开发者分享 | 如何在Vitis中把设置信息传递到底层的Vivado (上)

judy 在 周四, 07/22/2021 - 14:42 提交

在Vitis完成这个过程的底层,实际调用的是Vivado。Vitis会指定默认的Vivado策略来执行综合和实现的步骤。当默认的Vivado策略无法达到预期的时序要求时,我们需要在Vivado中分析时序问题的原因, 并根据时序失败的原因调整Vivado各个步骤的选项。有时我们也需要调整Vivado各个步骤的选项做不同方向的优化。

在Vitis完成这个过程的底层,实际调用的是Vivado。Vitis会指定默认的Vivado策略来执行综合和实现的步骤。当默认的Vivado策略无法达到预期的时序要求时,我们需要在Vivado中分析时序问题的原因, 并根据时序失败的原因调整Vivado各个步骤的选项。有时我们也需要调整Vivado各个步骤的选项做不同方向的优化。

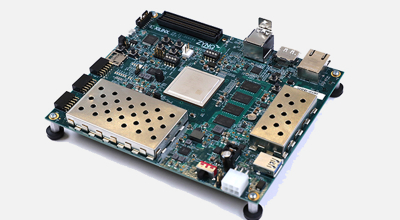

Vitis + ZCU104案例教程分享

本文描述了如何使用 XMPU、XPPU 和 TrustZone 提供的硬件和软件机制进行子系统的隔离。

了解如何将动态区域放置在动态区域内,以扩展 Dynamic Function eXchange 设计的灵活性和效率。

使用 Alveo U30 软件开发者套件 (SDK) 在一天内启动开发。观看视频,快速上手。

Kintex UltraScale+ 拥有的高速 SerDes,大大简化了 PCB 设计、节约了 PCB 面积;其片内集成大量 Block RAM、UltraRAM,替代了传统方案中的多片外挂 QDR SRAM,从而大幅节省 IO 资源和 PCB 面积。Kintex 器件所拥有的高速处理时钟和丰富的 DSP 资源,满足了数字示波器宽带实时数字信号处理,复杂滤波,高速 FFT 需求。

“软硬兼长”是京信与赛灵思合作的基础,也是更好赋能 Open RAN 的一大关键。自2007年初以来,京信随即开始采用赛灵思芯片及解决方案,并随其演进步伐持续开发高质量无线电产品及系统。赛灵思 Artix 7 系列 FPGA 广泛用于京信 2G/3G/4G 传统产品线。伴随 5G 时代的到来,赛灵思 Zynq 7000 SoC、MPSoC、Kintex 系列已广泛应用于京信新一代高效无线产品。

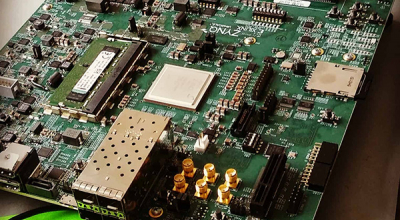

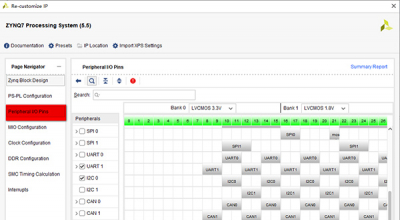

在使用ZYNQ进行开发设计时,往往需要对一些GPIO引脚进行配置,传统的配置方法通常在PL端进行管脚约束之后在Verilog代码中对相应引脚进行配置。这样如果开发过程中一旦有需要对管脚配置进行修改的话,那么就必须重新进行综合、布局布线、生成比特流文件,如果设计工程相对复杂的话,完成整个过程通常需要相当长一段时间。影响开发效率。

DNN加速器的设计一直在两个方面使力:通用架构和高效性能。通用性需要自顶向下的设计,首先综合各种神经网络的算子设计一套标准的指令集,然后根据硬件平台的特点,考察计算资源,存储资源以及带宽,进行硬件的模块化设计,在指令集以及硬件的特殊结构基础上,再去构建工具链。

为专用硬件架构设计神经网络,是近年来的热门话题,特别是在边缘器件上。在本次演讲视频中,您将了解如何借助 Once-for-All 神经网络,以低成本形式为 Xilinx 普及型 AI 平台 Vitis AI 搜索和部署高效率模型。