简化超高速数字系统中确定性延迟的设计

judy 在 周二, 07/06/2021 - 11:19 提交

实现确定性延迟是当今许多系统设计中讨论的主题。过去,人们一直在努力提高数据传输速度和带宽。如今的应用则越来越重视确定性——即要求数据包在精确的、可重复的时间点传送。本文将在设备的层面讨论确定性这一主题,以及如何设计超高速数据转换和信号处理系统以保证确定性延迟。

实现确定性延迟是当今许多系统设计中讨论的主题。过去,人们一直在努力提高数据传输速度和带宽。如今的应用则越来越重视确定性——即要求数据包在精确的、可重复的时间点传送。本文将在设备的层面讨论确定性这一主题,以及如何设计超高速数据转换和信号处理系统以保证确定性延迟。

本文描述将隔离设计流程 (IDF) 和动态函数交换 (DFX) 组合到一个设计中。

在 Vivado 2021.1 中,Control, Interfaces and Processing System (CIPS) IP 架构已重新设计。此次升级支持将来自其它 Versal 系列的器件集成到 CIPS IP 内。

VERSALDEMO1Z 是一个和 Xilinx 联合开发的电源参考板,它为 Xilinx Versal ACAP 平台提供完整的电源轨,ACAP 平台包括自适应引擎、人工智能引擎和标量引擎,以及外部的 DDR 存储器。这款参考板已经开放订购,它既可以作为成熟的整套参考设计,帮助客户抢占设计先机,也可以作为评估平台,快速方便地进行电源测试。

本该演示视频介绍了 Zynq® RFSoC DFE,这是一种适用于大规模 5G 部署的自适应无线电平台。

随着人工智能(AI)应用的高速发展,视觉AI成了各家技术公司逐鹿的主战场。基于机器学习,网络边缘的视觉AI设备可以根据AI推理,完成物体探测、人脸识别、图像分析等多种智能视觉任务,为用户带来全新的体验。

随着FPGA的不断发展,FPGA本身自带的PCIE硬核的数量越来越多,本文以ZU11EG为例介绍,如何进行对应的硬件引脚分配。

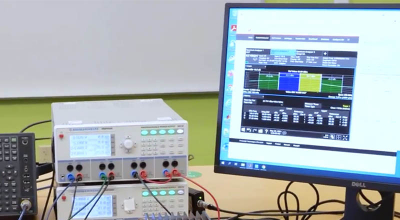

该演示展示了 Xilinx DPD v11 如何管理 GaN PA 的长期存储存应。该演示使用 Wolfspeed 的 39dBm GaN PA,展示了长期存储存应如何影响光谱发射掩模 (SEM) 和误差矢量幅度 (EVM)。看看 DPD v11 全新长期存储管理功能如何纠正这些不足。

“重构”对于刚接触FPGA的人来说,可谓十分神秘,对于已经入门的人来说很“简单”,但是你真的了解FPGA的重构吗?

在本文中,我们将提供一种高效方法,用于完成数据的交互、组织以及最终变换(预处理)。随后,我们将讲解如何在训练过程中正确地把数据输入给模型。PyTorch 框架将帮助我们实现此目标,我们还将从头开始编写几个类。PyTorch 可提供更完整的原生类,但创建我们自己的类可帮助我们加速学习。