【Vitis指南】Xilinx Vitis 系列(五)

judy 在 周一, 04/19/2021 - 09:51 提交

今天带来第五篇,介绍建立系统和Vitis IDE调试流程。

今天带来第五篇,介绍建立系统和Vitis IDE调试流程。

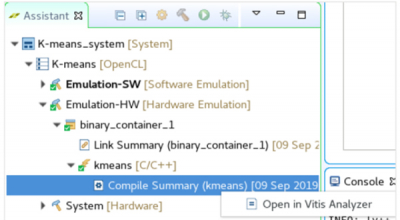

关键路径通常是指同步逻辑电路中,组合逻辑时延最大的路径(这里我认为还需要加上布线的延迟),也就是说关键路径是对设计性能起决定性影响的时序路径。对关键路径进行时序优化,可以直接提高设计性能。对同步逻辑来说,常用的时序优化方法包括Pipeline、Retiming、逻辑复制、加法/乘法树、关键信号后移、消除优先级等解决。

DeepField-SR 是一款功能固定的硬件加速器,该方案采用赛灵思 Alveo 加速卡和 AWS F1云平台,为视频超分辨率增强提供最高计算效率。DeepField-SR 以使用互联网真实视频数据进行训练的专有神经网络为基础,在多帧中融合空间-时间信息,能生成超高分辨率的视频质量。

AI 软件创新者Mipsology今天宣布与FPGA服务培训、设计和技术服务供应商E-Elements达成设计合作伙伴关系。E-Elements将Xilinx solutions与Mipsology公司的Zebra AI 推理加速器结合在一起,为亚洲医疗、机器人和自动交通行业设计产品与服务。

今天带来第四篇,介绍使用Vitis IDE,包括Vitis命令选项和创建Vitis IDE项目。Vitis命令将使用您定义的选项启动Vitis IDE。它提供用于指定工作区的选项以及项目的选项。以下各节描述了Vitis命令的选项。

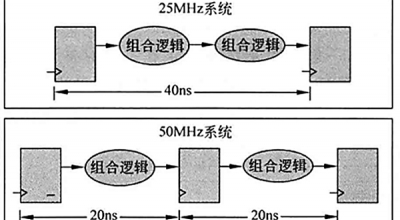

单口 RAM(Single RAM)、双口 RAM(Dual RAM)、简单双口 RAM(Simple-Dual RAM)、真双口 RAM(True-Dual RAM)有什么不同?对于 分布式 RAM,支持简单双口 RAM 和双口 RAM,不能配置成真双口 RAM。

本示例工程中我们会在 TensorFlow2 下使用 Keras API 创建一个自定义 CNN 网络,在 Vitis-AI 1.3 环境下编译成 Xilinx DPU 上运行的模型文件,并在 Xilinx zynqMP 上部署运行。该示例工程应在 Vitis-AI1.3 Docker,vitis-ai-tensorflow2conda 环境中运行。

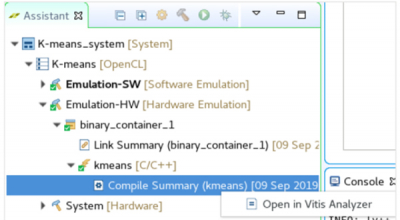

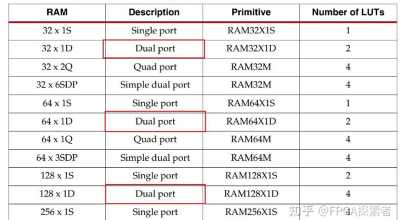

今天带来第三篇,介绍使用Vitis分析仪。Vitis分析仪是一种实用工具,允许查看和分析,同时建立并运行应用程序生成的报告。旨在查看由构建应用程序时的Vitis编译器和运行应用程序时的Xilinx®Runtime(XRT)库生成的报告。

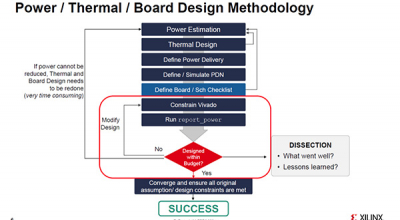

4月23日,Xilinx Adapt China:Vivado专场的第二天,赛灵思 Vivado专家团将带来连续三场的“设计收敛”技巧分享。从如何提高QoR(结果质量)的方法技巧、解决接受的时序问题工具,到功耗约束的最佳实践,诚意满满,技术干货一应俱全。

本文描述在Vivado®工具中使用Xilinx®设计约束(XDC)。XDC结合了行业标准的Synopsys设计约束(SDC)和Xilinx专有约束。创建XDC来定义时钟,I / O延迟和时序异常(如错误和多周期路径以及最小/最大延迟)的详细信息。