Xilinx源语-------FDRE

judy 在 周五, 11/27/2020 - 15:54 提交

FDRE代表一个单D型触发器,含的有五个信号分别为: 数据(data,D)、时钟使能(Clock enable,CE)、时钟(Clock)、同步复位(synchronous reset,R)、数据输出(dataout,Q)。当输入的同步复位信号为高时,否决(override)所有输入,并在时钟的上升沿将输出Q为低信号。

FDRE代表一个单D型触发器,含的有五个信号分别为: 数据(data,D)、时钟使能(Clock enable,CE)、时钟(Clock)、同步复位(synchronous reset,R)、数据输出(dataout,Q)。当输入的同步复位信号为高时,否决(override)所有输入,并在时钟的上升沿将输出Q为低信号。

在调试模式下,Xil_Assert系列宏会调用Xil_Assert来检查参数是否正常。如果不正常,缺省情况下,没有打印,会进入死循环。通过调用void Xil_AssertSetCallback(Xil_AssertCallback Routine), 设置回调函数, 可以自己处理失败情况,比如增加打印。

本视频为大家详细介绍了 Vitis 加速库,讲解库的构成和分类,以及如何在 Vitis 开发环境及 Xilinx 硬件平台上分层应用最适合的 Vitis 加速库。我们还会以 Alveo U50 加速卡为例,选取 Vitis 加速库中的一个压缩算法 Zlib 为例,详细介绍算法的构成、性能,并实例展示如何在 U50 板卡上实现 Vitis Zlib 算法库。

由于Verilog/Vhdl没有计算exp指数函数的库函数,所以在开发过程中可利用cordic IP核做exp函数即e^x值;但前提要保证输入范围在(-pi/4—pi/4)。在cordic核中e^x = sinh + cosh所以在配置cordic时点选sinh and cosh即可 如下图

lspci 命令和 setpci 命令均为 Linux 发行版中原生可用的命令。这 2 条命令均可提供多级输出,适合在不同时间点用于查看 PCI 总线上训练的不同组件的功能和状态。其中大部分功能均可反映《PCI Express 基本规范》中所需的配置空间寄存器。

亲爱的开发者朋友,首先感谢您对首届赛灵思全球自适应计算挑战赛的信任与支持!为了帮助大家顺利完成提交,我们在这里再次为大家明确相关要求和提交指引。

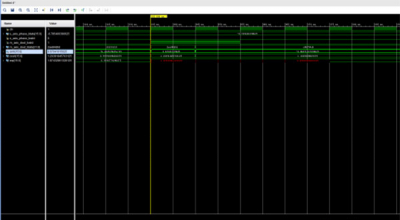

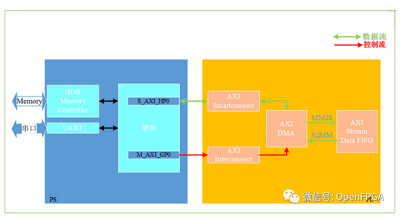

增加一个AXIDMA章节,这部分内容是很多例程的基础,难度不大但是也不小,需要彻底理解整个运行机制。

在VCU TRD 2019.1的Linux里,使用devemem读写内存,得到错误“devmem: mmap: Operation not permitted”。

过去三十年间,基于服务器的计算历经多次飞跃式发展。上世纪 90 年代,业界从单插槽独立服务器发展到服务器集群。紧接着在千禧年,产业首次看到双插槽服务器,再后来,多核处理器也问世了。进入下一个十年,GPU 的用途远远超出了处理图形的范畴,我们见证了基于 FPGA 的加速器卡的兴起。

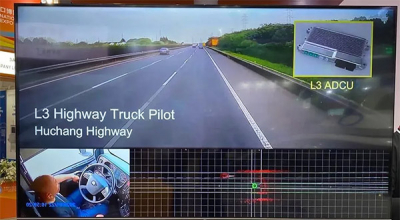

自动驾驶技术是汽车产业与高性能计算芯片、人工智能、物联网等新一代信息技术深度结合的产物,也是未来汽车行业发展的“大势所趋”。成立于 2018 年的宏景智驾便是这个赛道的探险者之一,其软硬一体自动驾驶计算平台是目前中国市场上少有支持高阶自动驾驶的通用型平台解决方案。