EV 马达控制系统演示

judy 在 周五, 01/22/2021 - 09:49 提交

SiC(碳化硅)具有减轻重量和驱动 EV 马达的功能,因此在电动汽车 (EV) 马达的发展中对碳化硅的需求越来越大。安森美的通用控制器板 (UCB) 解决方案包含灵活应变的 Zynq®-7000 SoC,可确保决定性的快速控制环路能够充分利用 SiC 的高开关频率。在自适应 Zynq-7000 SoC 的专用可编程逻辑中,可实现对高速马达的精确控制,展现高性能和高效率。

SiC(碳化硅)具有减轻重量和驱动 EV 马达的功能,因此在电动汽车 (EV) 马达的发展中对碳化硅的需求越来越大。安森美的通用控制器板 (UCB) 解决方案包含灵活应变的 Zynq®-7000 SoC,可确保决定性的快速控制环路能够充分利用 SiC 的高开关频率。在自适应 Zynq-7000 SoC 的专用可编程逻辑中,可实现对高速马达的精确控制,展现高性能和高效率。

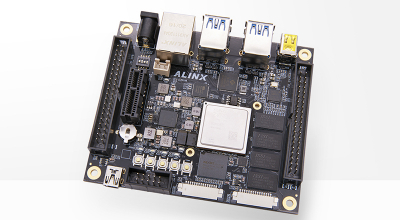

启动人工智能应用从来没有像现在这样容易!受益于像Xilinx Zynq UltraScale+ MPSoC 这样的FPGA,AI现在也可以离线使用或在边缘部署、使用。瑞苏盈科核心板模块结合Vitis AI开发工具给用户提供了便利工具,可用于开发和部署用于实时推理的机器学习应用

本文描述了如何使用Quad SPI和SD模式安全地启动Zynq®-7000 SoC,包括最佳使用RSA认证和AES加密。

Xilinx_A7_K7_V7系列Cadence符号库及PCB库,包含的型号有XC7A100T-1FGG484I;XC7A200T-1FBG676I;XC7K325T-2FFG900I;XC7K410T-2FFG900I;XC7VX690T-2FFG1927I。原理图符号按照BANK建立,很规范。

实时时钟(rtc)单元为系统和应用软件提供精确的时间基准。为了满足高精度的需要,实时时钟还包括校准电路,以补偿温度和电压波动。RTC 由 VCC-PSAUX 或 VCC-PSBATT 电源供电。当辅助电源可用时,RTC 使用它保持计数器活动。当辅助电源不可用时,RTC 自动切换到 VCC PSBATT 电源。

本视频展示Vitis系统集成的实例演示。介绍使用Vitis统一软件平台创建并集成RTL模块以及HLS内核的简单步骤。

2020 年,5G 商用进入新阶段,“5G+”科技开始融入百行百业。灵活应变的能力、开放的标准、 AI 和机器学习正持续推动 5G 网络演进发展。从 2021 年开始,随着新技术方法融入虚拟化分布式和中央单元,运营商有望更好地把控整体解决方案,从而以新服务加快 5G 商业化步伐

日前,赛灵思宣布两款 Versal™ ACAP 评估套件现已上市,分别为 Versal AI Core 系列 VCK190 评估套件和 Versal Prime系列 VMK180 评估套件。VCK190 和 VMK180 评估套件拥有相同的附件集,并且具有相似的板载接口。

前不久,赛灵思联手 Hackster.io 举办首届赛灵思自适应计算挑战赛,号召独立开发者利用 Vitis 统一软件平台和 Vitis AI 在选定的赛灵思硬件平台上开发新应用,以创新方法解决现实问题。在来自全球的 70 多个独创项目中,评委为每个类别甄选出三个冠军项目,分别获得高达 10,000 美元的奖金奖励。

此文基于第十八章内容进行软件开发