【视频】集成 RS-FEC 的 16nm UltraScale+ FPGA

judy 在 周五, 01/18/2019 - 14:36 提交

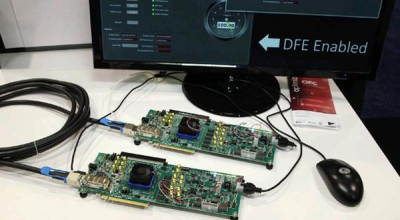

视频演示将展示 Xilinx 16nm Virtex UltraScale+ FPGA,其所集成的 100G 以太网 MAC 和 RS-FEC 能够串行工作,通过极具挑战的电子或光学互连发送数据。集成可节省逻辑区域,简化实现方案,并可降低日益普及的 100G 以太网接口或高速背板应用上的功耗

视频演示将展示 Xilinx 16nm Virtex UltraScale+ FPGA,其所集成的 100G 以太网 MAC 和 RS-FEC 能够串行工作,通过极具挑战的电子或光学互连发送数据。集成可节省逻辑区域,简化实现方案,并可降低日益普及的 100G 以太网接口或高速背板应用上的功耗

Zynq7000 系列芯片有 54 个 MIO(multiuse I/O), 它们分配在 GPIO 的 Bank0 和Bank1 隶属于 PS 部分, 这些 IO 与 PS 直接相连。 不需要添加引脚约束, MIO 信号对 PL部分是透明的。 所以对 MIO 的操作可以看作是纯PS 的操作

本文主要介绍Xilinx FPGA的配置模式,主要包括Master/Slave模式,Serial/SelectMAP模式,JTAG模式等。其中7系列只有Logic部分,其配置相关功能引脚全部连接到FPGA端的特定bank上;Zynq 7000系列既有PL部分,也有PS部分,其JTAG从PL侧引出,其余配置相关引脚全部从PS侧引出

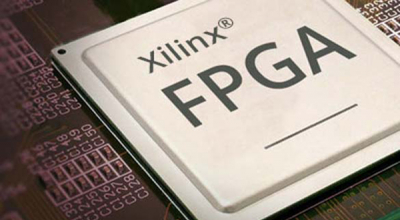

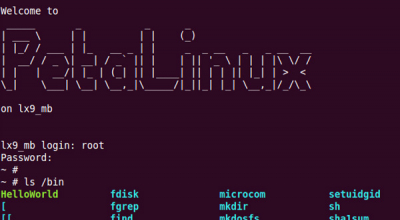

在本次研讨会中,赛灵思专家将向您介绍赛灵思MicroBlaze 处理器将如何让启动新设计变得前所未有地简单快捷!无需 RTL 经验就能使用 Vivado IP 集成器工具以及第三方 IP 库。专家将为您演示如何使用外围设备在几分钟之内快速打造任何嵌入式设计原型

可靠的通用通信是工业物联网 (IIoT) 的基础。低时延、高带宽、恢复力、可扩展性及符合标准是关键。自动化现已跨越 40 多个协议,可满足众多目标应用的特定需求。可编程逻辑为您的产品匹配所有客户网络带来的灵活性是无与伦比的

深度学习软硬一体化加速方案,具备模型剪枝&量化加速工具,能将原始模型性能提升 4 倍以上。高性能的加速引擎提供 2.4Tops 的强大 AI 算力,完整的嵌入式参考设计,便于硬件产品的结构设计及二次开发。AI 硬件产品通过集成 EdgeBoard,可大大提升终端设备 AI 推理能力。

EdgeBoard 是百度打造的基于赛灵思技术的从订制化需求到终端计算加速的一站式解决方案,支持企业轻松开发出高性能的 AI 硬件。开发者可以直接采用百度已经完全配置好的方案马上上手,也可以作为百度大脑 AI 硬件平台计划的一部分进行配置和定制

ug948中提供的官方例程为图像的中值滤波,该设计将一副256*256大小的RGB图像,添加噪声后提取出其中的Y通道,使用C++语言完成中值滤波。该设计将在Simulink环境下进行仿真。本次设计的流程是利用Vivado HLS建立C/C++代码,Export RTL–>System Generator–>Vivado

由于汽车科技在CES扮演的角色越来越重要,赛灵思在整周的活动中也成为目光焦点。在今年的展会上,赛灵思与汽车业合作伙伴及客户共同发布了多项新闻, 分享赛灵思的技术合作技术支持人工智能 (AI) 加速、自动驾驶 (AD) 和高级驾驶辅助系统 (ADAS)

先去官网下载一个对应的bsp包,如果没有,可以自定义工程,自己建自己的项目,在开始阶段,先用bsp熟悉一下开发流程: