借助vivado来学习FPGA配置模式

judy 在 周一, 11/12/2018 - 09:40 提交

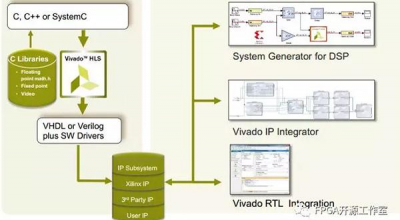

DA(Vivado)软件可以很好的帮助我们更好的去学习FPGA相关知识,例如:

DA(Vivado)软件可以很好的帮助我们更好的去学习FPGA相关知识,例如:

赛灵思公司全球总裁兼 CEO Victor Peng 荣膺2018 年年度创新人物奖。 图一为Aspencore 亚太区负责人张毓波 (Yorbe) 先生为Victor 颁发奖杯

赛灵思 Zynq UltraScale+ RFSoC 荣膺处理器/DSP/FPGA 类最佳产品奖

作者:Matt Chevrier,德州仪器

为工业以太网器件供电需要解决工业以太网和工业应用的几个特定问题。

标准以太网与工业以太网之间最大的区别在于拓扑结构,如图1所示。标准以太网为星形拓扑,而工业以太网则包含线形、树形和环形等多种不同的拓扑结构。

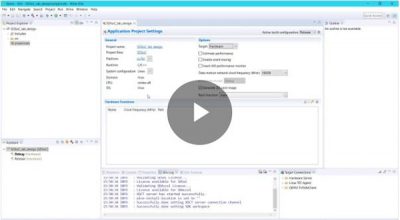

详解 SDSoC 集成式开发环境 (IDE) 的完整开发流程。

作者:Huster-ty

前言:

ZYNQ 7000有三种GPIO:MIO,EMIO,AXI_GPIO

MIO是固定管脚的,属于PS,使用时不消耗PL资源;EMIO通过PL扩展,使用时需要分配管脚,使用时消耗PL管脚资源;AXI_GPIO是封装好的IP核,PS通过M_AXI_GPIO接口控制PL部分实现IO,使用时消耗管脚资源和逻辑资源。

为了快速实现算法板级验证,PC端需要通过JTAG或以太网与FPGA形成通路。最简单便捷的方案是利用协议栈芯片,用户可以无视底层,利用简单的SPI协议读写寄存器实现复杂的TCP UDP等网络协议。当然带宽会受限于SPI接口有效速率,本文采用芯片为W5500,支持10M/100M自适应,其理论值高达80Mbps,基本达到算法验证的要求。

作者: OpenSLee,来源:FPGA开源工作室

1. 背景知识

在Xilinx提供的很多ip如VDMA ,OSD,Mixer,TPG等等,在使用前都需要进行配置,配置接口往往是AXI-Lite接口,正常情况下我们一般自己编写配置逻辑或者通过MB/ZYNQ等对IP进行配置,如果在我们使用到XDMA的同时也使用到需要AXI-Lite配置的ip的话,那么有一种新的方法可以对这类型IP进行配置。

2018年10月23日 - Silexica发布了多核软件开发工具SLX的最新版本,新版的FPGA和C/C++功能得到大幅增强。SLX工具是目前业界首款用于FPGA的工具,该软件全面支持Xilinx的SDSoC开发环境,在进入高阶综合(High-Level Synthesis,HLS)之前即可进行软硬件开发探索,保证HLS的进行过程更加精确高效。