本文是该系列的第4篇,第2篇以数字滤波器的设计为主题,介绍了System Generator的完整设计流程;第3篇介绍了 System Generator导出设计的说明文档和testbench的特性。本文将介绍System Generator对设计进行资源分析和时序分析的相关方法。

查看分析结果

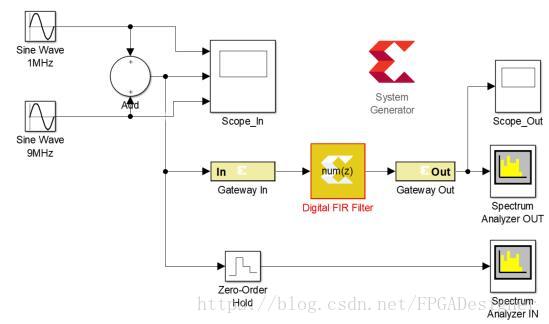

本文在第2篇设计的数字滤波器模型基础上运行分析。System Generator集成了时序分析和资源分析功能,以确保在simulink中设计的DSP系统导出到FPGA环境中能够正确运行。其本质上仍然是在后台调用Vivado进行分析,System Generator只是读取了分析结果并显示出来。

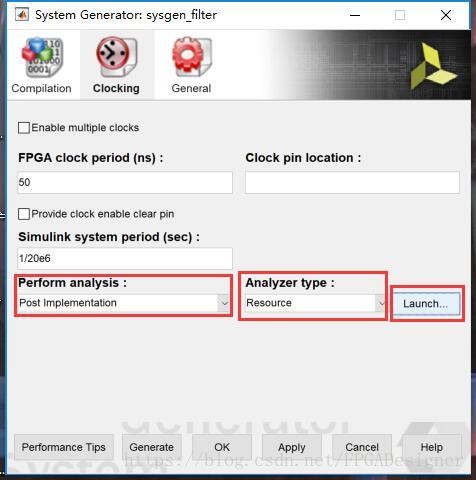

设计完成并且Simulink运行完毕后,打开System Generator这个block,切换到Clock标签下:

Perform analysis中可以设置:

• None:不进行分析;

• Post Synthesis:综合后进行分析;

• Post Implementation:实现后进行分析。

Analyzer type中可以设置“Resource”(进行资源分析)或“Timing”(进行时序分析)。注意在Perform analysis设置好,并且导出设计到FPGA后,可以切换Analyzer type,并且点击右边的“Launch”查看两种报告。但修改设计和修改Perform analysis参数后必须重新运行才能生成最新的报告。

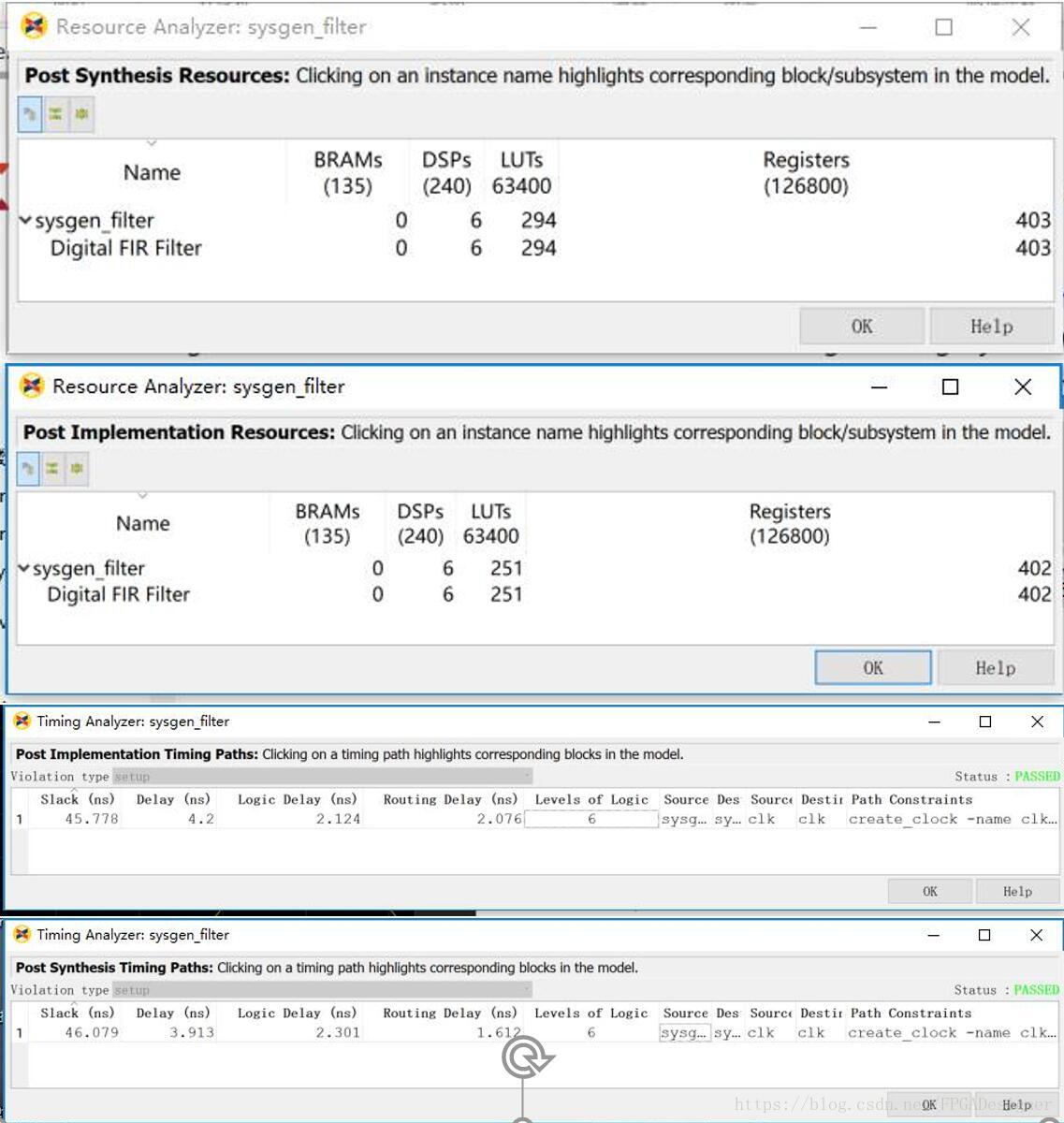

综合后和实现后的资源分析和时序分析分别如下。时序报告中可以看到每一条时钟路径的情况(本设计中只有一条);资源报告中可以看到每一个模块的资源消耗(本设计只有一个模块)。可以看到综合后与实现后的资源消耗情况、时序情况有些差异:

时序分析

System Generator集成的静态时序分析功能提供了如下特性:

• 点击每一列的指标名称,可以选择升序/降序排列;

• 时序不满足时,相应的路径Slack值为负数,且显示为红色;

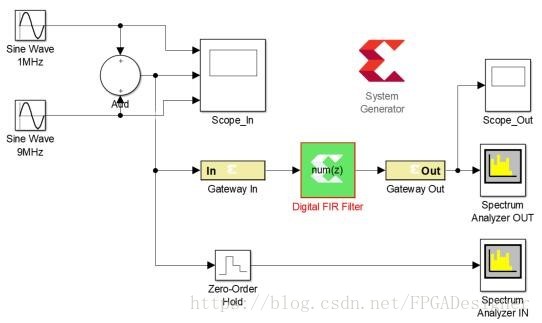

• 交叉定位功能:时序报告中选中某一路径,Simulink模型中对应的部分会高亮显示(时序满足为绿色;不满足为红色),这可以帮助设计者更快的找到和修改时序错误,如下图:

• 时序不满足时,可以考虑修改设计(如增加一些单元的Latency,以资源换速度),或者更换综合策略/实现策略。

在System Generator block的Compilation标签下可以设置“Synthesis strategy”和“Implementation strategy”。列表中有几种Vivado提供的策略,也可以在Vivado中添加好用户自定义的策略,在System Generator中调用。

资源分析

System Generator集成的资源分析功能提供了如下特性:

• 点击每一列的指标名称,可以选择升序/降序排列;

• BRAMs(包括RAMB36E、FIFO36E、RAMB18E、FIFO18E0资源);DSPs(包括DSP48E、DSP48E1、DSP48E2资源);Registers(包括寄存器和触发器,以FD和LD开头的资源);LUTs(所有的查找表);

• 交叉定位功能:资源报告中选中某一模块,Simulink模型中对应的部分会高亮显示(黄色),如下图:

资源消耗超过FPGA芯片总资源时,可以考虑修改设计,或者更换综合策略/实现策略。这里与时序分析部分相同。

时序/资源分析失败的说明

绝大多数情况下,时序分析和资源分析都能得到正确的结果,但有时在Generate生成结束后,会提示一个Error,无法获取结果数据。

失败的原因一般都是如下情况:在同一目录下有多个slx文件,但是所有的slx文件设置的输出目录都相同(比如都是默认的./netlist)。在导出第一个slx文件时是可以正确运行时序/资源分析的;但在导出第二个slx文件的设计时,就会报错。原因便是不同的模型向同一目录下导出设计。在设置路径时要注意。

文章来源:FPGADesigner的博客

*本文由作者授权转发,如需转载请联系作者本人