版权声明:本文为博主原创文章,遵循 CC 4.0 by-sa 版权协议,转载请附上原文出处链接和本声明。

本文链接:https://blog.csdn.net/qq_37512669/article/details/90139723

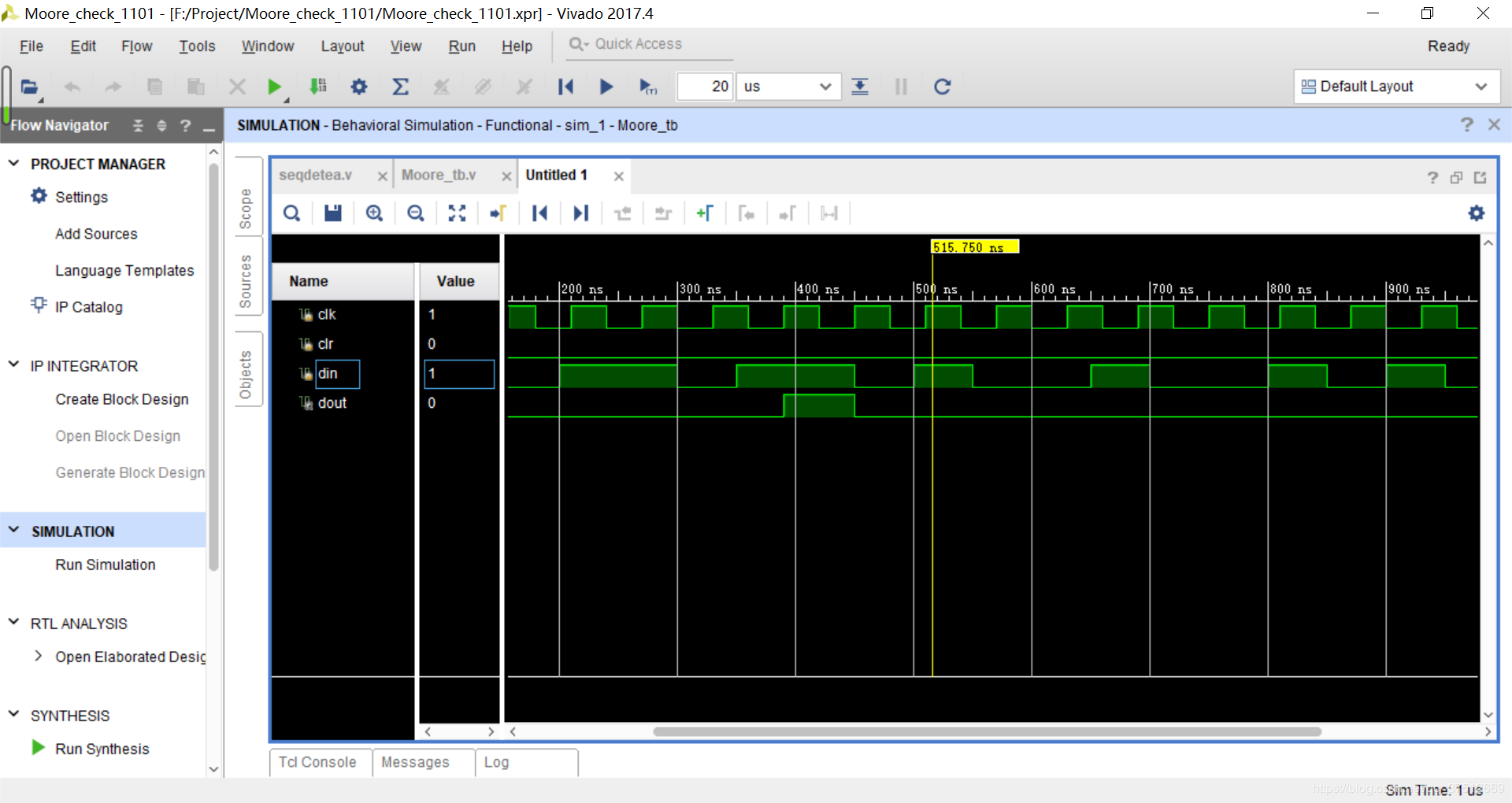

软件:Vivado2017.4 板卡:Ego1 型号:xc7a35tcsg324-1

四、有限状态机

Moore状态机

只与当前状态有关而与输入无关

`timescale 1ns / 1ps

module seqdetea(

input wire clk,

input wire clr,

input wire din,

output reg dout

);

reg[2:0]present_state,next_state;

parameter S0=3'b000,S1=3'b001,S2=3'b010,S3=3'b011,S4=3'b100;

//状态寄存器

always@(posedge clk or posedge clr)

begin

if(clr == 1)

present_state <=S0;

else

present_state <=next_state;

end

//C1模块

always@(*)

begin

case(present_state)

S0:if(din == 1)

next_state <= S1;

else

next_state <= S0;

S1:if(din == 1)

next_state <= S2;

else

next_state <= S0;

S2:if(din == 1)

next_state <= S2;

else

next_state <= S3;

S3:if(din == 1)

next_state <= S4;

else

next_state <= S0;

S4:if(din == 1)

next_state <= S2;

else

next_state <= S0;

default: next_state <= S0;

endcase

end

//C2模块

always@(*)

begin

if(present_state == S4)

dout =1;

else

dout = 0;

end

endmodule

书写:Test_beach

`timescale 1ns / 1ps

module Moore_tb();

reg clk,clr;

reg din;

wire dout;

seqdetea u0(.clk(clk),.clr(clr),.din(din),.dout(dout));

initial begin

clk = 1'b0;

clr = 1'b0;

end

always

begin

#50 din = 1'b1;

#50 din = 1'b1;

#50 din = 1'b0;

#50 din = 1'b1;

#50 din = 1'b1;

#50 din = 1'b0;

#50 din = 1'b1;

#50 din = 1'b1;

#50 din = 1'b0;

#50 din = 1'b1;

#50 din = 1'b0;

#50 din = 1'b0;

#50 din = 1'b1;

#50 din = 1'b0;

#50 din = 1'b0;

#50 din = 1'b1;

#50 din = 1'b0;

#50 din = 1'b1;

#50 din = 1'b0;

end

always begin

clk = 1'b0;

#30 clk = 1'b1;

#30;

end

endmodule

仿真结果:

Mealy状态机

不仅和当前状态有关而且和输入状态也有关

`timescale 1ns / 1ps

module seqdetb(

input wire clk,

input wire clr,

input wire din,

output reg dout

);

reg[1:0]present_state,next_state;

parameter S0 = 3'b00,S1 = 3'b01,S2 = 3'b10,S3 = 3'b11;

//状态寄存器

always@(posedge clk or posedge clr)

begin

if(clr == 1)

present_state <= S0;

else

present_state <= next_state;

end

//C1 模块

always@(*)

begin

case(present_state)

S0:if(din == 1)

next_state <= S1;

else

next_state <= S0;

S1:if(din ==1)

next_state <=S2;

else

next_state <=S0;

S2:if(din == 0)

next_state <=S3;

else

next_state <=S0;

S3:if(din == 1)

next_state <= S1;

else

next_state <=S0;

default:next_state <=S0;

endcase

end

always@(posedge clk or posedge clr)

begin

if(clr == 1)

dout <=0;

else

if((present_state == S3)&&(din == 1))

dout <=1;

else

dout <=0;

end

endmodule

版权声明:本文为博主原创文章,遵循 CC 4.0 by-sa 版权协议,转载请附上原文出处链接和本声明。

本文链接:https://blog.csdn.net/qq_37512669/article/details/90139723