近期在研究AXI 1G/2.5G Ethernet IP核的Demo工程时,发现Xilinx对Clock的管理如分频,倍频等没有使用IP,而是直接调用了相关原语MMCME3_ADV,在这里MMCME3_ADV原语是针对UltraScale的器件的,7系列的器件相关原语名称为MMCME2_ADV。这个规则和LVDS的serdes等原语一致。

在梳理这个clock模块时,发现代码中对MMCME3_ADV这个原语配置的参数与想象中的不一致,但却能输出正确的时钟(仿真波形确认,时钟正确)。

时钟要求如下:

输入时钟300Mhz,输出5个时钟分别为300M,125M,100M,166M,50M

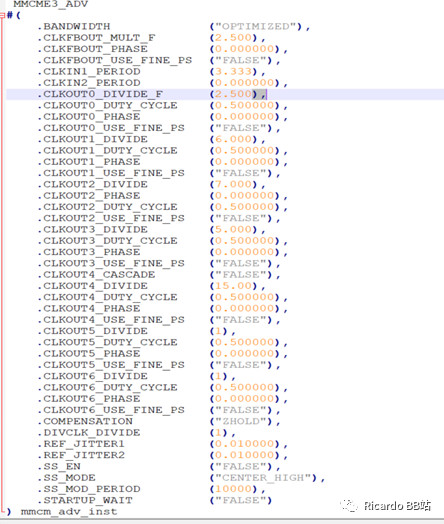

原语配置如下:

原先理解中的参数配置:

对于CLKOUT0来说,应该输出的为300M,按照倍数关系.CLKOUT0_DIVIDE_F (1.00 ) // 300/300

对于CLKOUT1来说,应该输出的为125M,按照倍数关系.CLKOUT1_DIVIDE_F (2.40 ) // 300/125

对于CLKOUT2来说,应该输出的为100M,按照倍数关系.CLKOUT2_DIVIDE (3 ) // 300/100

对于CLKOUT3来说,应该输出的为166M,按照倍数关系.CLKOUT3_DIVIDE_F (1.81 ) // 300/166

对于CLKOUT4来说,应该输出的为50M,按照倍数关系.CLKOUT4_DIVIDE (6 ) // 300/50

而且这样配置,通过换算得到的时钟频率也是和输出时钟的频率一致,因此觉得该模块代码有误,但通过仿真发现输出的所有时钟都是正确的!!!故可以确定是理解有问题,在仔细查阅文档后发现,MMCM对输入的时钟一般会通过先倍频在分频的方式产生输出时钟,故此在参数配置时需要考虑到倍频的系数。从上述原语配置中可以看出,输入时钟先通过了一个系数为2.5的倍频,因此输出时钟的配置计算应该如下:

输入300M,倍频系数2.5,倍频后时钟为750M

对于CLKOUT0来说,输出300M,按照倍数关系.CLKOUT0_DIVIDE_F (2.50) // 750/300

对于CLKOUT1来说,输出125M,按照倍数关系.CLKOUT1_DIVIDE (6) // 750/125

对于CLKOUT2来说,输出100M,按照倍数关系.CLKOUT2_DIVIDE (7) // 750/100

对于CLKOUT3来说,输出166M,按照倍数关系.CLKOUT3_DIVIDE (5) // 750/166

对于CLKOUT4来说,输出50M,按照倍数关系.CLKOUT3_DIVIDE (15) // 750/50

这就与上述代码中一致了!

最后总结:对于Xilinx的MMCM原语,在使用中要注意倍频系数,要先根据倍频系数来求分频系数。

本文转自:Ricardo BB站 - Ricardo.Wu ,转载此文目的在于传递更多信息,版权归原作者所有。