作者:华仔成龙

原文链接: https://blog.csdn.net/jinhua1990

声明:本文由原创博主授权转发,如需转载请联系博主

开发板:Ultra96

Xilinx Vivado:2018.2

SDK:2018.2

学习Ultra96,在http://zedboard.org/support/design/24166/156可以下载Ultra96的相关教程,入门教程有Tutorials 01 to 04。可以根据其来熟悉开发板。

Tutorial 1:Introduction

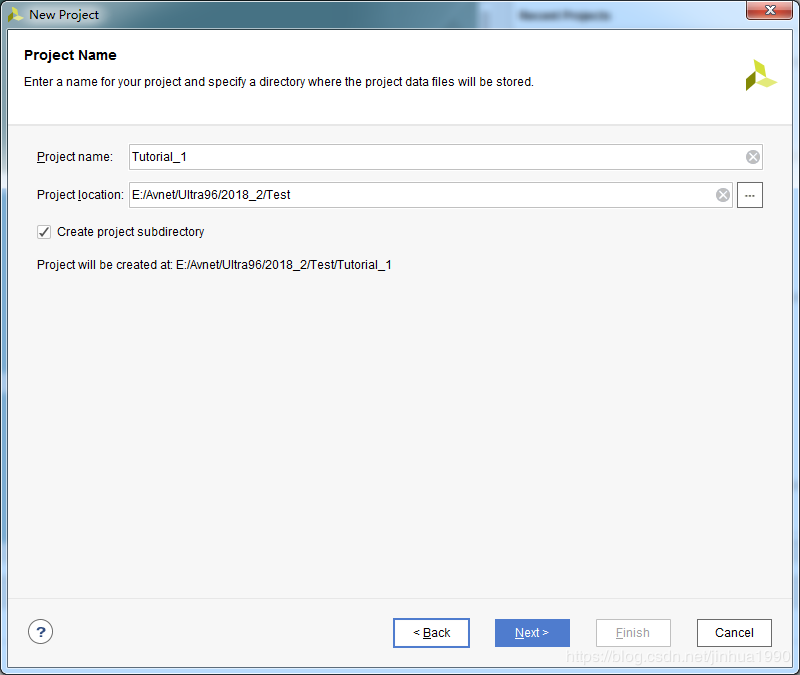

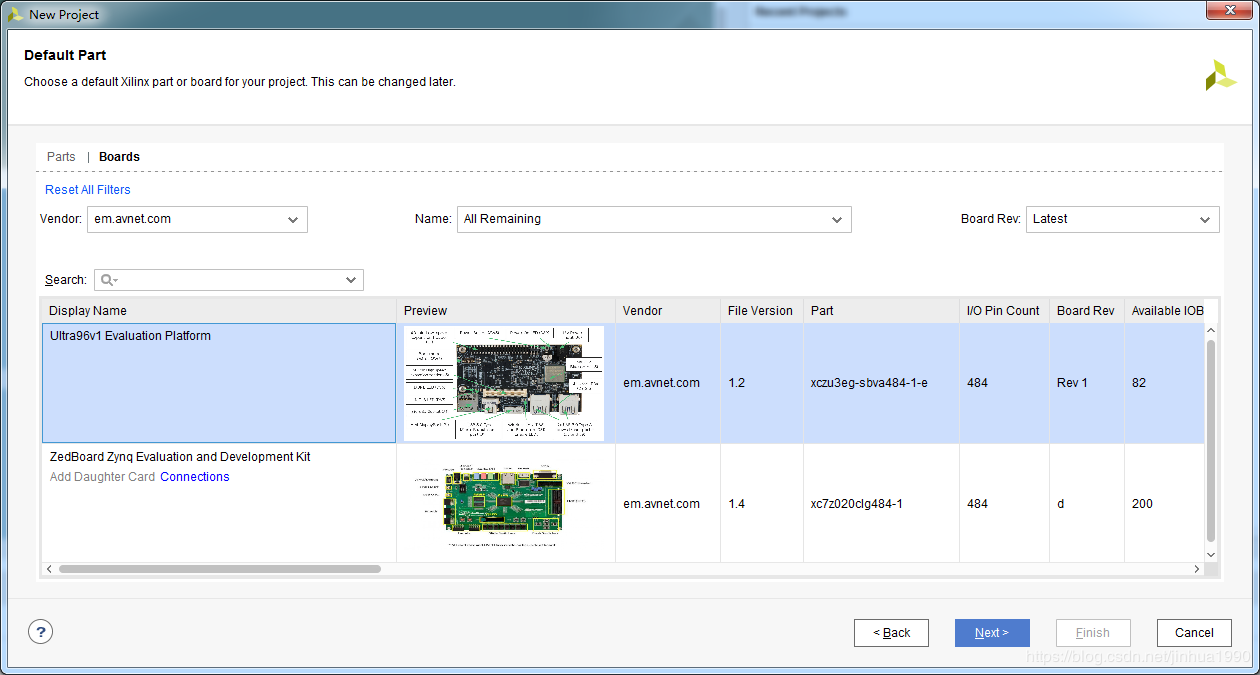

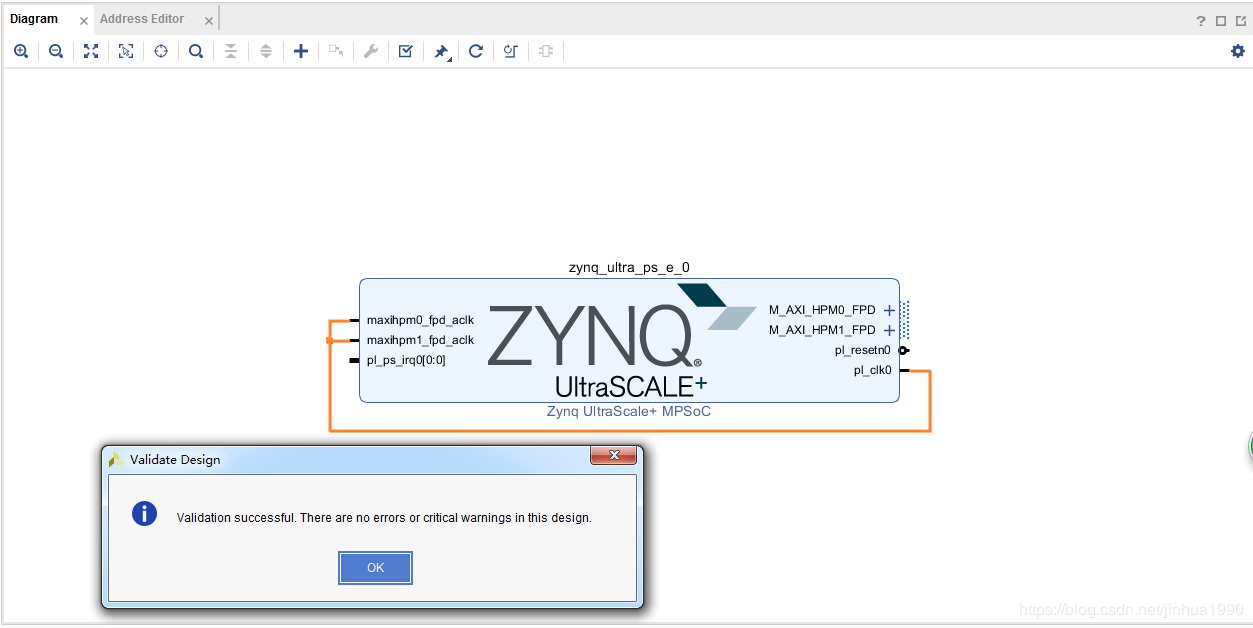

创建工程——>选择Ultra96开发板——>创建模块——>添加Zynq MP SoC——>Run Block Automation——>连接时钟、验证设计——>Generate Output Products——>Create HDL wrapper——>Generate Bitstream——>导出bitstream到SDK(File —Export —Export Hardware;Include bitstream)。

Tutorial 2:Hello World

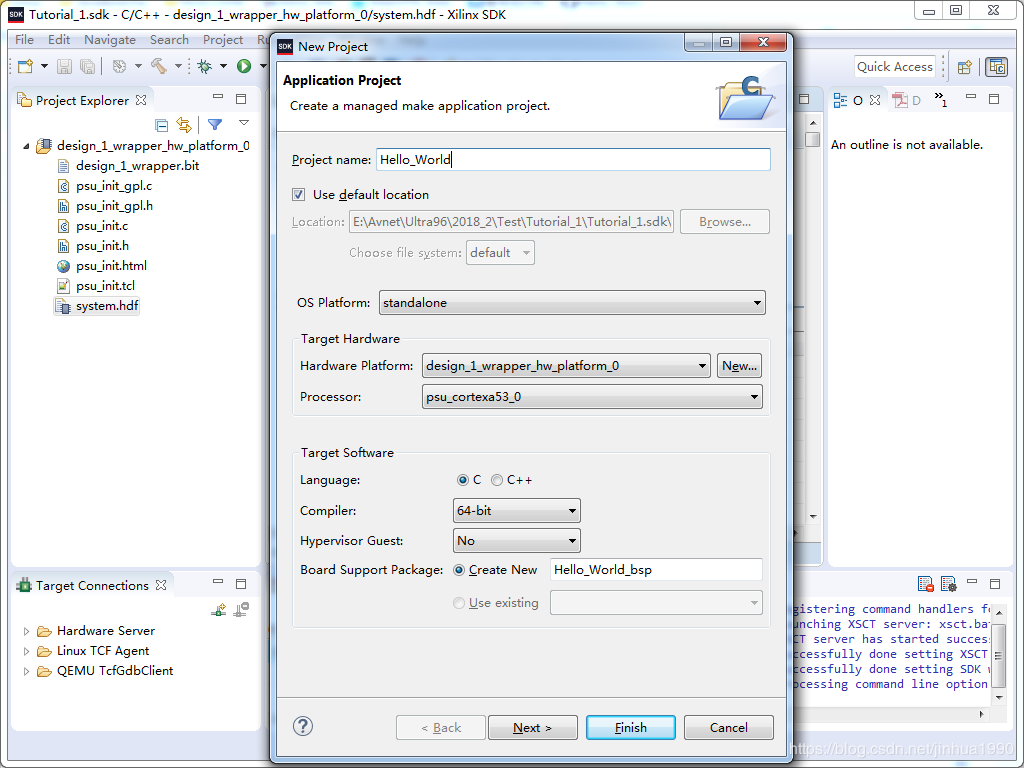

在Vivado中打开SDK(File—Launch SDK),创建新工程——>Hello World;

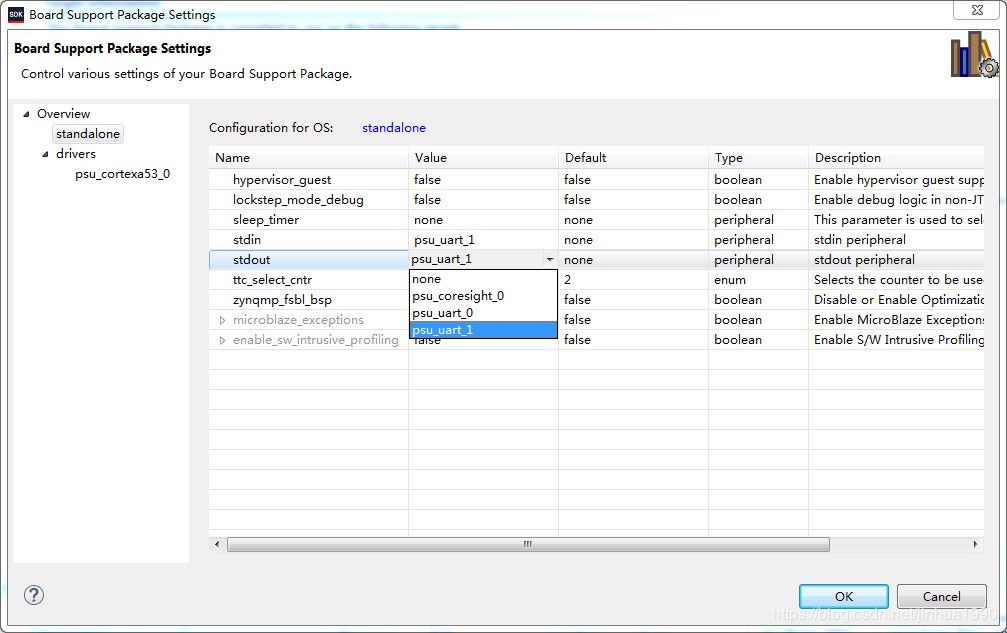

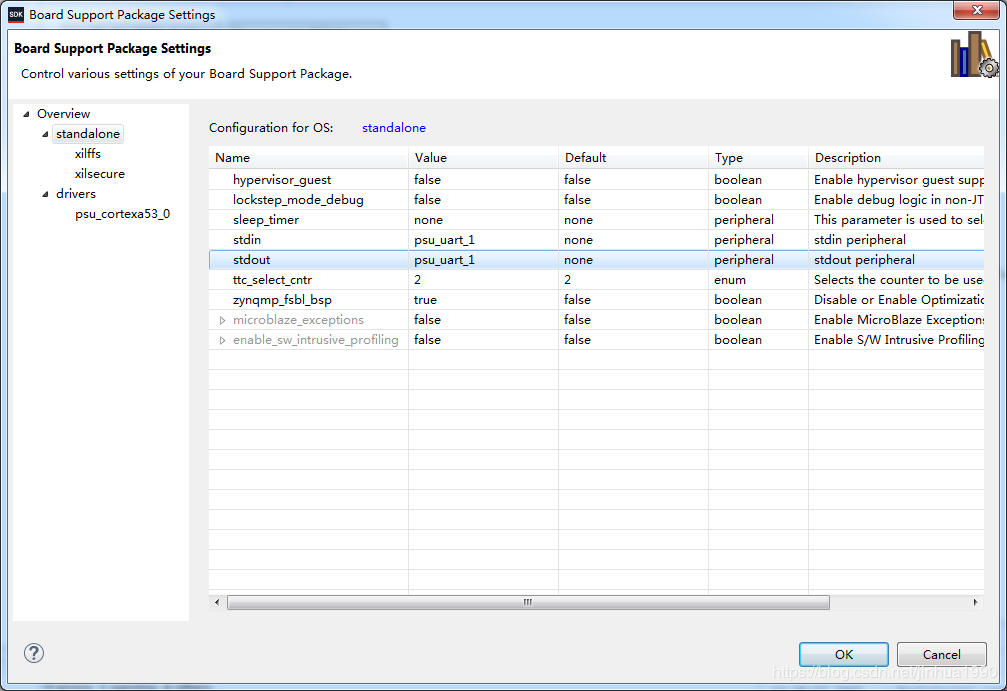

这里需要注意的是:Ultra96开发板用的UART1作为串口输入输出,需要修改BSP,在Project Explorer中右键Hello_World_bsp——>Board Support Package Settings——>standalone,stdin和stdout选择psu_uart_1。

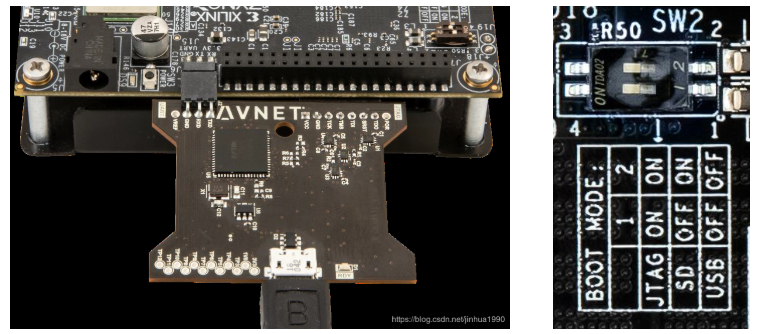

连接JTAG模块,设置拨码开关到JTAG启动,在SDK Terminal中配置串口波特率115200;

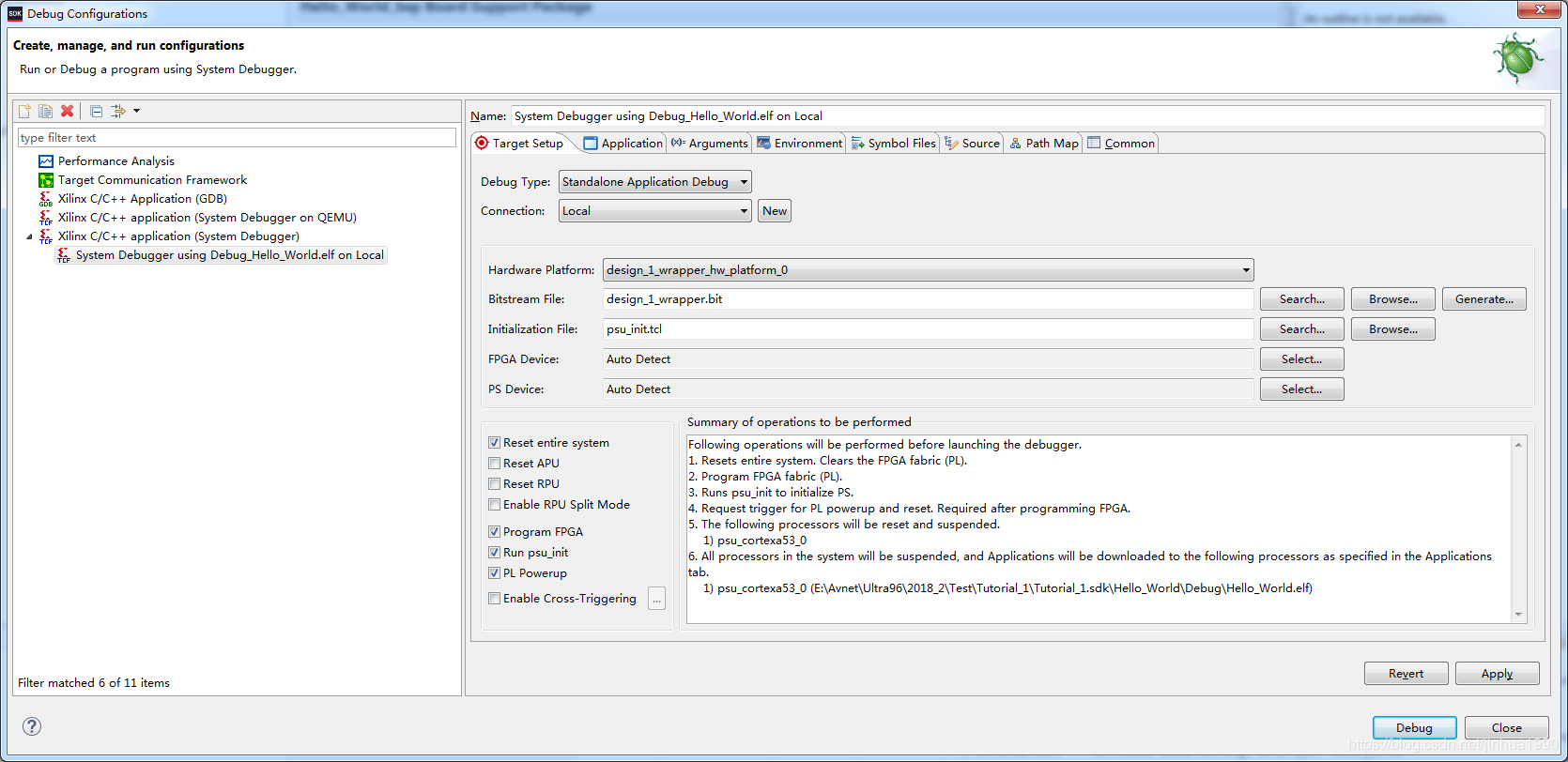

调试设置Debug Configurations——>System Debugger——>Reset entire system(会自动选上Program FPGA)——>Apply——>Debug。运行后即可在SDK Terminal中看到输出“Hello World”。

Tutorial 3:Test Application

同Tutorial 2创建的Hello World,Tutorial 3创建相关应用测试(Test App)——Memory Tests、Peripheral Tests、Zynq MP DRAM tests。

里面提到在SDK中显示代码行数,在这记录一下:Window——>Preferences dialog——> General——>Editors——>Text Editors——>选择Show line numbers即可。

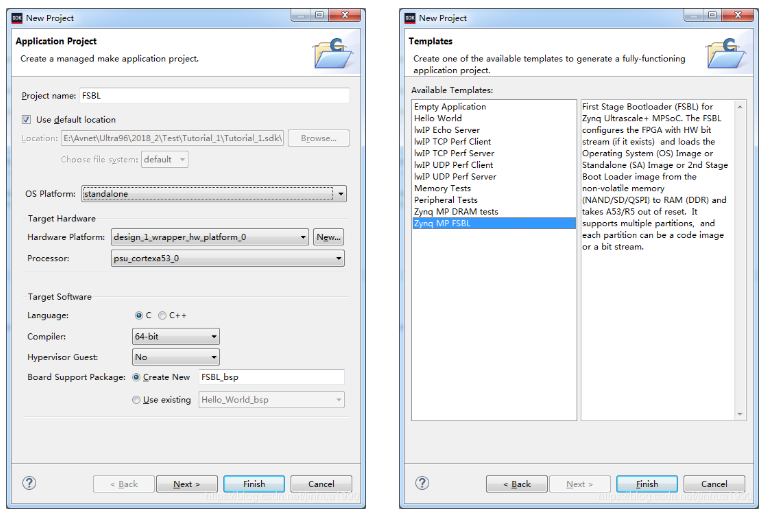

Tutorial 4:FSBL+BOOT

用过其他zynq开发平台的都会有生成FSBL这一步,虽然也可以用PetaLinux去直接生成BOOT.bin文件。

创建SDK工程时选择模板Zynq MP FSBL,不要忘记bsp配置uart_1,配置好就可以了,SDK自动编译生成FSBL.elf文件。

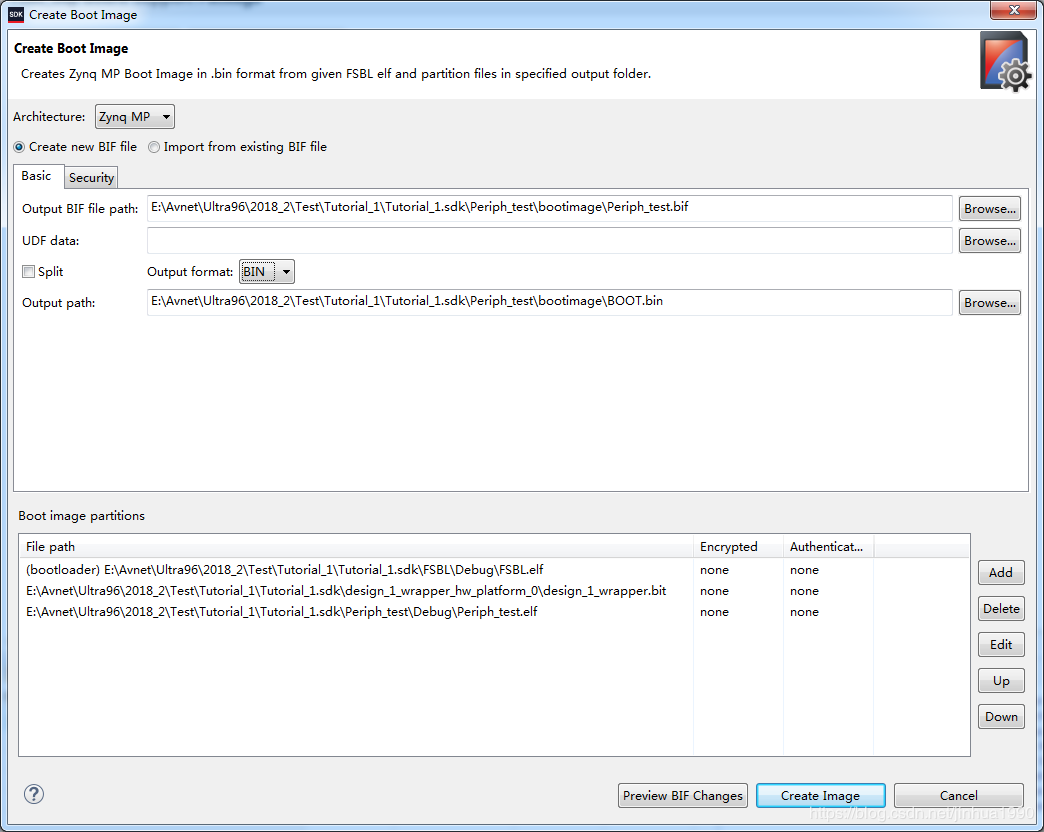

选择串口测试来生成boot.bin文件,选择Periph_test工程,选择Xilinx——> Create Boot Image,如果在同一个工程的话,会默认选择好,直接生成,否则需要导入文件,并且对应相应文件的排列顺序,选择生成BIN文件即可创建完成。

将BOOT.bin拷贝到SD卡,拨码开关选到SD卡启动,连接到串口,启动后就可在串口中打印出对应Peripheral Tests的输出信息。

Ultra96的基础教程就完事了,后续将继续根据这个开发板做一些学习记录。