作者:小青菜哥哥

原文链接:https://mp.weixin.qq.com/s?__biz=MzUxMTcyNDQyMQ==&mid=2247484506&idx=1&s...

声明:本文由原创博主授权转发,如需转载请联系博主

本篇参考xilinx官方JESD204 IP核的数据手册PG066,具体介绍基于该IP核的JESD204B数据传输实现方法~

第一次设计

在vivado开发软件中例化JESD204 IP核时,xilinx提供了一个基于verilog语言的例子工程设计。用户可以先熟悉例子程序,然后基于该例子二次开发适用于自己的工程设计,极大的降低难度。

串行线速率和时钟

JESD204B协议并没有定义某一固定的串行数据传输线速率,而是给出了线速率的范围312.5Mb/s~12.5Gb/s,xilinx 公司提供的JESD204IP核则支持1Gb/s~12.5Gb/s的线速率。

在绝大多数应用中,串行线速率的大小是由与FPGA相连的ADC或者DAC芯片决定的。JESD204 IP核工作的核时钟(coreclock)频率必须是线速率的1/40倍,并且线速率的大小也决定了FPGA的高速串行收发器(MGT)的参考时钟频率的选择范围。

核时钟(core clock)

JESD204 IP核内部的数据操作都是32bit(4字节)宽度,核时钟频率总是等于线速率的1/40倍。比如数据传输的线速率为4Gbs,则IP核工作的核时钟就为100MHz,基于AXI4-streaming的RX和TX数据传输接口的时钟都是100MHz。

参考时钟(reference clock)

在JESD204_PHY中的GTP/GTX/GTH/GTY串行收发器需要一个稳定、低抖动参考时钟。为了简化系统,在一些应用中参考时钟频率和核时钟频率可以相等。但是用户必须明白,这两个时钟其实不是一个东西。

配置时钟(AXI4-lite clock)

JESD204 IP核内部很多配置寄存器和状态寄存器,某些需要读写控制。读写控制的接口采用的是AXI4-lite接口协议,因此该IP核还需要专门的配置时钟AXI4-liteclock。

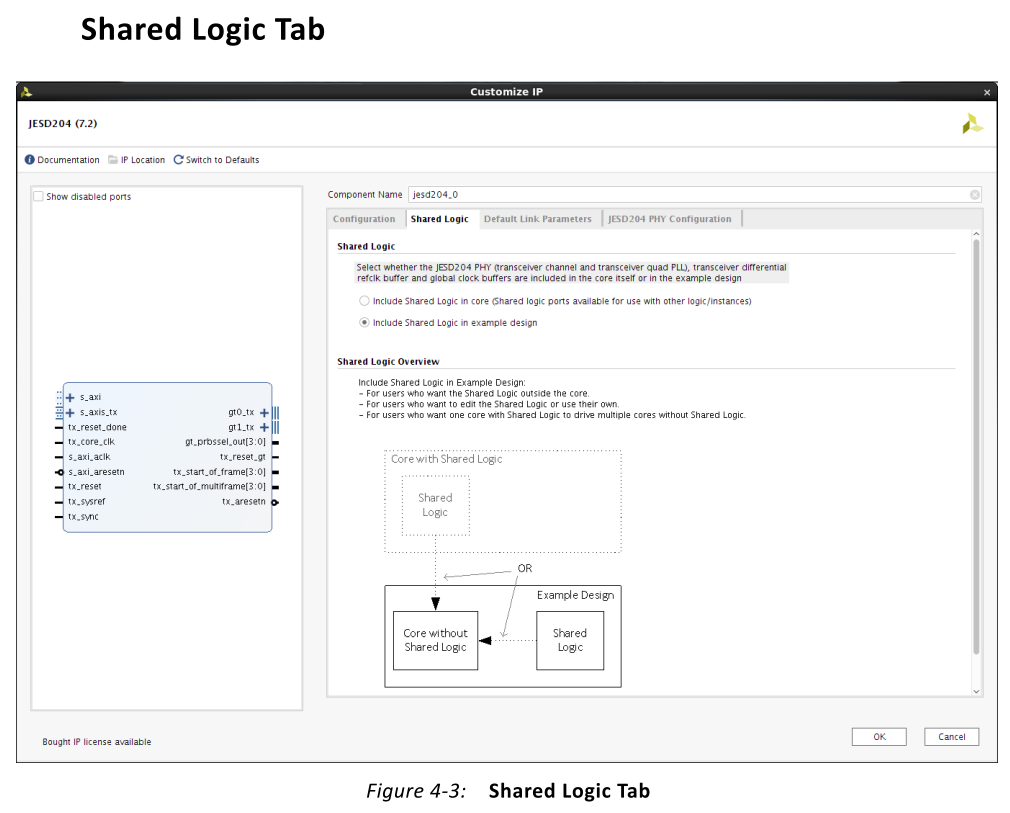

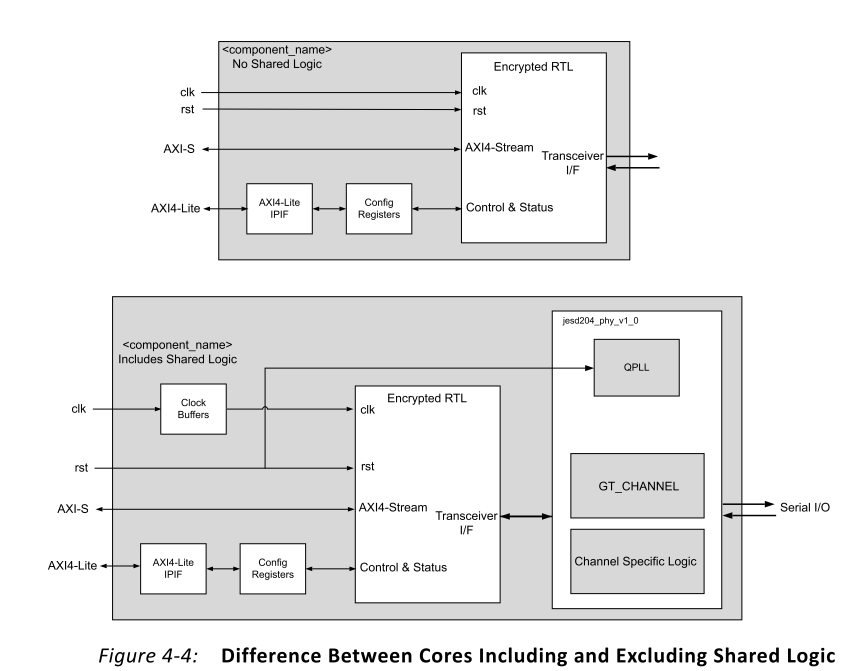

IP核的例化选择——Shared Logic Example Design

当JESD204 IP核在vivado中例化时,有一个很重要的选择项“Shared Logic Example Design”。默认的选项是“Include Shared Logic in Example Design”,在这种情况下,JESD204_PHY核和一些其它的共享逻辑不会被包含,也就是说只有JESD204B协议的功能,不包括时钟、收发器部分等逻辑。

为了能够使用JESD204_PHY核和其它辅助逻辑,用户需要基于该例化的IP核生成例子工程,工程中就包含了全部的逻辑功能。该例子工程非常有用,一般来说用户基于该例子工程二次开发自己的工程即可,用户可以修改任何参数和代码,十分灵活。

如果用户选择了“Include Shared Logic in Core”,则例化后的IP核包含了JESD204 IP核、JESD204_PHY核以及其它辅助逻辑(例如时钟逻辑)等全部功能。对于简单的jesd204B功能实现来说,选择“IncludeShared Logic in Core”更方便,但缺点是不够灵活,用户不能进行任何更改。

收发器共享

由于JESD20B协议是单向传输协议,因此JESD204IP核只能作为发送器或者接收器,不能同时收发,然而Xilinx的GTP/GTX/GTH/GTY收发器却能够同时收发。因此,在某些需要同时收发数据的JESD204链路的应用中,同时例化TX和RX 的JESD204核,但却共享一个JESD204_PHY核,这种操作就是收发器共享,该功能被目前的JESD204IP核支持。

子类模式

JESD204IP核支持3种子类模式,通过寄存器配置可以控制IP核的子类工作模式。默认的工作模式是子类1,此模式需要SYSREF参考信号。子类0和子类2则不需要SYSREF信号。

子类0

子类0被设计成向后兼容JESD204A,除了将最大线速率提升至12.5Gb/s外,其它功能和JESD204A一致。还子类不支持确定性延迟,不需要SYSREF信号。

子类1

子类1通过用户在外部提供一个SYSREF信号来支持确定性延迟,该SYSREF信号分布于JESD204B系统的所有器件,作为唯一的时间参考点。SYSREF信号可以是“one-shot”、“periodic”或者“gappedperiodic”, JESD204 IP核支持这3种形式的SYSREF。

子类2

子类2通过SYNC 信号来支持确定性延迟。

时钟(非常重要)

本节介绍JESD204核正常工作所需的时钟。

每条链路的lane数量

每条链路(一个JESD204IP核)支持的最大lane数量是8路,如果一条链路的数据需求超过8路,则可以将多个IP核级联工作。

对于例化为发送器的IP核来说,每个IP核的每条lane的ID都需要通过LaneID寄存器配置来设定。

对于例化为接收器的IP核来说,每个IP核的每条lane的ID都可以从ILA Config Data 3寄存器的LID数据段中读取。

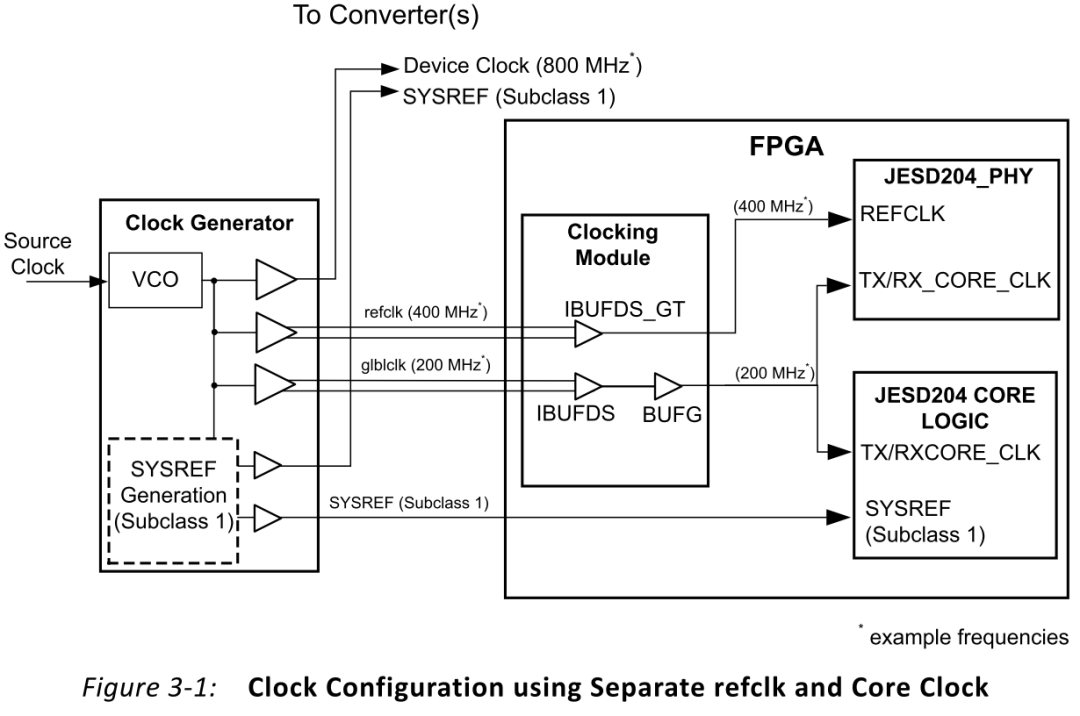

通用时钟方案

图3-1所示为最通用、灵活的时钟解决方案。在图中,refclk和glblclk均由同一外部时钟芯片产生,进入FPGA后分别作为JESD204_PHY内部收发器的参考时钟和JESD204IP核的核时钟。在这种方式下,参考时钟和核时钟完全物理上分离,它们可以运行在不同的时钟频率下而没有相互限制。唯一的限制就是参考时钟的频率值要根据收发器线速率的大小而选择,核时钟的频率值则完全等于线速率的1/40倍。

在Artix-7, Kintex-7 和Virtex-7中,如果参考时钟频率值不在其可作为核时钟的频率范围之内时,必须选择图3-1的方案(表3-1~表3-3)。

在UltraScale和UltraScale+中,如果参考频率值不和核时钟频率值相同,也必须使用图3-1方案。

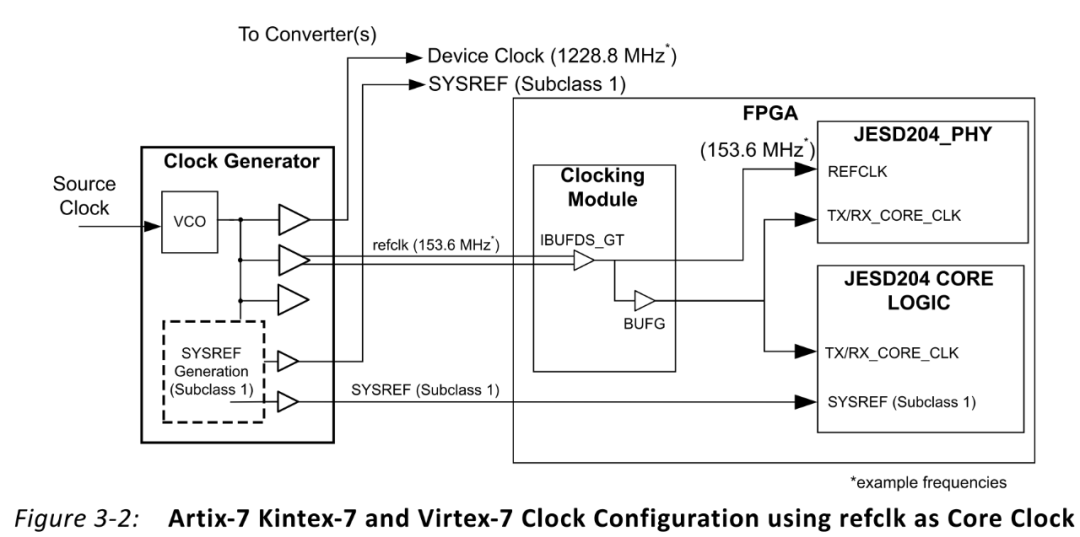

如图3-2所示为参考时钟作为核时钟的时钟方案。该方案适用于当参考时钟频率值处于其可作为核时钟的频率范围之内时的Artix-7,Kintex-7 和Virtex-7设备。

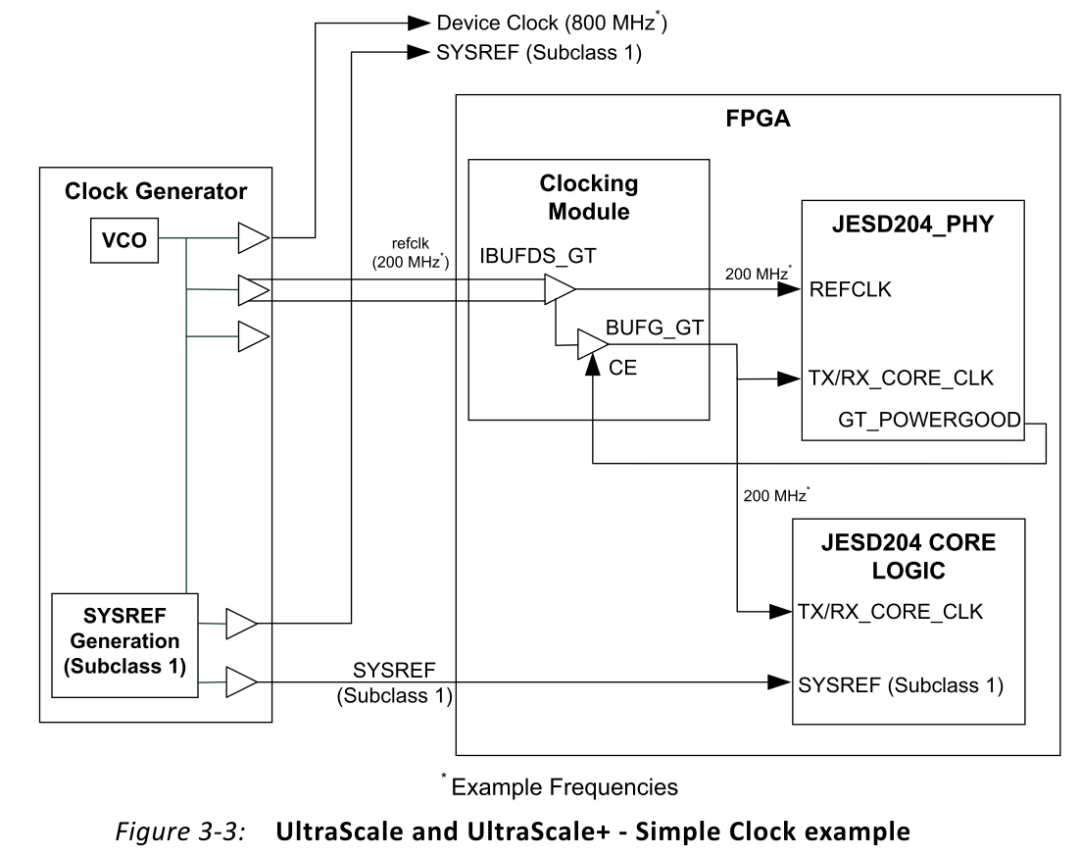

如图3-3所示同样为参考时钟作为核时钟的时钟方案。该方案适用于当参考时钟频率值处于其可作为核时钟的频率范围之内时的UltraScale和UltraScale+设备。

支持的时钟频率范围

表3-1~3-7为IP核所支持的设备的相关参数范围:

| Table 3-1: Frequency Ranges for Artix-7 Devices | |||

| Device Family: Artix-7 and Zynq-7000 (GTP Transceiver) | |||

| 参数 | 速度等级 | ||

| -3 | -2 | -1 | |

| 最大线速率(Gb/s) | 6.6 | 6.6 | 3.75 |

| 最小线速率(Gb/s) | 0.5 | 0.5 | 0.5 |

| 最大参考时钟(MHz) | 660 | 660 | 660 |

| 最小参考时钟(MHz) | 60 | 60 | 60 |

| 可作为核时钟的最大参考时钟(MHz) | 165 | 165 | 93.75 |

| 可作为核时钟的最小参考时钟(MHz) | 60 | 60 | 80 |

| Table 3-2: Frequency Ranges for Kintex-7, Virtex-7 and Zynq-7000 Devices | |||

| Device Family: Kintex-7, Virtex-7 and Zynq-7000 (GTXE2 Transceiver) | |||

| 参数 | 速度等级 | ||

| -3 | -2 | -1 | |

| 最大线速率(Gb/s) | 12.5 | 10.3 | 8 |

| 最小线速率(Gb/s) | 0.5 | 0.5 | 0.5 |

| 最大参考时钟(MHz) | 700 | 670 | 670 |

| 最小参考时钟(MHz) | 60 | 60 | 60 |

| 可作为核时钟的最大参考时钟(MHz) | 165 | 165 | 165 |

| 可作为核时钟的最小参考时钟(MHz) | |||

| Table 3-3: Frequency Ranges for Virtex-7 Devices Using GTHE2 | |||

| Device Family: Virtex-7 (GTHE2 Transceiver) | |||

| 参数 | 速度等级 | ||

| -3 | -2 | -1 | |

| 最大线速率(Gb/s) | 12.5 | 11.3 | 8.5 |

| 最小线速率(Gb/s) | 0.5 | 0.5 | 0.5 |

| 最大参考时钟(MHz) | 820 | 820 | 820 |

| 最小参考时钟(MHz) | 60 | 60 | 60 |

| 可作为核时钟的最大参考时钟(MHz) | 165 | 165 | 165 |

| 可作为核时钟的最小参考时钟(MHz) | 80 | 80 | 80 |

| Table 3-4: Frequency Ranges for Kintex and Virtex UltraScale Architecture-GTHE3 | |||

| Device Family: Kintex UltraScale (GTHE3 Transceiver) | |||

| 参数 | 速度等级 | ||

| -3 | -2 | -1 | |

| 最大线速率(Gb/s) | 12.5 | 12.5 | 12.5 |

| 最小线速率(Gb/s) | 0.5 | 0.5 | 0.5 |

| 最大参考时钟(MHz) | 820 | 820 | 820 |

| 最小参考时钟(MHz) | 60 | 60 | 60 |

| 可作为核时钟的最大参考时钟(MHz) | 312.5 | 312.5 | 312.5 |

| 可作为核时钟的最小参考时钟(MHz) | 80 | 80 | 80 |

| Table 3-5: Frequency Ranges for Kintex and Virtex UltraScale Architecture-GTYE3 | |||

| Device Family: Kintex and Virtex UltraScale (GTYE3 Transceiver) | |||

| 参数 | 速度等级 | ||

| -3 | -2 | -1 | |

| 最大线速率(Gb/s) | 12.5 | 12.5 | 12.5 |

| 最小线速率(Gb/s) | 0.5 | 0.5 | 0.5 |

| 最大参考时钟(MHz) | 820 | 820 | 820 |

| 最小参考时钟(MHz) | 60 | 60 | 60 |

| 可作为核时钟的最大参考时钟(MHz) | 312.5 | 312.5 | 312.5 |

| 可作为核时钟的最小参考时钟(MHz) | 80 | 80 | 80 |

| Table 3-6: Frequency Ranges for Kintex, Virtex and Zynq Ultrascale+ Architecture-GTHE4 | |||

| Device Family: Kintex UltraScale (GTHE4 Transceiver) | |||

| 参数 | 速度等级 | ||

| -3 | -2 | -1 | |

| 最大线速率(Gb/s) | 12.5 | 12.5 | 12.5 |

| 最小线速率(Gb/s) | 0.5 | 0.5 | 0.5 |

| 最大参考时钟(MHz) | 820 | 820 | 820 |

| 最小参考时钟(MHz) | 60 | 60 | 60 |

| 可作为核时钟的最大参考时钟(MHz) | 312.5 | 312.5 | 312.5 |

| 可作为核时钟的最小参考时钟(MHz) | 80 | 80 | 80 |

| Table 3-7: Frequency Ranges for Kintex, Virtex and Zynq Ultrascale+ Architecture-GTYE4 | |||

| Device Family: Kintex, Virtex and Zynq UltraScale (GTYE4 Transceiver) | |||

| 参数 | 速度等级 | ||

| -3 | -2 | -1 | |

| 最大线速率(Gb/s) | 12.5 | 12.5 | 12.5 |

| 最小线速率(Gb/s) | 0.5 | 0.5 | 0.5 |

| 最大参考时钟(MHz) | 820 | 820 | 820 |

| 最小参考时钟(MHz) | 60 | 60 | 60 |

| 可作为核时钟的最大参考时钟(MHz) | 312.5 | 312.5 | 312.5 |

| 可作为核时钟的最小参考时钟(MHz) | 80 | 80 | 80 |

时钟模块方案详述

对于上述的所有的器件族(GTP,GTXE2, GTHE2, GTHE3, GTYE3, GTHE4 and GTYE4收发器),用户都可以使用图3-1~图3~3的通用时钟方案。基于用户所选的“Shared Logic”选项,时钟方案的代码会作为IP核的一部分或者作为可编辑的例子工程的一部分。

对于基于GTP收发器的Artix-7设备,JESD204_PHY核处理数据的位宽是16bit,而JESD204IP核处理数据的位宽是32bit,因此时钟模块必须另外给收发器提供一个双倍于核时钟频率的内部时钟。在例子代码中,双倍时钟由MMCM来提供,如下图3-4所示:

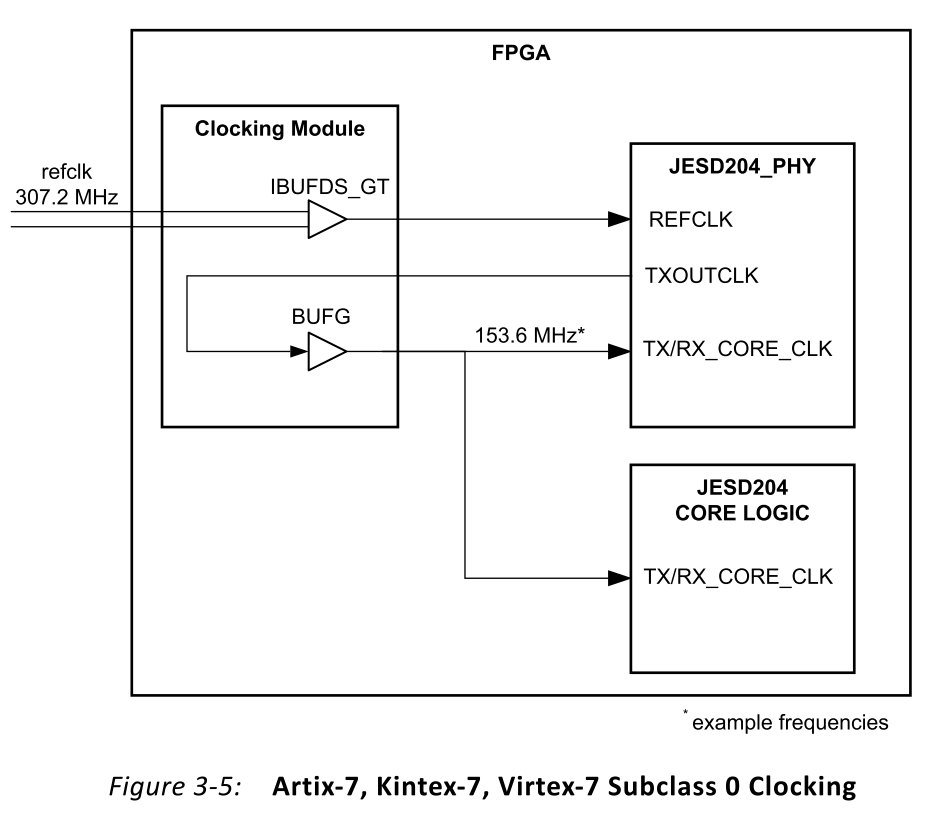

子类0的时钟方案

子类0的应用没有确定性延迟功能,时钟功能相对简单,不用提供SYSREF信号。

对于KintexUltraScale 和VirtexUltraScale设备,图3-3的时钟方案完全适用于子类0。而对于Artix-7,Kintex-7 和Virtex-7设备,可以将JESD204_PHY输出的TXOUTCLK作为核时钟的时钟源,如图3-5所示。当然对于GTP收发器,还是需要额外的MMCM来产生两倍于核时钟的TXUSRCLK/RXUSRCLK。

复位功能

JESD204 IP核使用了如下几种复位:

整个系统可以被一个异步信号复位。如果是例化成发送器,则该复位信号为tx_reset。如果是接收器,则该复位信号为rx_reset。需要注意的是只有配置寄存器不受系统复位控制,当且仅当单独的AXI4_lite接口的复位信号s_axi_aresetn被提供时,配置寄存器的值恢复到默认值。

通过AXI4_lite接口向复位寄存器写入特定的值,可以触发整个数据链路的复位,但不包括复位配置寄存器。

监视器定时复位(Watchdog Timer Reset)

不需要

当系统复位或者软件复位使能时,rx_aresetn或tx_aresetn会输出低电平

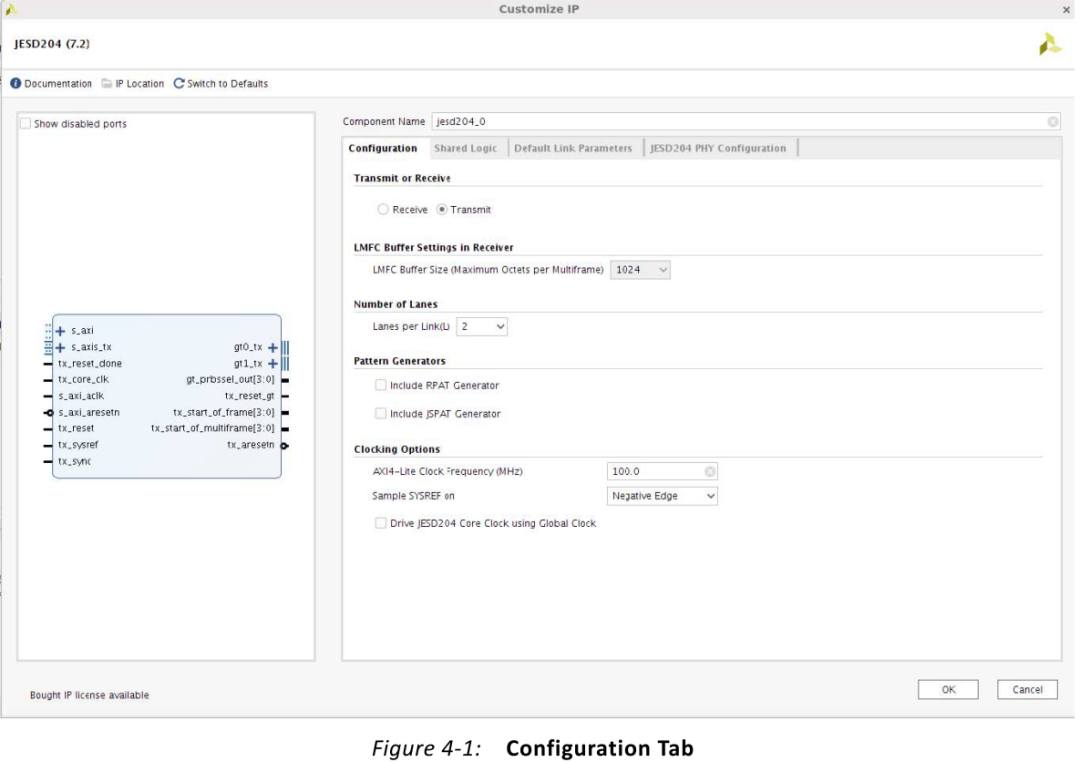

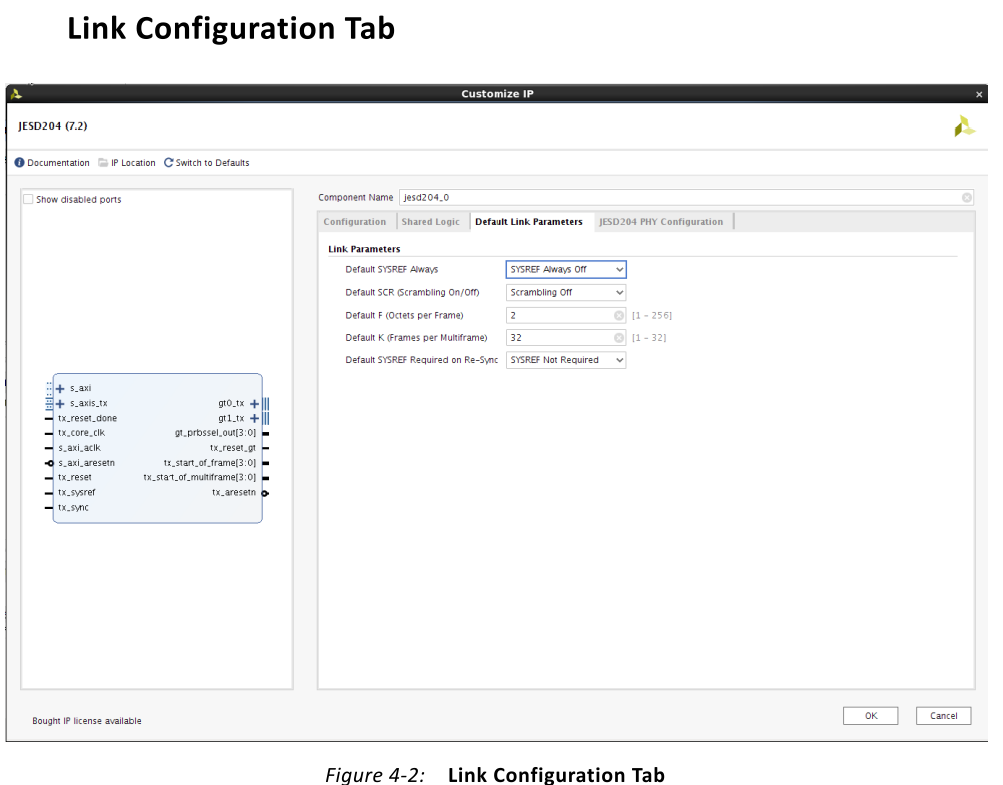

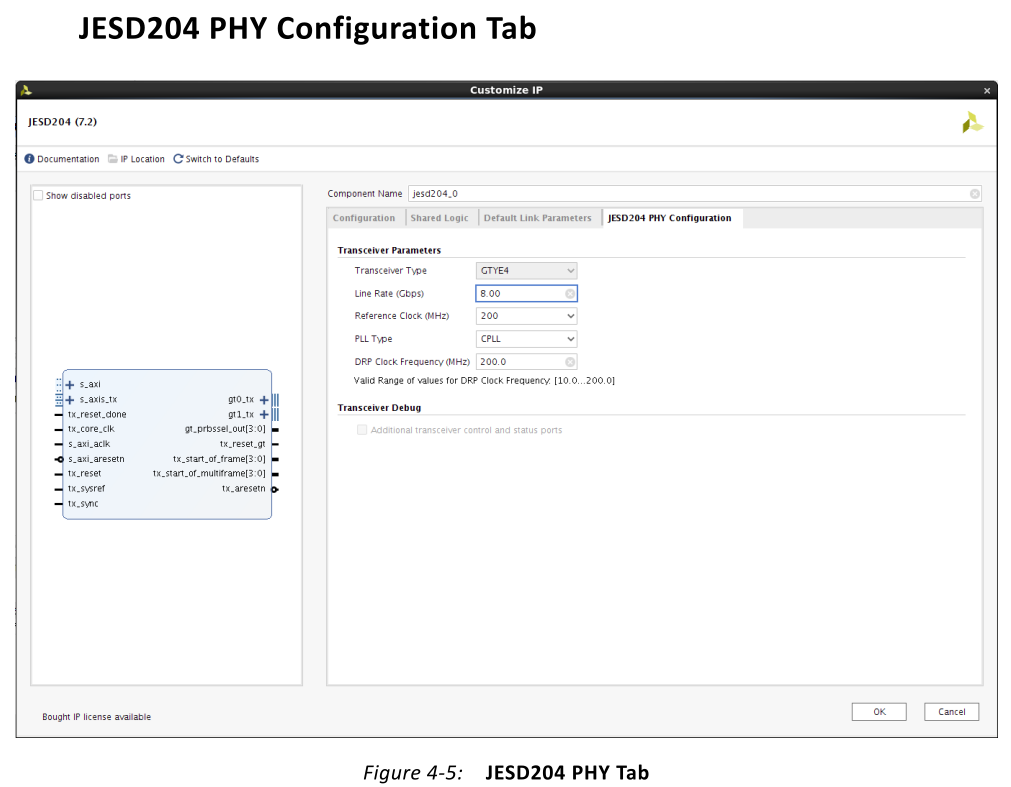

JESD204 IP核的例化界面说明

当例化JESD204 IP核时,可以选择“sharedlogic”包含在IP核内部或者是作为例程当中独立于JESD204核的单独模块。选择“IncludeShared Logic in core”后,IP核会包含JESD204 PHY核以及时钟逻辑,选择“IncludeShared Logic in example design”后,生成的例程中包含独立的JESD204B协议的IP核、JESD204PHY核以及时钟逻辑,这样对于多核设计或者收发器共享的应用来说很方便,可以共享JESD204PHY核和时钟逻辑。

对于简单的单方向数据通路应用,推荐选择“IncludeShared Logic in core”。对于既有ADC、又有DAC的应用,就选择“IncludeShared Logic in example design”,因为多个IP核可以共享QPLL和ClockBuffer模块。

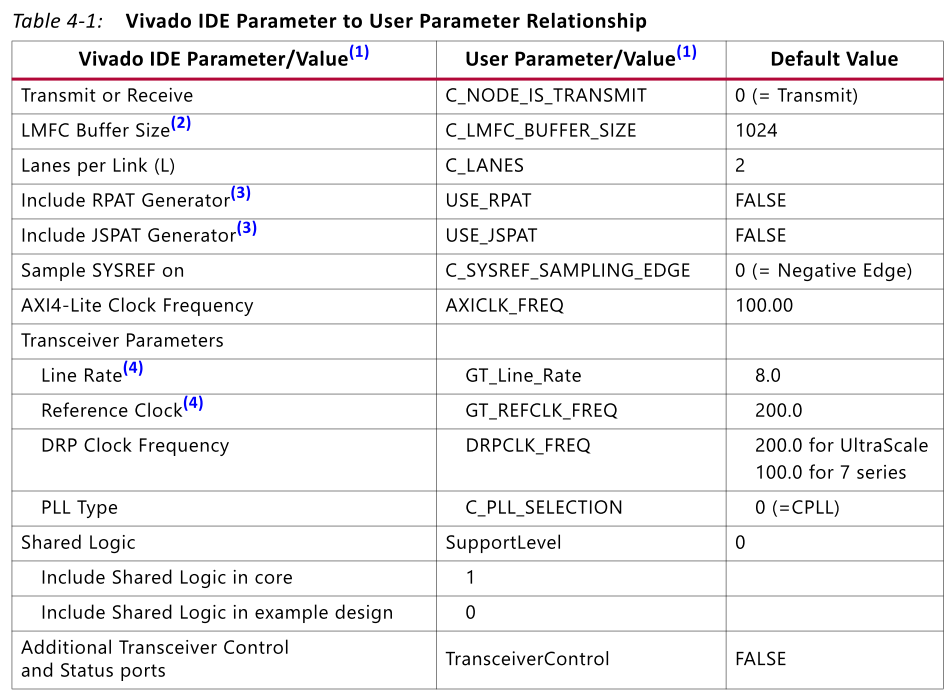

下表4-1给出了Vivado界面的参数选项和用户参数的对应关系以及默认值。

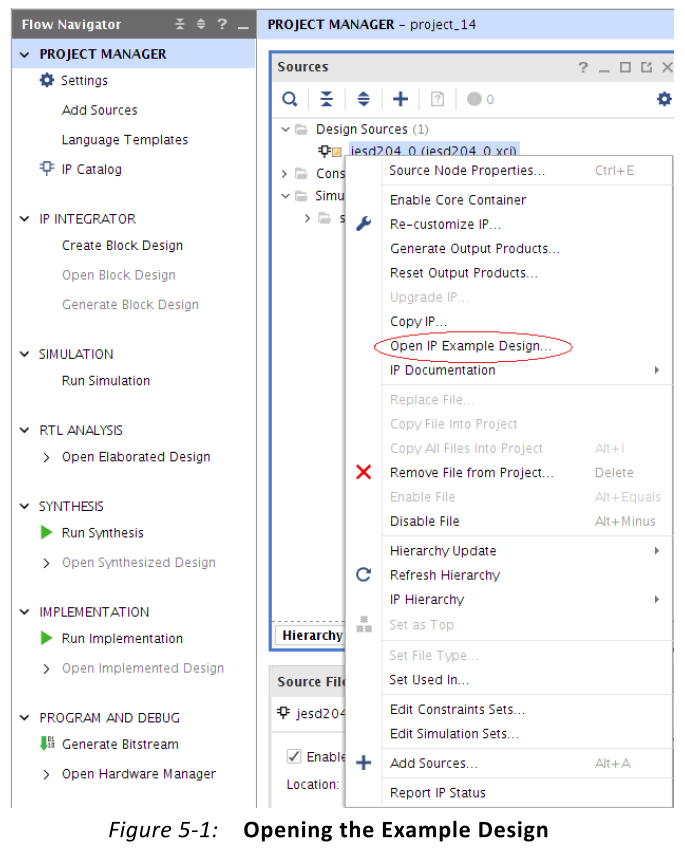

Vivado界面的参数设置完之后,点击完成。Vivado就会例化JESD204 IP核,右键单击该例化完成的IP核,选择“open IP Example Design”,即可生成例程,用户直接基于该例程就可以方便、快捷的开发出自己的工程项目了~

JESD204 IP核主要操作内容就介绍到这了,下篇将从AXI4-lite配置接口说起,来实现JESD204 IP的寄存器参数读写~