作者: 碎碎思,来源: OpenFPGA微信公众号

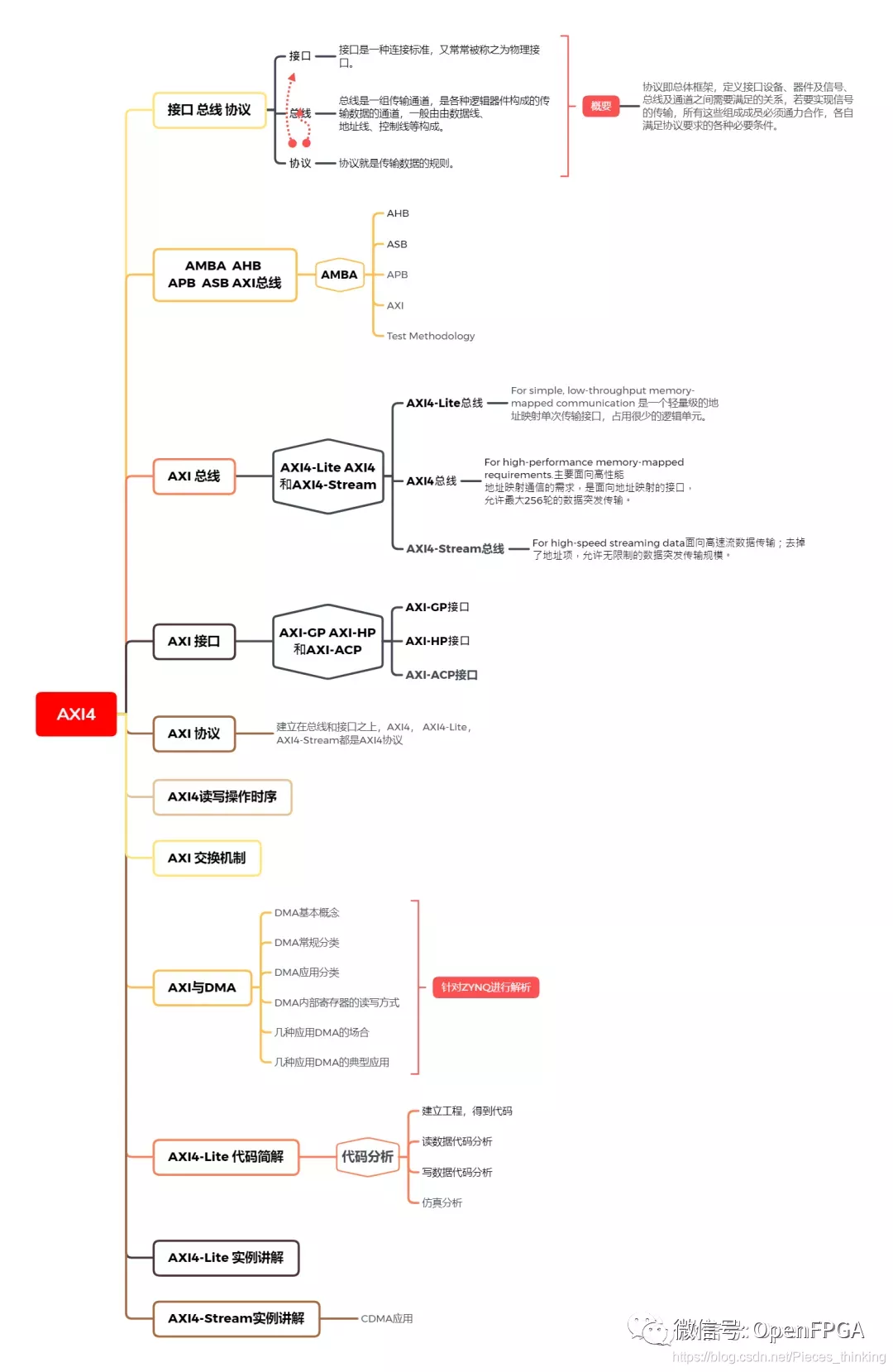

不同类型的DMA

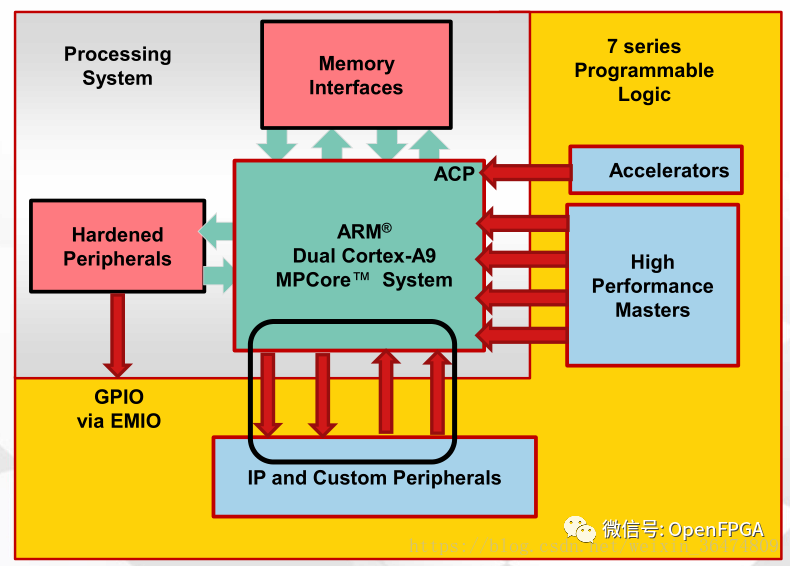

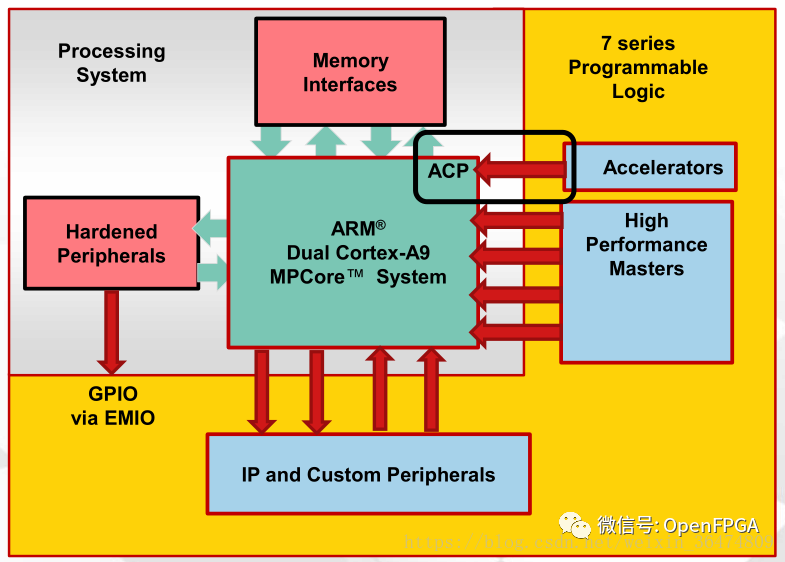

GPIO

PL general purpose AXI

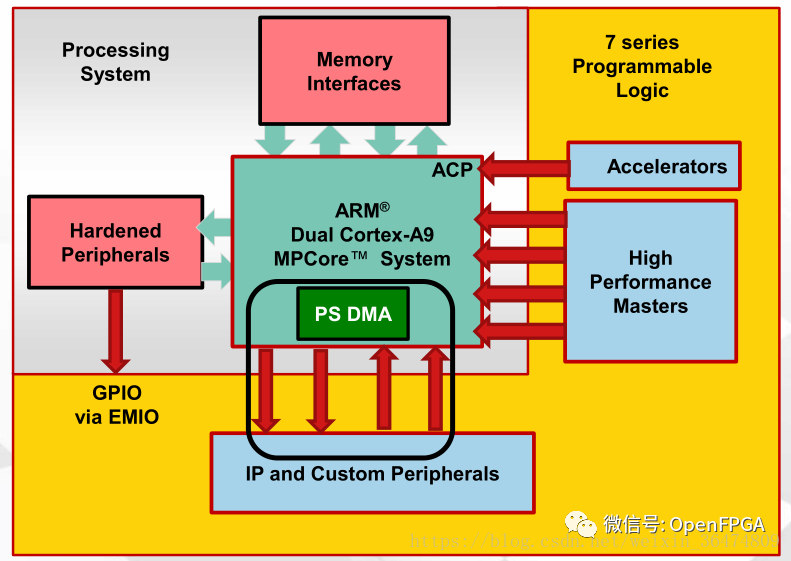

GP AXI utlilizing PS DMAC

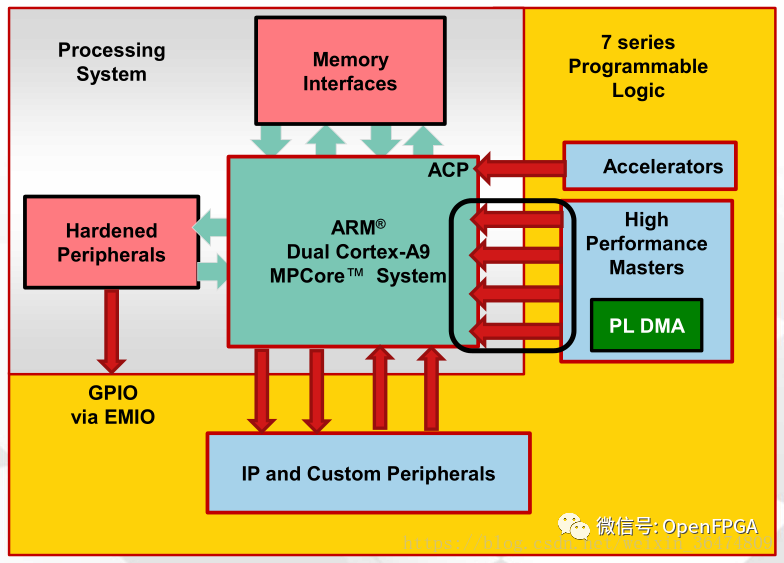

High performance w/DMA

ACP w/DMA

几种DMA的总结

ZYNQ中不同应用的DMA

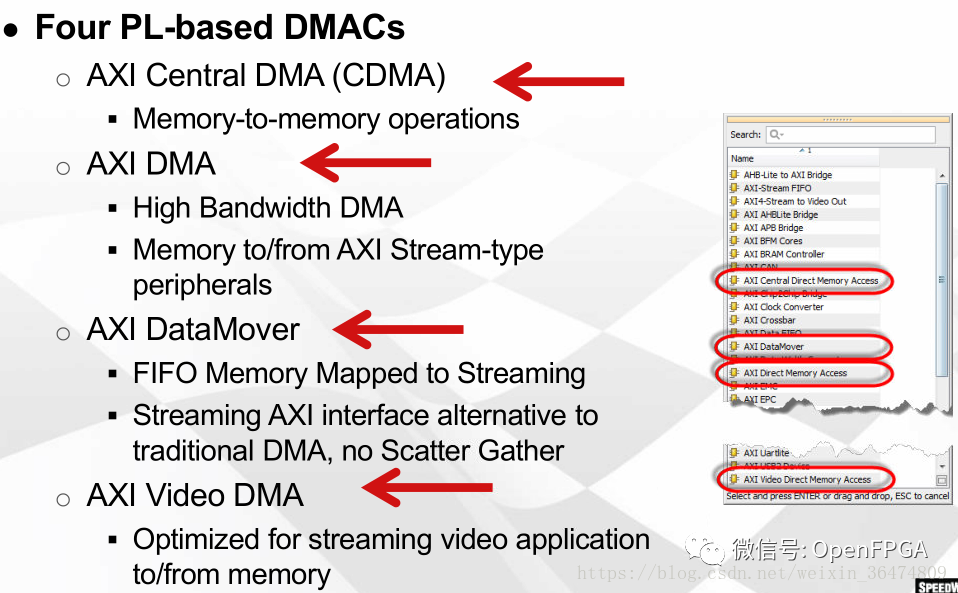

几个常用的 AXI 接口 IP 的功能(上面已经提到):

AXI-DMA:实现从 PS 内存到 PL 高速传输高速通道 AXI-HP<---->AXI-Stream 的转换

AXI-FIFO-MM2S:实现从 PS 内存到 PL 通用传输通道 AXI-GP<----->AXI-Stream 的转换

AXI-Datamover:实现从 PS 内存到 PL 高速传输高速通道 AXI-HP<---->AXI-Stream 的转换,只不过这次是完全由 PL 控制的, PS 是完全被动的。

AXI-VDMA:实现从 PS 内存到 PL 高速传输高速通道 AXI-HP<---->AXI-Stream 的转换,只不过是专门针对视频、图像等二维数据的。

AXI-CDMA:这个是由 PL 完成的将数据从内存的一个位置搬移到另一个位置,无需 CPU 来插手。

涉及到DMA主要包括AXI Centralized DMA、AXI Video DMA和AXI DMA,详细的描述及IP核如下图所示:

图4‑39 几种DMA应用

具体的描述如下表:

表4‑19 几种应用DMA描述

| 类型 | 接口名称 | 数据位宽 | 接口类型 | 功能描述 | 关键特性 |

| AXI Centralized DMA | control | 32 | AXI4-lite slave | CPU通过总线对DMA内部的源地址寄存器、目的地址寄存器、控制寄存器、状态寄存器和传输数据长度寄存器等进行初始化。 | a 兼容总线AXI4、AXI4-lite接口协议; b AXI4数据宽度支持32、64、128、256、512、1024; c AXI4-Stream 数据宽度支持8、16、32、64、128、256、512、1024; d 可选的数据重组引擎; e 独立且异步的数据通道操作; g可选S/G模式传输和普通模式传输; h 可选存储转发。 |

| Scatter/gather | 32 | AXI4 master | 从系统内存读取和更新DMA传输数据的配置信息,根据配置信息初始化CDMA传输参数,执行S/G传输模式;它卸载了CPU控制传输,实现硬件自动化。 | ||

| data read | 32、64、128、256、512、1024 | AXI4 master | 根据源地址从系统内存中读取数据。 | ||

| data write | 32、64、128、256、512、1024 | AXI4 master | 根据目的地址向系统内存中写入数据。 | ||

| AXI Video DMA | control | 32 | AXI4-lite slave | 访问VDMA内部的寄存器,对DMA内部的源地址寄存器、目的地址寄存器、控制寄存器、状态寄存器和传输数据长度寄存器等进行初始化。 | a 高带宽直接存储的视频数据流;b 具有二维DMA传送操作;c 独立且异步读取和写入通道操作;d 同步耦合帧缓冲区;e 支持最大32帧缓冲区;f 支持动态时钟频率的变化;g 配置突发传输数据的大小与行缓冲区的深度;h 处理器可访问的初始化、中断、状态和管理寄存器;i 兼容AXI4、AXI4-lite、AXI4-stream接口协议;j 可选的S/G传输模式和普通模式传输。 |

| Scatter/gather | 32 | AXI4 master | 从系统内存读取和更新DMA传输数据的配置信息,根据配置信息初始化VDMA传输参数,执行S/G传输模式;它卸载了CPU控制传输,实现硬件自动化。 | ||

| data memory mapped read(mm2s) | 32、64、128、256、512、1024 | AXI4 master | 根据源地址从系统内存中读取数据。 | ||

| data memory mapped write(s2mm) | 32、64、128、256、512、1024 | AXI4 master | 根据目的地址向系统内存中写入数据。 | ||

| data stream out | 8、16、32、64、128、256、512、1024 | AXI4-Stream master | 从VDMA侧到兼容AXI4-Stream流接口的数据传输;数据位宽必须不大于data memory mapped 数据的位宽。 | ||

| data stream in | 8、16、32、64、128、256、512、1024 | AXI4-Stream slave | 从兼容AXI4-Stream流接口到VDMA侧的数据传输;数据位宽必须不大于data memory mapped 数据的位宽。 | ||

| AXIDMA | Control | 32 | AXI-lite Slave | 访问DMA内部的寄存器,对DMA内部的源地址寄存器、目的地址寄存器、控制寄存器、状态寄存器和传输数据长度寄存器等进行初始化。 | a 兼容AXI4-liteAXI4、AXI4-Stream总线接口协议; b 可选的普通传输模式和S/G模式; c 数据宽度可至1024; d 可选AXI控制流和状态流; e 两通道是独立、全双工的。 |

| AXI MemoryMapReadMaster | 32、64、128、256、512、1024 | AXI4 Master | 根据源地址从系统内存中读取数据。 | ||

| AXI MemoryMapwriteMaster | 32、64、128、256、512、1024 | AXI4Master | 根据目的地址向系统内存中写入数据。 | ||

| Scatter/Gather | 32 | AXI4Master | 从系统内存读取和更新DMA传输数据的配置信息,根据配置信息初始化DMA传输参数,执行S/G传输模式;它卸载了CPU控制传输,实现硬件自动化。 | ||

| DataStreamOut | 32、64、128、256、512、1024 | AXI4-StreamMaster | 从DMA侧到兼容AXI4-Stream流接口的数据传输;数据位宽必须不大于data memory mapped 数据的位宽。 | ||

| DataStreamIn | 32、64、128、256、512、1024 | AXI4-StreamSlave | 从兼容AXI4-Stream的流接口到DMA侧的数据传输;数据位宽必须不大于data memory mapped 数据的位宽。 | ||

| AXI ControlStreamMaster | 32 | AXI4-StreamMaster | 控制memory to stream的数据流 | ||

| AXIStatusStreamSlave | 32 | AXI4-StreamSlave | AXI4-Stream侧传入数据流的状态 |