作者:碎碎思,来源:OpenFPGA微信公众号

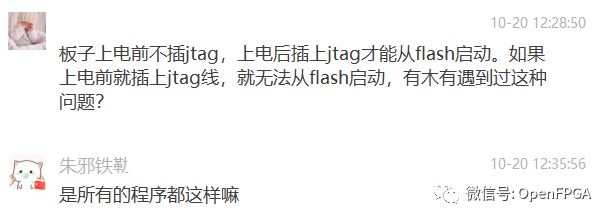

最近群里有很多人遇到上述的情况,一直觉得不可思议,以前没有遇到这种情况,如果是很常见的情况,那官网一定有人反馈,如果是极特别的情况,那么也就只能按照BUG处理了。

很幸运,官网有很多人反馈类似的问题,先把问题和解决方式放出来:

https://www.xilinx.com/support/answers/66954.html

出现这个问题的原因:

以下行为是Vivado 2016.1硬件管理器的新增功能(还是新功能,滋滋...):当板断电或断开电缆连接时,Vivado将在硬件管理器中关闭硬件目标。

重新打开板电源或重新连接电缆后,Vivado现在将自动尝试在Hardware Manager中重新打开硬件目标。

除了重新打开硬件目标之外,硬件管理器还将尝试刷新所有设备寄存器,包括读取配置状态寄存器。

由于此新行为,如果满足以下所有条件,则可能会看到间歇性配置失败:

(上面描述的就是我们说的;在JTAG下载器连接时FPGA不加载flash里的程序,基本就一样不差)

如果使用了任何配置接口(JTAG除外),并且还连接了JTAG电缆,则JTAG链自动检测和/或寄存器读取可能会中断配置,并且在加电或重启后将无法完成配置。

有关更多详细信息,请参阅(UG908)。

在以下三种情况下可能会发生此问题(上面情况时必发生的):

1. 设备上电或重启。脉冲PROGRAM_B不会导致此问题,因为Vivado硬件管理器看不到电缆断开连接并执行了电缆自动检测。

2. 用户发出“ refresh_hw_devices”命令

3. 用户插入JTAG电缆

解决办法:

一、通过Vivado_init.tcl脚本避免情况发生

1)新建一个Vivado_init.tcl脚本,添加一下内容:

set_param labtools.auto_update_hardware 0

2)将脚本放到:

installdir /Vivado/version/scripts/Vivado_init.tcl

目录下

installdir是Vivado Design Suite的安装目录。

或者

添加本地用户目录:

1. 对于Windows 7:%APPDATA%/ Roaming / Xilinx / Vivado / Vivado_init.tcl

2. 对于Linux:$ HOME / .Xilinx / Vivado / Vivado_init.tcl

如果这两个位置都存在Vivado_init.tcl,则Vivado首先从安装目录中获取文件,然后从您的主目录中获取文件。

有关更多信息,请参见《(UG894)Vivado Design Suite用户指南中的使用Tcl脚本》中的“加载和运行Tcl脚本”一章。

http://www.xilinx.com/cgi-bin/docs/rdoc?v=latest;d=ug894-vivado-tcl-scri...

二、在加电或重新启动电源之前,请拔下电缆。

三、减慢轮询的发生。

例如,每小时轮询一次,请使用以下选项启动hw_server:

hw_server -e "set jtag-poll-delay 3600000000"

This command should be called in the CMD window instead of Vivado Tcl console.

四、按以下步骤在JTAG模式下关闭并重新打开目标,以防止发生任何轮询,然后恢复到正常模式:

1)在JTAG模式下关闭并重新打开目标:

set tmp_target [ get_hw_targets -filter { IS_OPENED == 1 }]close_hw_target $tmp_target

open_hw_target -jtag_mode on $tmp_target

set_property LOCK true [get_property HW_JTAG $tmp_target]

2)软件启动后,恢复到正常模式:

set_property LOCK false [get_property HW_JTAG $tmp_target

close_hw_target $tmp_target

open_hw_target $tmp_target

我试过第一种方式,同时用两种方式加载了Vivado_init.tcl,问题可以解决。

也试过在重新上电的过程中关闭Vivado(不让JTAG工作),也是可以正常启动的,其他方式大家可以多去尝试。

官方这种处理方式有一定便携性和局限性,各有优缺点,不知道大家怎么看。