本文转载自:亦梦云烟的博客

在编写ZYNQ的FPGA逻辑代码过程中,往往需要对时序进行分析。时序信号的分析一般通常有软件仿真和在线仿真两种,本文介绍这两种方法的具体使用方法。

一. Vivado软件时序仿真

建立时序仿真的步骤:

1. 建立工程后,添加源文件,本文以一个非常简单的模块——生成1Hz方波,进行说明。

module clock_1Hz(

clock, //input system clock,30MHz

clk //output 10Hz clock, 10Hz

);

input wire clock;

output reg clk;

reg [24:0]cnt;

always @(posedge clock)

begin

cnt <= cnt + 1'b1;

if(cnt > 15000000)

begin

cnt <= 0;

clk <= ~clk;

end

end

endmodule

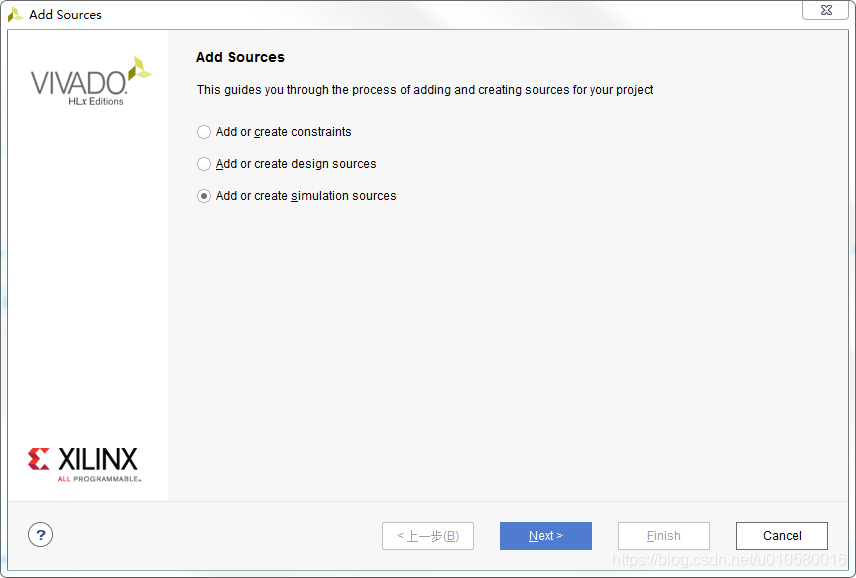

再点击Add sources选择第三个添加仿真文件。

点击Create File创建仿真文件,命名为clock_1Hz_sim.v

编写仿真测试程序:

`define clk_peirod 10

module clock_1Hz_sim();

reg clk;

wire clk_10Hz;

clock_1Hz clock_1Hz_0(

.clock(clk),

.clk(clk_10Hz)

);

initial clk = 1;

initial

begin

#(`clk_peirod*100);

$stop;

end

always #(`clk_peirod/2) clk = ~clk;

endmodule

2.器件库编译,在vivado菜单的Tools->Compile Simulation Libraries...,仿真工具选择ModelSim,其他默认即可,等待编译结束。

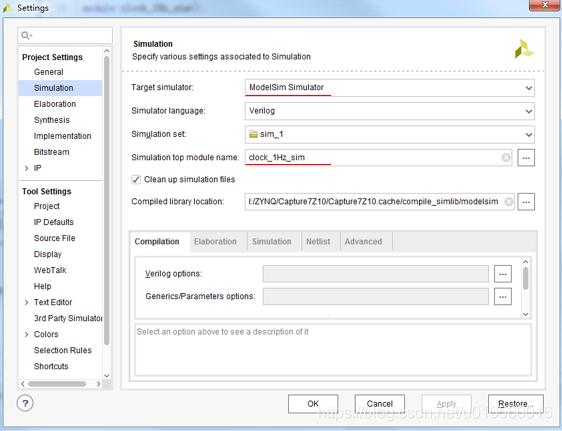

设置仿真工具,点击菜单Flow->Settings->Simulation,选择ModelSim Simulator进行仿真,仿真文件设置为clock_1Hz_sim。

点击仿真工具进行仿真,SIMULATION->Run Simulation->Run behavioral Simulation。

启动ModelSim后,软件可能报错,如下所示:

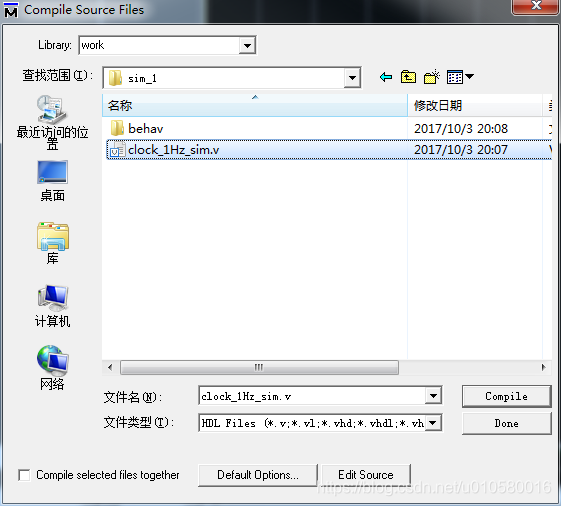

出现这种情况是因为软件没有找到源文件,手动将源文件加入到编译路径的work中,点击compile,选择源文件,加入到work目录中。

在信号上点击Add wave,可以将信号添加到仿真波形中。

点击Run all,再点击stop,可以查看波形。

二. vivado在线逻辑分析仪的使用

Vidado开发环境将逻辑分析仪嵌入在软件中,不需要额外使用ChipScope软件。在Vivado中进行硬件在线调试的步骤如下:

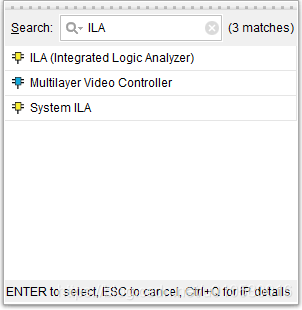

1. 在vivado工程共,添加ILA(集成逻辑分析仪)核。之后搜索ILA,添加第一个IP核即可。

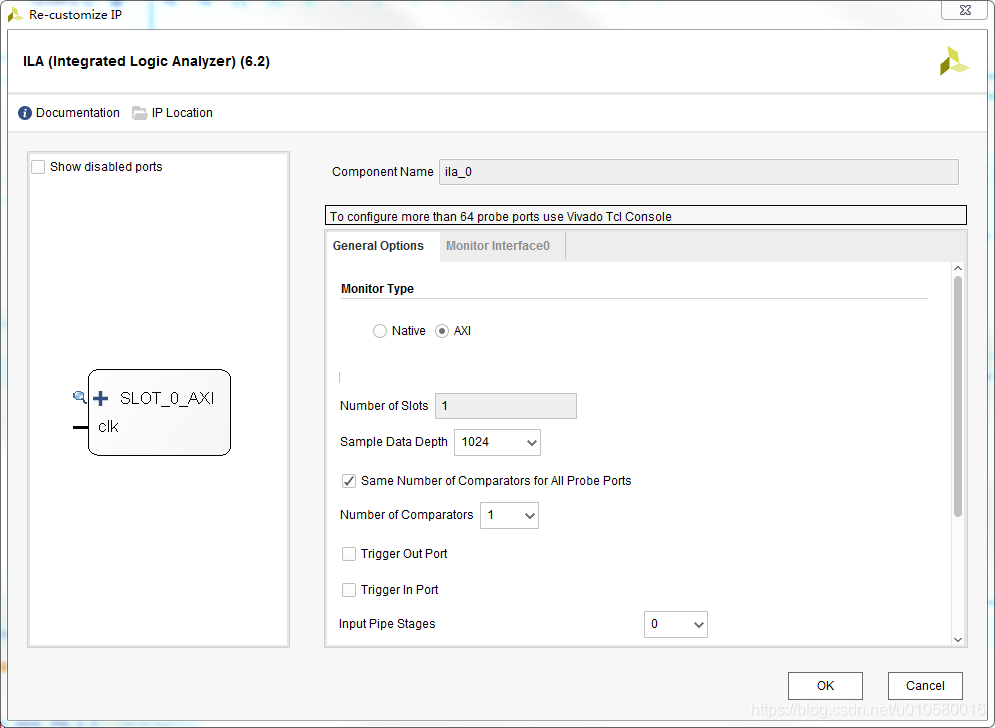

2. 新建ILA时弹出ILA配置界面,这里需要配置采集信号的时钟深度,信号宽度,保持默认即可。

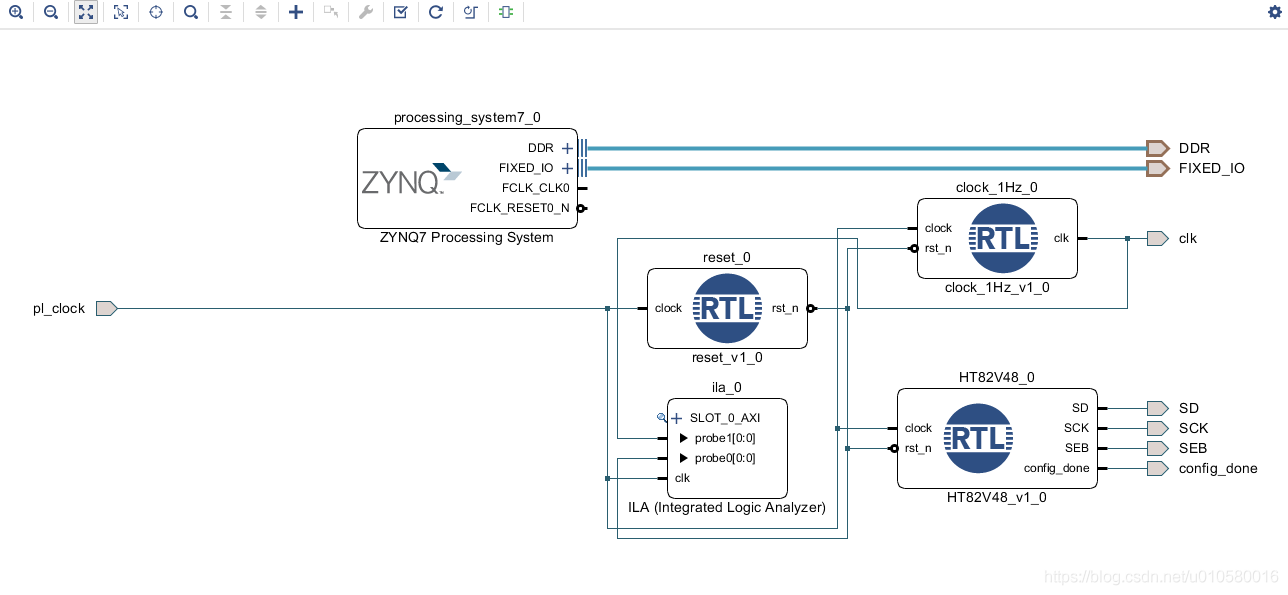

3. 在原理图中进行连线,clk信号必须要连接到时钟上,展开SLOT_0_AXI,连接需要观察的信号到这些端口上,软件会自动例化代码。

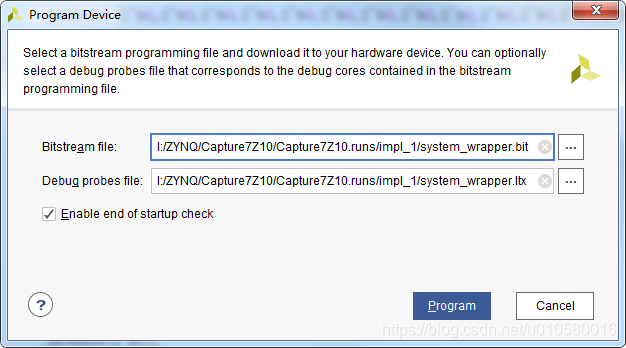

4. 综合编译后生成bit流文件,下载到电路板中,其中Debug probes file中会多添加ltx文件。

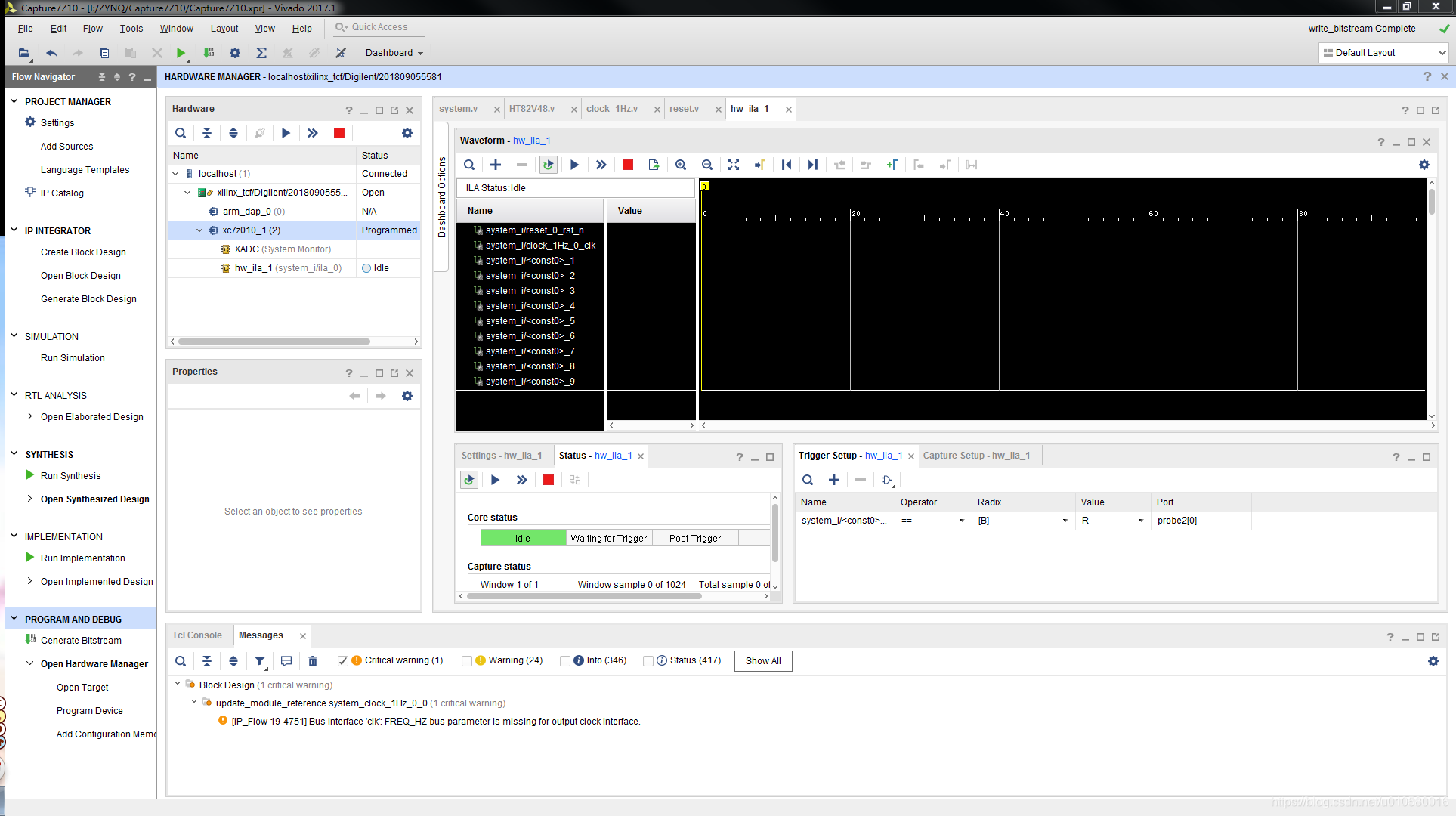

5. 打开逻辑分析仪窗口: 点击菜单Window->Debug Probes

6. 软件界面中将会出现逻辑分析仪窗口,如下所示:

7. 点击逻辑分析仪窗口右上角的float图标可以让该窗口独立出来,达到最大化视图的效果。

8. 在Trigger Setup窗口点击+号图标,添加信号触发的条件,点击运行可观察到波形。

注:

1. ILA的时钟输入必须比采集的信号频率至少大两倍,否则无法触发。

2. 如果ILA的时钟输入时PS产生的,在下载完FPGA后debug probes界面不会有任何显示,只有当PS 部分的程序启动之后才会执行ILA。