作者:BIGMAC,来源:图灵研究院微信公众号

注:本文由作者授权转发,如需转载请联系作者本人

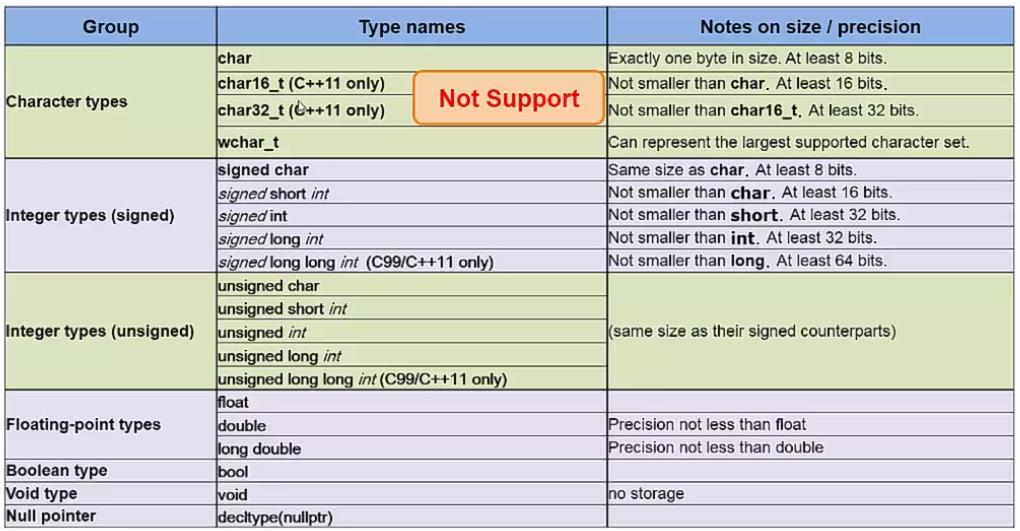

1. 传统C语言支持的数据类型

其中要说明的是,Vitis HLS不支持“char16_t”以及“char32_t”这两种数据类型。

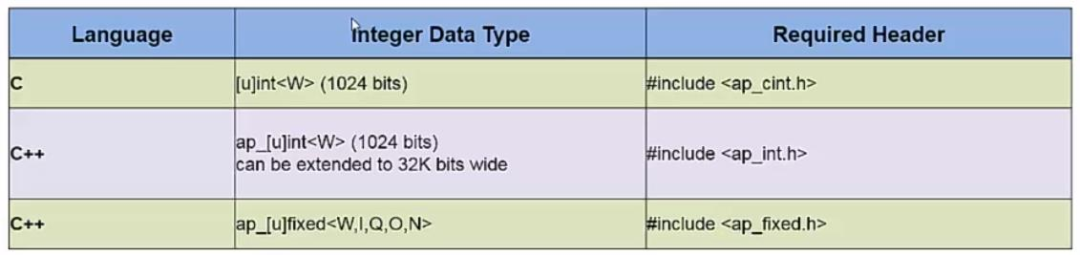

2. HLS引入了任意精度的数据类型

2. 1 为何要使用任意精度的数据类型

C语言的原生数据类型都是基于8bit为边界的(比如8、16、32、64bits)。但FPGA开发人员在RTL代码开发中经常需要用自定义位宽的数据类型,如果强制用8bit为边界的数据类型,可能会增加资源的开销和降低运算的速度。

例如实现一个18bit*18bit的乘法器,如果采用以8bit为边界的数据类型,则输入数据的长度都需要扩展定义为32bit。乘法器的输出结果需要用64bit数据来表示。这种运算对于Xilinx 7系列的FPGA来说,需要消耗4个DSP48E1单元。

2. 2任意精度的数据类型定义

在HLS中,我们可以采用以下方式来定义任意精度的数据类型:

如在C++中,可以采用“ap_[u]int

例如:ap_int<6> data;定义了一个6bit位宽的int类型变量。

注:ap为ArbitraryPrecision的缩写。

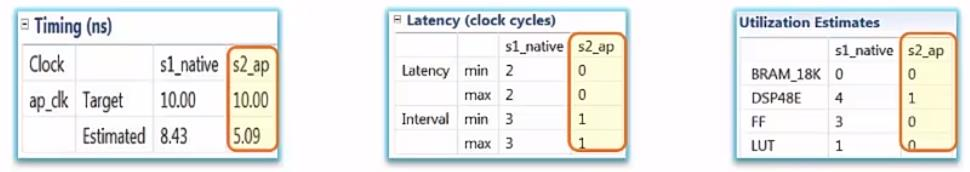

例子:对于一个18bit*18bit的乘法器,输入数据采用ap_int<18>,输出数据采用ap_int<36>。下图展示了采用传统C语言的数据类型方式(s1_native)和任意精度数据类型方式(s2_ap)的HLS编译结果。

图中结果可以明显看出,采用任意精度的解决方案(s2_ap)生成的RTL比C语言默认的数据类型解决方案(s1_native)生成的RTL时钟可以运行在更高的频率上、系统周期延迟也显著的降低、资源使用总数也显著的降低。

因此,采用任意精度数据类型,可以在获得相同精度的运算条件下,运算速度更快且使用更少的资源。

2. 3任意精度类型数据的初始化

例,对一个6bit位宽的int变量进行初始化,第一种方式为“copy intialiation”:

ap_int<6> a_6bit_var_c = -22

第二种方式为“direct initialization”:

ap_int<6> a_6bit_var_c(-22)

赋值的时候,指定数据格式方式如下:

ap_int<6> a_6bit_var_c(“0b101010”, 2);(二进制)

ap_int<6> a_6bit_var_c(“0x2A”, 16);(十六进制)

也可以将前缀“0b”、“0x”省略掉,如下:

ap_int<6> a_6bit_var_c(“101010”, 2);(二进制)

ap_int<6> a_6bit_var_c(“2A”, 16);(十六进制)

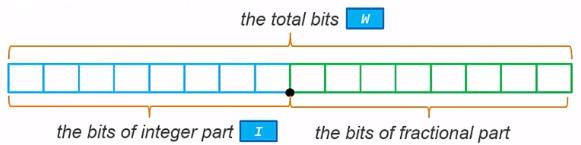

2. 4 ap_[u]fixed

ap_[u]fixed

例如,变量定义和初始化如下

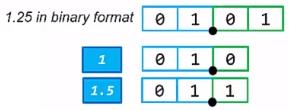

ap_[u]fixed<3, 2> var1 = 1.25;

由于1.25对应的二进制形式为0101(蓝色为整数部分,绿色为小数部分),但ap_[u]fixed<3,2>的定义相当于取了1.25的2bit整数部分,1bit的小数部分,即最终数据为010,即代表数据1。

如果定义和初始化改为如下:

ap_[u]fixed<3, 2, AP_RND> var2 = 1.25,Q参数为AP_RND,即低位采用四舍五入的方式,最终var2的二进制为011,代表数据为1.5。

3. 小结

任意精度类型的数据在不同类型之间可以进行显示或隐式转换,本文章就不一一介绍了,详细可以查看高亚军老师的HLS教学视频。

链接如下:https://www.bilibili.com/video/BV1bt41187RW?p=6

---------------------------------

参考文献:

[1]《Vitis High-Level Synthesis User Guide》. UG1399. Xilinx

[2]“跟Xilinx SAE学HLS系列视频讲座-高亚军 ”https://www.bilibili.com/video/av41246874