本文转载自: FPGA打工人微信公众号

注:本文由作者授权转发,如需转载请联系作者本人

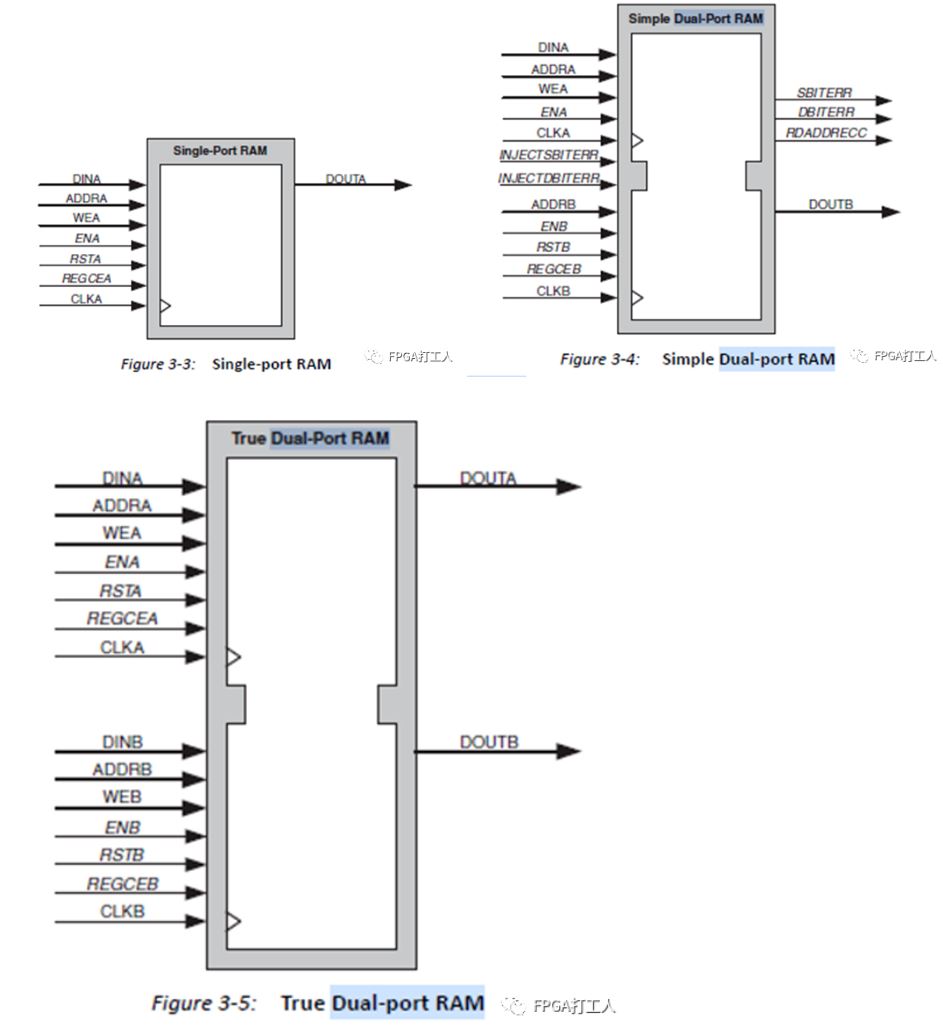

Block_RAM应该是每个FPGA开发者经常遇到的,其作为一种固定资源存在于FPGA中,针对xilinx的BRAM,正常通过vivado的IP Core Generator得到,如果批量需要生成的话,可以通过运行tcl脚本得到,之前也是因为项目需要才编写了这个tcl脚本。BRAM有三种:单口RAM,简化双口RAM和真双口RAM。

该tcl脚本三种RAM都支持,当然,这个仅供参考,里面几个设置可能还需要根据具体项目细节性调整。

首先就是顶层几个参数的说明

set mem_ip "SRAM_1P_FPGA_128X8X4"

#set mem_ip "SRAM_2P_FPGA_768X8X4"

#set mem_ip "SRAM_DP_FPGA_768X8X4"

set mem_addr ./

file mkdir $mem_addr

mem_ip是对应的生成IP的name,mem_addr是对应IP存放的路径。这里注意的是,name中的1P、2P、DP分别对应单口RAM,简化双口RAM和真双口RAM。

其次就是深度和数据位宽的获取

set Mem_Select [string range $mem_ip 0 11]

set Mem_Parater [string range $mem_ip 13 end]

scan $Mem_Parater "%dX%dX%d" Depth Byte Width

set Write_Width [expr $Byte*$Width]

下面简单以单口RAM的配置为例

if { $Mem_Select == "SRAM_1P_FPGA"} {

if { $Byte == 8} {

set_property CONFIG.Use_Byte_Write_Enable true [get_ips $mem_ip]

set_property CONFIG.Byte_Size 8 [get_ips $mem_ip]

} elseif { $Byte == 9} {

set_property CONFIG.Use_Byte_Write_Enable true [get_ips $mem_ip]

set_property CONFIG.Byte_Size 9 [get_ips $mem_ip]

}

set_property CONFIG.Write_Width_A $Write_Width [get_ips $mem_ip]

set_property CONFIG.Write_Width_B $Write_Width [get_ips $mem_ip]

set_property CONFIG.Read_Width_A $Write_Width [get_ips $mem_ip]

set_property CONFIG.Read_Width_B $Write_Width [get_ips $mem_ip]

set_property CONFIG.Write_Depth_A $Depth [get_ips $mem_ip]

set_property CONFIG.Register_PortA_Output_of_Memory_Primitives false [get_ips $mem_ip]

}

后面详细的tcl获取可以在后台回复“BRAM_IP”。