本文转载自:FPGA技术实战博客

注:本文由作者授权转发,如需转载请联系作者本人

引言:从本文开始我们介绍Xilinx 7系列FPGA的SelectIO资源结构及使用,我们在进行FPGA外设硬件及软件设计时,如ADC、PHY、DDR3等,通常会涉及到该资源。本节我们介绍以下知识点:

1.I/O概述

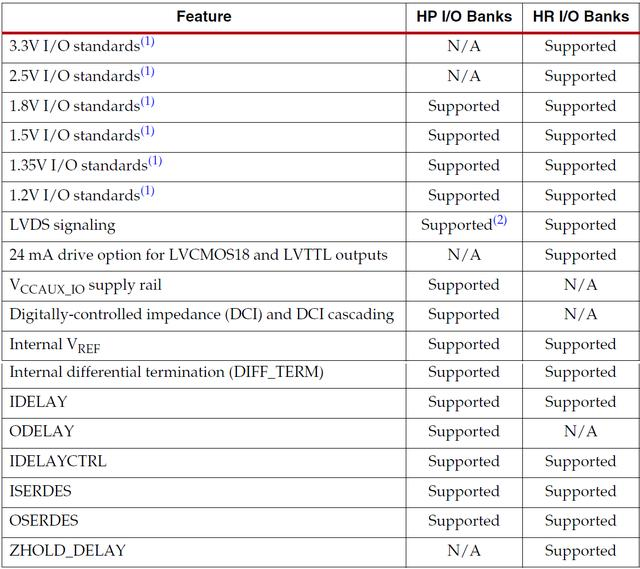

7系列FPGA I/O bank分为高性能(HP)banks和宽范围(HR)banks。HP I/O banks可以实现高性能存储器接口或者芯片间高速接口,支持电压最大1.8V,HR I/O banks支持更宽范围的I/O电平标准,最大支持3.3V。这两种I/O banks支持的I/O特性如图1所示。

图1、HR和HP I/O banks支持的特性

注意:

并不是所有的I/O标准和电流驱动强度在HP和HR I/O banks都支持。

尽管LVDS一般认为是2.5V I/O标准,但是在HR和HP I/O banks中都支持。

2.SelectIO资源介绍

所有的7系列FPGA具有可配置的SelectIO驱动器和接收器,支持宽范围的可变标准接口,支持可编程输出电流,边沿速率,DCI片上端接和内部产生参考电压(INTERNAL_VREF)。

图2、可配置I/O参数

注意:HR banks没有DCI,因此任何需要参考DCI的应用不能使用HR banks。

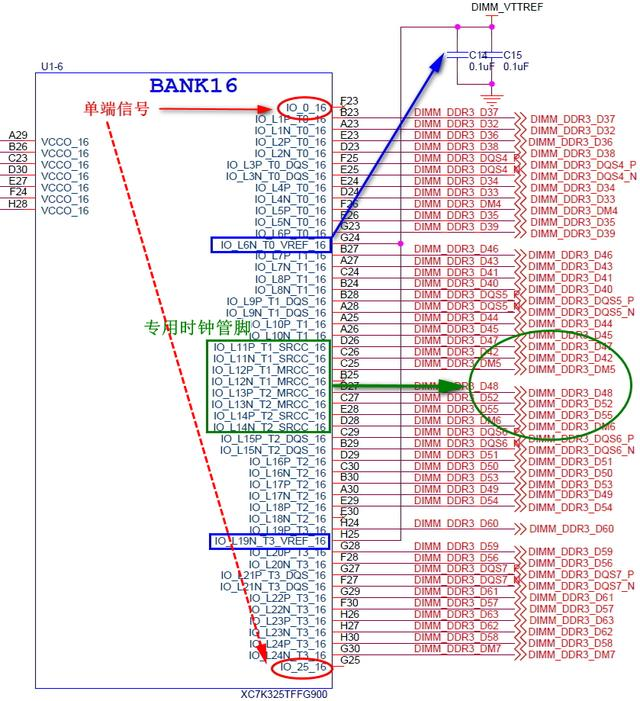

除了某些例外,每个I/O bank包含50个SelectIO管脚。在每个bank的末端有两个只能用作单端I/O使用的管脚,剩余48个管脚可以用作48个单端I/O或者24对差分I/O。每个SelectIO可以配置为输入、输出或者三态驱动。

图3、I/O bank管脚

SelectIO管脚可以配置为单端和差分信号:

单端I/O标准(例如LVCMOS、LVTTL、HSTL、PCI和SSTL)

差分I/O标准(例如,Mini_LVDS、RSDS、PPDS、BLVDS和差分HSTL和SSTL)

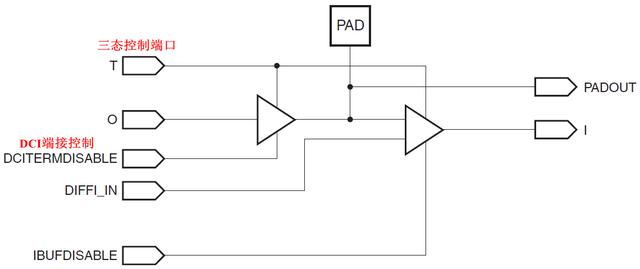

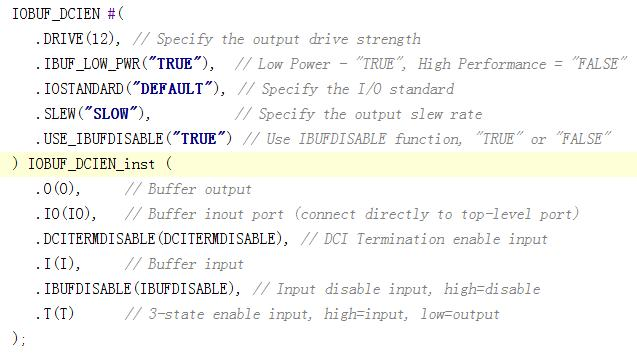

图4显示了HP bank只能配置为单端信号的IOB内部逻辑和器件管脚(PAD)连接,其对应的原句如图5所示。

图4、只能作为单端管脚的HP IOB结构

图5、单端HP IOB原句

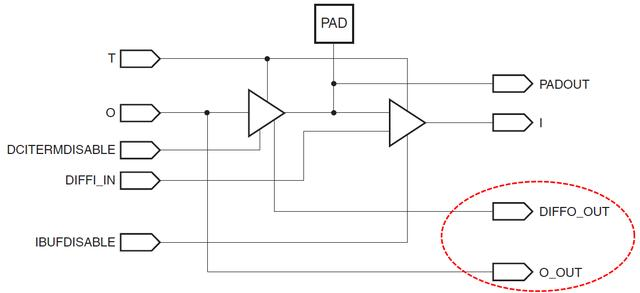

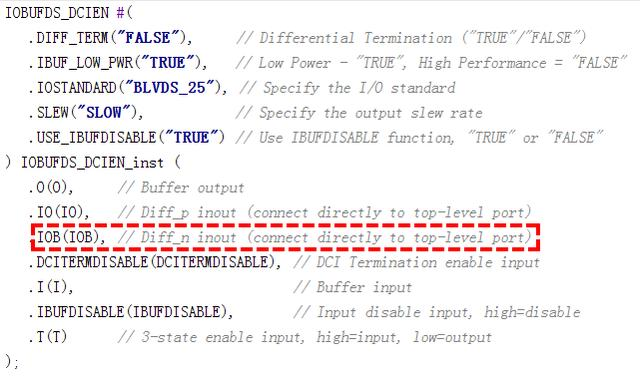

图6位常规HP IOB结构框图,该类型管脚可以配置为单端或者差分信号,其原句如图7所示。

图6、常规HP IOB结构框图

图7、常规HP IOB原句

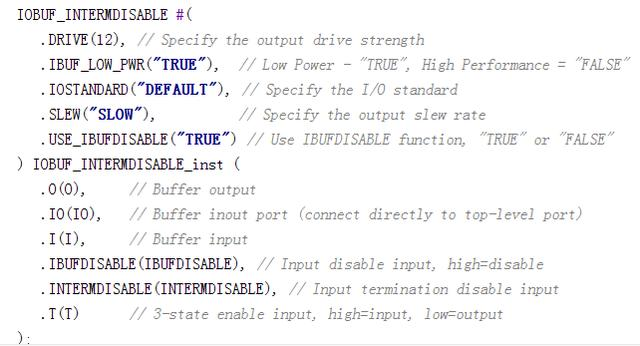

图8为只能作为单端管脚的HR IOB结构框图,图9为其对应的原句。

图8、只能作为单端管脚的HR IOB结构

图9、只能作为单端管脚的HR IOB原句

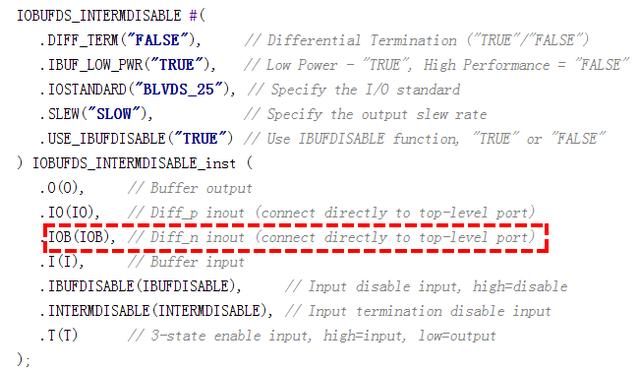

图10为常规HR IOB结构框图,图11为其对应的原句。

图10、常规HR IOB结构框图

图11、 HR IOB原句

3.SelectIO资源通用设计指导

3.1 7系列FPGA I/O Bank规则

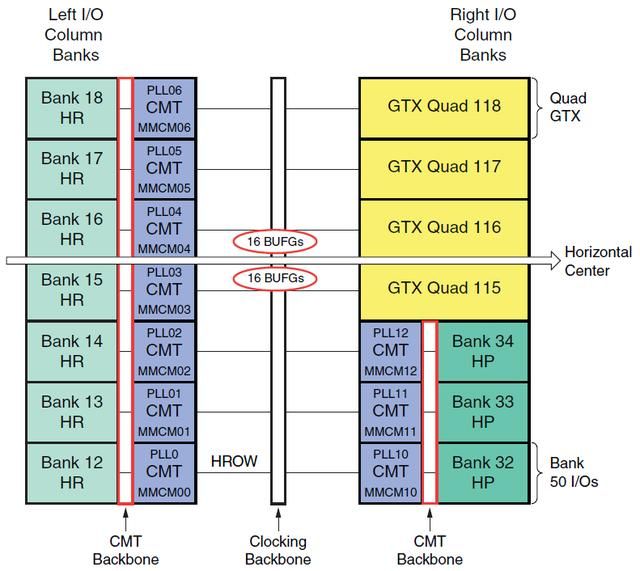

在7系列FPGA器件中,每个I/O bank包括50个IOB资源,Bank的数量和器件大小和封装管脚有关。例如XC7K325T有10个可用的I/O banks,如图12所示。

图12、XC7K325T I/O Banks

3.2 SelectIO管脚供电电压

Vcco电压管脚: Vcco供电是7系列I/O电路主要的电压,位于同一bank内的所有Vcco电源管脚必须连接到相同的外部电压,故同一个bank内的所有I/O管脚必须共享Vcco电平。Vcco电压必须匹配I/O电平标准要求,如果不匹配可能会造成器件I/O损坏。

在HP I/O bank中,如果I/O标准电压要求≤1.8V,但是如果Vcco≥2.5V,则FPGA器件自动进入过压保护模式,重新配置正确的Vcco电平,器件自动恢复正常模式。

VREF: 单端I/O标准使用差分输入缓冲会要求一个参考输入电压(VREF),这种标准信号称为伪差分信号,如DDR2/3使用的差分SSTL电平标准。当在I/O bank中,VREF电压需要时,此时该类型管脚需要当作电源管脚使用,在图3中,我们可以看到这一点。7系列FPGA可以使用芯片内部产生的参考电压,此时需要使能INTERNAL_VERF约束。

Vccaux: 全局辅助电压Vccaux电源轨主要为7系列FPGA内部各种逻辑资源模块提供电源,如BRAM资源,Vccaux也为某些I/O标准输入缓冲电路提供供电。

Vccaux_io: 该管脚只为HP I/O bank电路提供辅助电压。该管脚电压应用于K7和V7系列FPGA,提供1.8V和2.0V两种供电电压选择,该管脚电压与存储器接口频率有关,其中2.0V电压支持更高频率存储器接口。如果Vccaux_io设置为2.0V电压,此时需要对VCCAXU_IO添加约束。

3.3 配置期间和配置后I/O状态

7系列FPGA在I/O bank0中有专用的配置功能管脚,Bank14和Bank15也包含多功能管脚用于配置功能,在配置完成后可以用作普通I/O。