本文转载自: FPGA打工人微信公众号

注:本文由作者授权转发,如需转载请联系作者本人

Vivado HLS概述

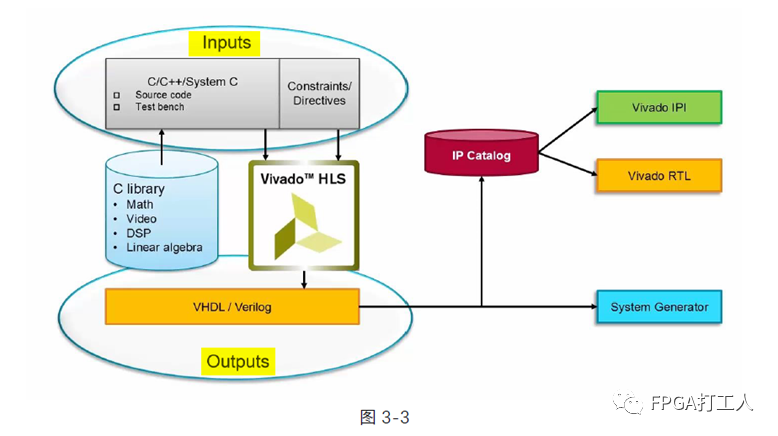

HLS现在应该算是比较成熟了,其最大的吸引力就是可以采用纯C/C++或者System C来对FPGA进行编程,相对于VHDL和Verilog更加容易上手。再一个就是采用基于模型的方法—System Generator。但这也需要开发者在C/C++层面把算法做更多的优化,以及对综合工具采用相应的directives。

C/C++/System C、Test bench以及Constraints/Directives构成了HLS的输入,HLS还提供了一些library,HLS的输出是VHDL/Verilog代码。在正常使用时,会将输出封装为一个IP。

其中的Test Bench文件起到自我检测的作用,通俗理解就是仿真,看仿真结果是否是自己想要的结果。在实际操作流程中,步骤依次为:C的仿真、C的综合、C和RTL的协同仿真、导出RTL,每个步骤都有专门的文件夹存放非所需的文件和生成的文件。

在完成C综合后可以查看相应的报告查看相应的性能评估、资源利用率的评估以及接口和时序的信息,在完成协同仿真后还可以查看RTL的仿真波形,以直观的方式查看输入输出端口之间的时序关系。

每个工程可以有不同的Slolution,里面包含了不同的Directives,这些Directives是用来优化C综合的,还有另一种选择,就是把Directives直接写在C/C++的源码中。

总体来说,HLS可以完成部分以前需要手动完成的工作,具体如下:

基本实现Flow

先来个具体实现Flow,后面再展开说说。

明确需求

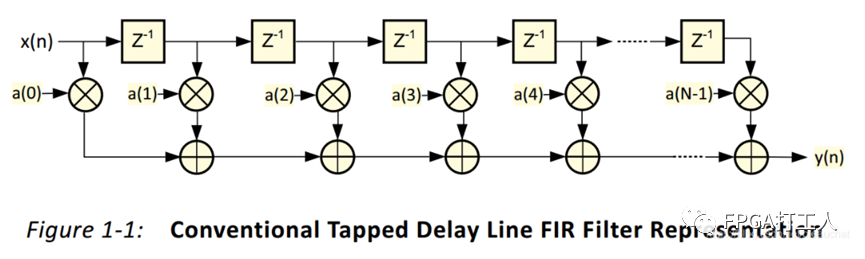

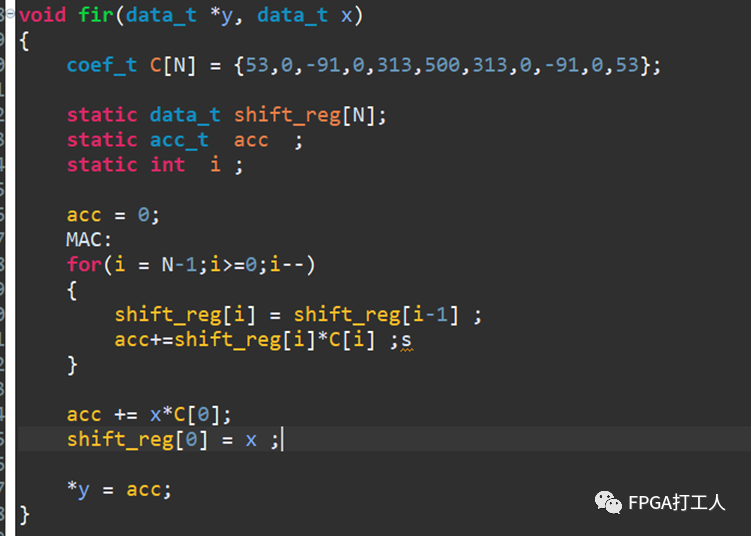

以实现一个11阶fir滤波器为例。要计算一个N阶滤波器的输出值,需要N个乘法和N-1个加法。

fir滤波器函数有两个输入端口,一个端口是输入数据x和另一个端口是输出结果y。由于每次执行该函数会提供一个函数输入数据并接收一个函数输出数据,多次调用这个函数后,完成整个输出信号的计算。

滤波器系数存储在函数内部声明的数组c[]中,定义为静态常数。注意系数是对称的。可以利用这个特点来减少数组c[]所需的存储容量。

Project创建及代码实现

点击Create Project后会进入如下界面,修改工程name及路径。

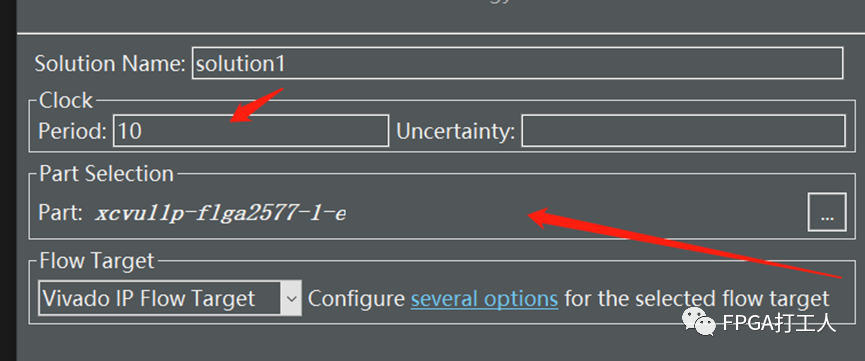

之后next进入如下界面,第一个箭头用来修改所需时钟频率,第二个用来修改FPGA型号。之后点击finish。

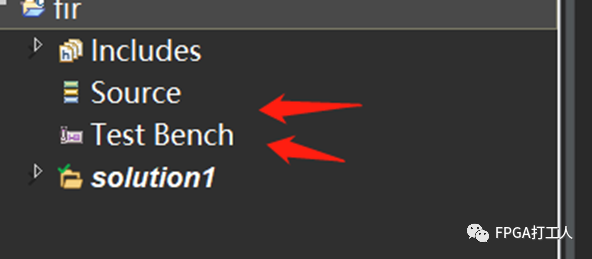

进入work界面,Source下为fir函数代码文件,Test Bench下为C仿真文件,实际上可以理解为C/C++的主函数。

代码实现:

优化

最后得到的结果实际上由两部分决定,一部分是code实现,另一部分就是优化命令,这个后面会有一个详细介绍。

仿真

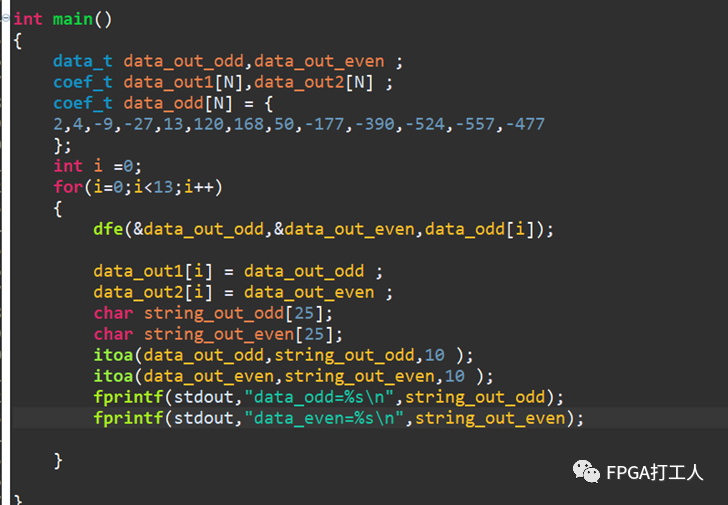

在Test Bench下创建仿真文件主函数,下面以后面Demo用到的仿真文件为例说明:fprintf可以通过打印将仿真结果打印出来。

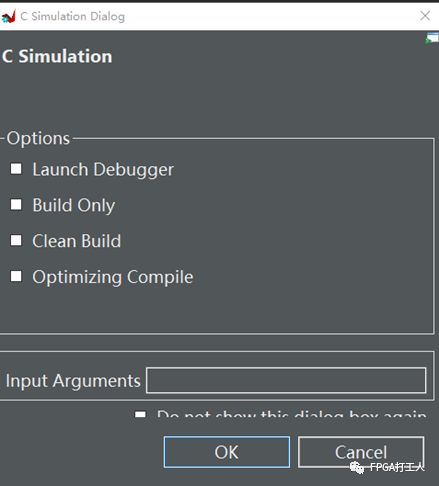

具体编译选择Project->Run C simulation,之后会出现下面的操作,如果想看每一步Debug,可以勾选Launch Debugger。

IP导出

点击Solution->Export RTL会出现如下界面,此界面主要为生成IP的一些基本设置。生成OK后可以在vivado环境下像调用其他IP方式一样使用。