本文转载自:十年老鸟的CSDN博客

注:本文由作者授权转发,如需转载请联系作者本人

时钟架构

设计中采用如下图所示时钟设计图,主要是refclk和coreclk分开的

图 3-1 显示了最通用和最灵活的时钟方案,其中使用单独的 refclk 和 glblclk 输入分别提供收发器参考时钟和内核时钟。 通过这种配置,参考时钟和内核时钟是物理上独立的时钟,可以在独立的频率下运行,没有额外的限制。 参考时钟可以在收发器限制范围内的任何频率运行,以选择线路速率。 内核时钟始终以所需的速率运行(串行线路速率的 1/40)

Reference Clock ——给JESDPHY的参考时钟 —— JESD204_PHY 中的 GTP/GTX/GTH/GTY 串行收发器需要稳定、低抖动的参考时钟,该参考时钟具有与器件和速度等级相关的范围。 在某些情况下,为内核时钟和参考时钟使用相同的时钟频率或源可能是有利的。 然而,这可能并不总是实用的。 了解对参考时钟和内核时钟施加的限制以及系统级含义(例如 SYSREF/SYNC 的同步捕获以实现子类 1 或 2 确定性延迟)非常重要。

Coreclk ——JESD204 内核使用 32 位(4 字节)数据路径运行。 核心时钟频率始终是线路速率除以 40。例如,对于 6.25 Gbs 的串行线路速率,核心时钟频率为 156.25 MHz。 AXI 流 RX 和 TX 数据接口在此内核时钟频率下运行

AXI4-Lite Interface Clock ——内核通过 AXI4-Lite 处理器接口进行配置和监控。 此接口的时钟是独立于内核时钟或参考时钟的时钟。 该时钟与核心时钟或参考时钟之间没有任何依赖关系

Drp_clk ——DRP 时钟。 基于 UltraScale 架构的设备需要一个自由运行的 DRP 时钟,这个时钟可以和AXI4-Lite接口时钟使用同一个

在JESDPHY的模块中

同时输入了Refclk 和core_clk,说明JESDPHY与JESD 204B CORE之间的数据交互都是在core_clk的时钟域下,JESDPHY内部已经做好了serdes内部时钟和core_clk的时钟域转换

Subclass 1

子类 1 通过使用公共 SYSREF 信号支持确定性延迟。 SYSREF 信号在内核外部生成,并分配给系统中的所有设备。 JESD204B 标准允许 SYSREF 为“一次性”、周期性或间隙周期性。 内核能够使用这些选择中的任何一个进行操作。 可靠捕获 SYSREF 的时序和时钟要求是实现可靠确定性延迟的关键

SYSREF Sampling Clock Edge

SYSREF的采样边沿选用上升沿和下降沿也是有讲究的。

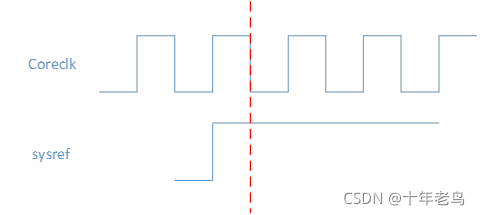

IP核可以配置是coreclk的上升沿采样sysref还是下降沿采样sysref。默认的设置是下降沿采样,这是基于SYSREF和给到core的时钟是同步的假设。因此在IO管脚处SYSREF和CORECLK的上升沿是对齐的。且一般sysref是源时钟的分频。因此下降沿提供了最好的时序余量。

在我们的设计中,sysref都是coreclk进行分频产生的,那么下降沿采样肯定是必选的了

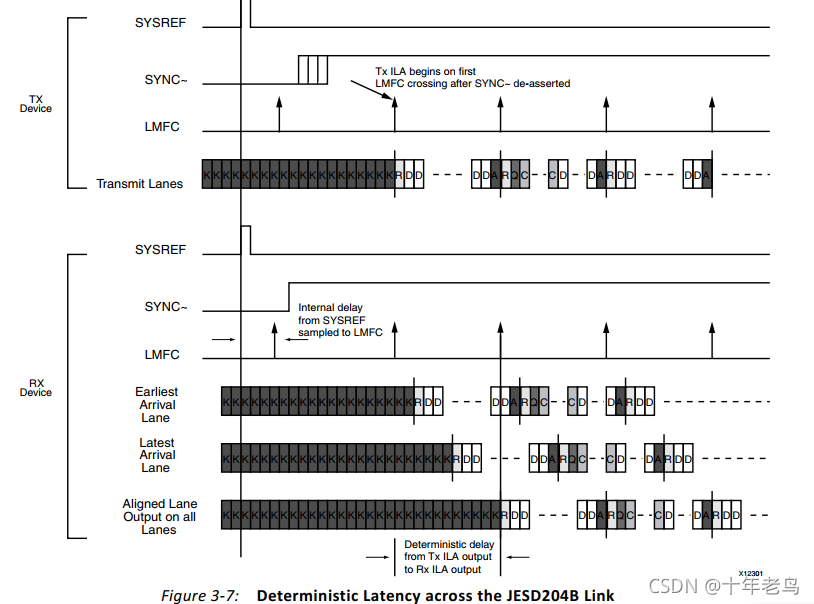

确定性时延

确定性时延时怎么来的,先要理解下面这张图。

SYSREF:作为Tx Device和Rx Device共用的参考信号,用于产生LMFC(Local Multiframe Clock)信号(我觉得与其说它是一个CLOCK,不如说它是一个脉冲合适)。

实际上是有一个LMFC的计数器。这个计数器在检测SYSREF的边沿(上升沿或者下降沿,我们这里是下降沿)对LMFC进行复位,如果2 octets一个帧(F = 2),16帧一个多帧(M = 16),那么则32(MF)个octets一个多帧,一个多帧定义为32个octets,那么LMFC计数器则会在0-7之间循环计数(5 core_clk cycles - 20 octets; 8clk – 32 octets)。每次记一个周期时,LMFC则会产生一个脉冲。

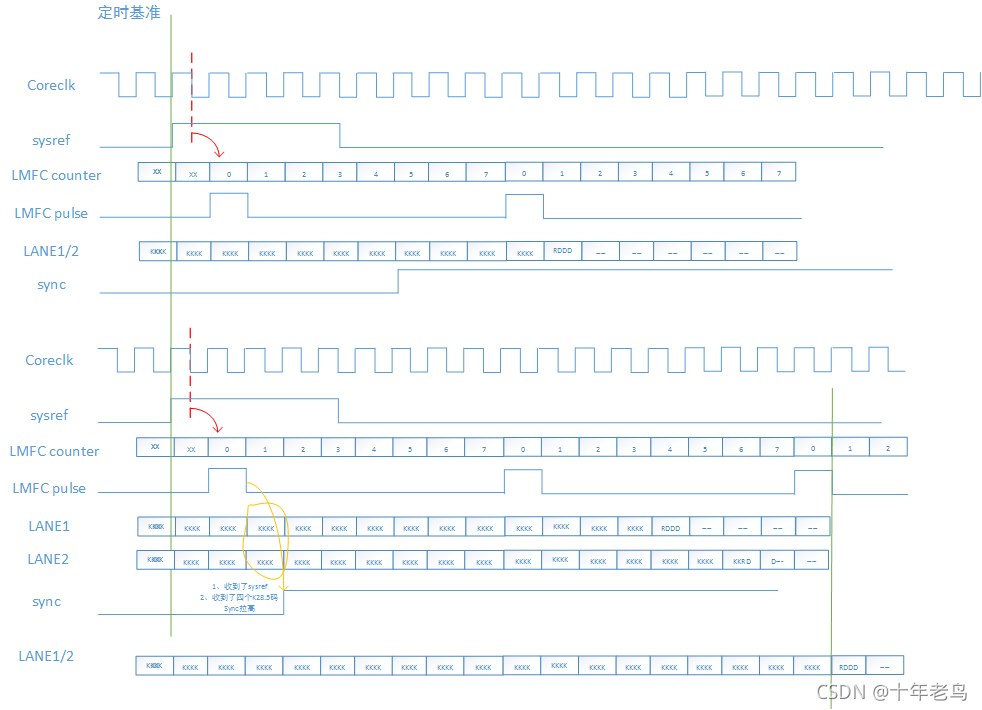

下面我为了增强理解重新画了一遍上图

1、我们假设sysref到接收和发射端距离是一样的,那么收发两端的LMFC counter和pulse相差不大。(左绿线)

2、同时我们假设LANE1的线短,LANE2的线长,那么LANE1的数据先于LANE2到达(接收端LANE1率先出现了R字符)

3、因为接收端每个有RX BUFFER,只要这个BUFFER的容量大于两条LANE线长的差即可补偿线距离不同造成的时延不同

4、两个LANE都已经接收到R的情况下,有LMFC触发,两个LANE的buffer同时从R处释放数据(右绿线)

5、LMFC counter实际时序不一定如我所画的,但大致应该就是这个意思,可以作为理解用

6、LANE1延迟了20字节,LANE2延迟了10个字节,这就是2个lane的确定性时延,每次上电将都是这样。通过接收SYSREF位置的调整(SYSREF DELAY),可以减小两个lane的确定性时延

SYSREF Delay

JESD204B 标准中定义的确定性延迟机制要求多帧大小大于链路上的最大可能延迟。 在实践中,这很难实现,特别是对于帧比较小的情况。 但是,只要多帧大小大于链路上延迟的最大变化,就可以实现确定性延迟

当最大延迟变化导致整体延迟跨越两个相邻 LMFC 周期之间的边界时,就会出现潜在问题。 在这种情况下,可以在系统重新启动之间观察到恰好一个 LMFC 周期的延迟变化。 应计算整体系统延迟(请参阅 RX 端到端延迟或 TX 端到端延迟)以确定这是否是可能的情况。

在出现这种情况的情况下,TX 或 RX 设备中的 LMFC 边界可以通过向其中一个设备中的 SYSREF 添加额外延迟来相对于彼此移动。 Xilinx JESD204 内核通过允许内部 SYSREF 处理逻辑中的额外延迟来支持内部 LMFC 的这种移位。 这是使用 SYSREF 处理寄存器中的 SYSREF 延迟字段编程的,允许在 SYSREF 事件检测和 LMFC 计数器复位之间插入 0 到 15 个内核时钟周期的延迟。 SYSREF 延迟值的变化需要内核复位以强制链路重新对齐