本文转载自:十年老鸟的CSDN博客

注:本文由作者授权转发,如需转载请联系作者本人

Tb看完了,那我们需要对example 进行改造才能进行上板调试。

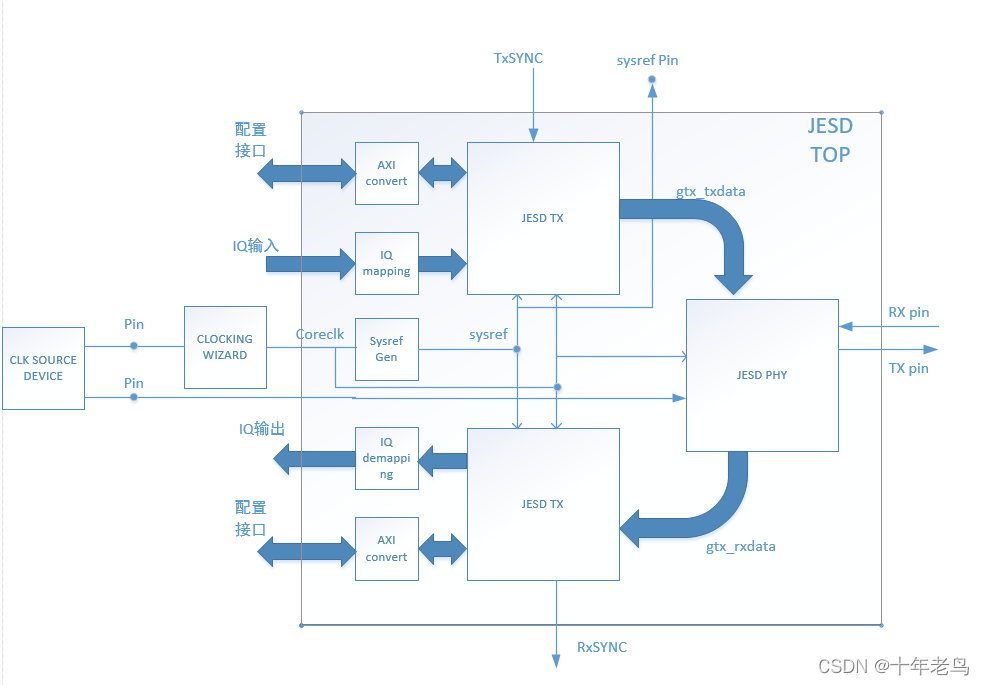

很明显,作为一个ADC和DAC接口,我们需要构建一个顶层模块

1、 IQ输入,作为DAC的数据源

2、 IQ输出,作为ADC采集的数据

3、 AXI总线,用于对IP核的配置

4、 几个复位线,对phy 和axi进行复位用

5、 时钟

6、 与FPGA外部JESD器件接口 【高速接口管脚/SYSREF/参考时钟/SYNC标志等】

4T4R 4lane采样率 245.76Mbps 9.8304G的速率

JESD CORE 数据的位宽为32bit,正好一个lane覆盖一个 {I,Q}

AXI convert : JESD CORE 使用的是AXI接口,除非直接与ZYNQ SOC直连,否则需要进行协议转换才好进行操作

IQ MAPPING/DEMAPPING: IQ数据的摆放设置,随芯片设置有关,有可能要设置IQ高低位,大小端等

SYSREF GEN: 这个模块用于生成SYSREF,给到JESD CORE和外面的JESD芯片,内部产生可以用CORECLK进行。这个SYSREF也可以外部管脚输入。

JESD RXTX JESD IP核

JESD PHY核

1、如何判断建链: tx_tvalid tx_sync 和 rx_tvalid rx_sync 都拉高了,则FPGA端正常

同时如果外部芯片支持指令查询的话,也要查询一下其建链标志,

两边互相确认建链,则无问题

2、jesd phy 有一个 gtx_loopback_in 端口,用作配置RXTX高速接口环回的作用,当上板调试出问题的时候会有作用。也用于最开始上板调试时自己还回看是否能自己建链,数据是否正常

3、预加重参数

.gtx_txpostcursor_in

.gtx_txprecursor_in

.gtx_txdiffctrl_in

当判断信号质量不佳的时候,可以调这些参数,在调这些参数之前,建立ibert眼图进行扫描

建链不稳定是一个棘手的问题,尤其是高低温环境下,需要有一些经验才能快速定位问题。