本文转载自:孤独的单刀的CSDN博客

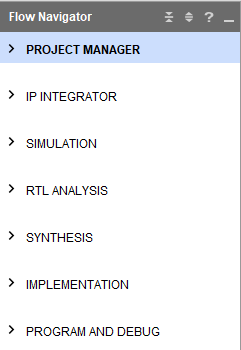

1、一般流程

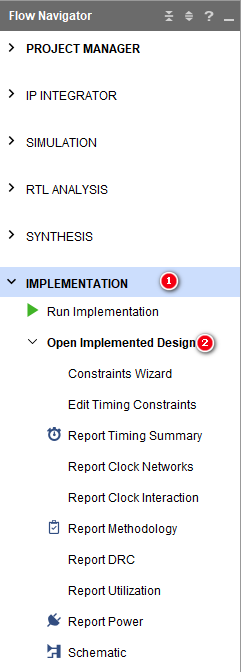

Xilinx 的开发工具Vivado其实还是比较好上手的,在左边的设计流程导航已经把FPGA的开发过程按先后顺序给排列出来了:

Project Manager:项目管理器,此项是对项目的参数进行设置

IP Integrator:IP集成器,此项是对IP的操作

Simulation:仿真,包括功能仿真、综合后仿真和实现后仿真

RTL Analysis:RTL分析,将用户的设计输入细化成逻辑电路,也就是常说的RTL电路

Synthesis:综合,类似于软件编程中的编译,是一个把RTL电路用FPGA内资源实现的过程,会生成综合网表

Implementation:实现,把综合网表具体实现的过程,可以理解为将综合后的电路具体映射到FPGA内部资源的过程

Program and Debug:下载和调试,将最终实现的电路生成BIT文件(或其他格式的文件),可下载进FPGA板卡中,还可以在这个环节进行调试debug

理论上,FPGA从编程到下载实现预期功能的过程最少仅需要上述7个步骤中的4、5、6和7,即RTL分析、综合、实现和下载。其中的RTL分析、综合、实现的具体含义和区别又是什么?

2、RTL分析(RTL analysis)

一般来讲,通常的设计输入都是Verilog、VHDL或者System Verilog等硬件描述语言HDL编写的文件,RTL分析这一步就是将HDL语言转化成逻辑电路图的过程。比如HDL语言描述的计数器转化成对应的逻辑电路,又或者下例中的HDL语言描述的加法器转化成对应的逻辑电路。

假设要实现简单的加法器----2个8bit输入的加法,不考虑进位,即输出同样为8bit。根据需求可以很容易地写出代码:

module test( input [7:0] in1, input [7:0] in2, output [7:0] out ); assign out = in1 + in2; //简单加法器 endmodule

这个代码的核心只有一句,就是用一个assign语句将两个输入相加。这一语句转化成逻辑电路,很明显就是一个加法器。

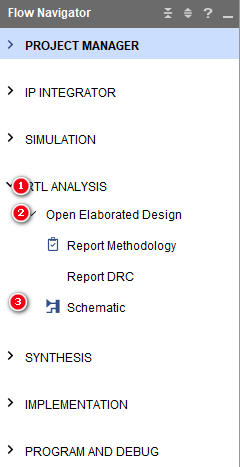

光说不练云玩家,接下来添加测试工程,并把该文件保存后,按下图顺序点击:

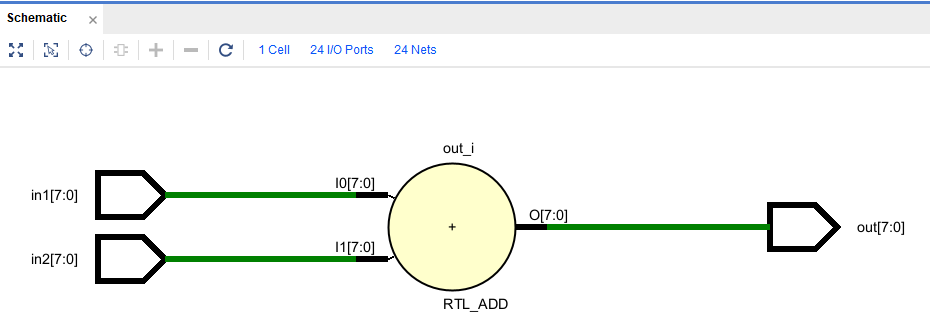

可以看到RTL分析后的电路:

和预期的一致吧?就是一个2输入8bit的加法器。

3、综合(synthesis)

综合是指将高级抽象层次的语言描述转化成较低层次的电路结构,也就是说将硬件描述语言描述的电路逻辑转化成查找表LUT、触发器等FPGA内部存在的基本逻辑单元的互连关系,也就是我们常说的综合网表。

比如上面的例子,RTL分析后的电路是一个2输入8bit的加法器,那么综合后的电路是什么样子呢?按下图顺序点击:

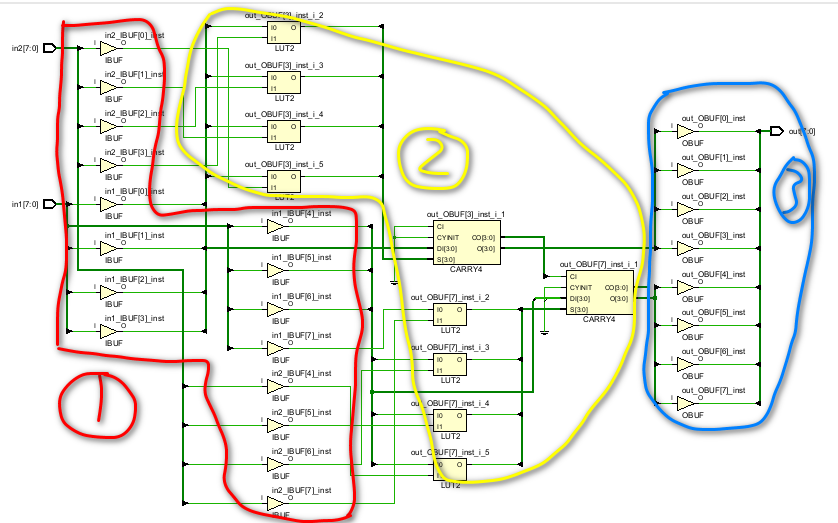

可以看到综合后的电路是这样的:

好家伙,出来一大堆乱七八糟的,这跟RTL电路完全不一样呀?这些玩意都是啥?

2个输入端口的8+8 共16个IBUF,是FPGA的IO口默认添加的输入缓冲,这个更多是为了电气方面的考量,和逻辑关系不大

8个LUT2 + 2个CARRY4,这都是FPGA底层的逻辑资源,用来实现各种组合逻辑功能

1个输出端口的8个OBUF,是FPGA的IO口默认添加的输出缓冲,

那么,为什么RTL电路和综合后的电路有如此大的区别?因为RTL电路是把HDL转化成逻辑电路,而综合后的电路则是用FPGA内部的逻辑资源来实现。所以最直接的原因就是FPGA底层没有加法器这个东西,只能用其他逻辑资源来实现加法器的功能。

4、实现(implementation)

综合后生成的综合网表只是表示了逻辑资源之间虚拟的连接关系,并没有规定每个逻辑资源位置以及连线长度等。实现就是一个将综合网表中的逻辑资源位置以及连线长度确定的过程。

比如上例中,综合后的电路由8个lut2 + 2个CARRY4 + 24个IOB组成,但是FPGA内部的LUT、CARRY4和IOB的数量远不止这些,所以需要根据用户设定的策略(面积优化、速度优化)来找到具体的逻辑资源。

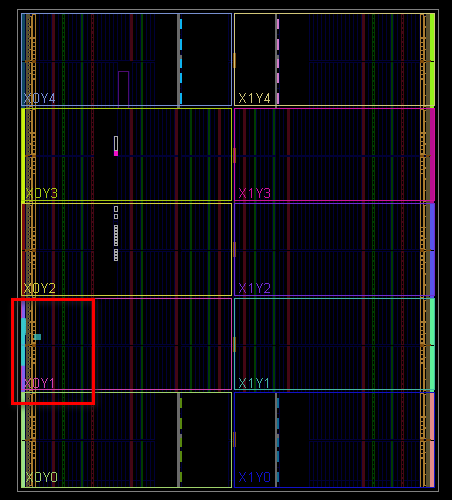

那么实现后的电路是什么样子呢?按下图顺序点击:

此时,看到的是整个FPGA芯片的资源使用详情:

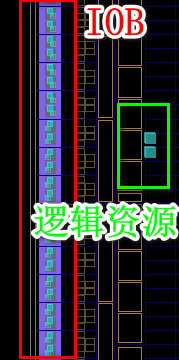

把高亮的部分放大观察:

左侧是具体的24个IOB,这是在左列数百个IOB中根据实现策略找到的具体解;右边则是具体的逻辑资源LUT+CARRY4,这是在数万个逻辑资源中找到的具体解。

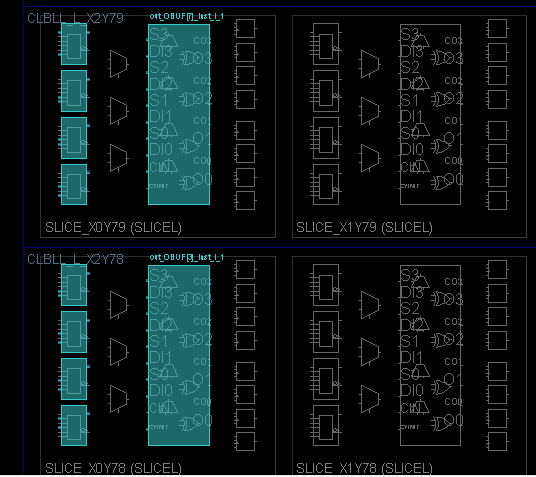

具体使用到的逻辑资源则是编号为CLBLL_L_X2Y79中编号为SLICE_X0Y79中的4个LUT6+1个CARRY4 和 CLBLL_L_X2Y78中编号为SLICE_X0Y78中的4个LUT6+1个CARRY4 。

我经常说的一句话是:FPGA其实就是些积木。如果你想要个足球,那我就用很多个球形模块来拼;如果你想要把枪,那我就用很多个矩形模块+三角形模块来拼。

假设你想用积木(FPGA)拼个变形金刚(目标设计),那么写HDL的过程大致就是:输入=若干积木,输出=变形金刚,中间则是用语言来描述这个变形金刚的样子,比如长25米,宽15米等;RTL电路图呢,则是将HDL转化成一张变形金刚的图纸;综合则是计算具体要用多少个矩形模块、多少个三角形模块、多少个球形模块来拼成变形金刚的过程;而实现则是,确定了矩形模块、三角形模块、球形模块的数量后,到你的积木堆里找到具体的模块的过程(毕竟你的积木堆里的模块数量远远不止是只能拼一个变形金刚不是)。