本文转载自:FPGA技术实战的CSDN博客

引言:串行收发器中的均衡器在接收中补偿线路高频信号衰减,减少误码率,增大信号眼图显示等方面具有重要作用。采样时钟随数据一起传输,在接收端通过CDR电路恢复时钟,极大的提高了数据传输速率。本文我们一起了解下GTX/GTH收发器中这两种资源的结构和使用方法:

GTX/GTH收发器RX均衡器

GTX/GTH收发器CDR时钟恢复电路

1.RX均衡器(DFE和LPM)

1.1功能描述

串行链路比特误码率(BER)性能是发送器、传输媒介和接收器的一个功能。传输媒介是带宽受限的,通过它的信号会衰减和失真。均衡器主要用于补偿由于频率不同而引起的阻抗或者衰减差异。

对于GTX/GTH收发器,基于系统级的功耗和性能的权衡,有两种类型的自适应滤波可用:

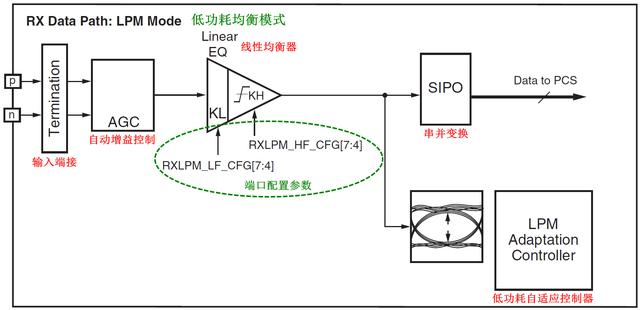

功耗优化和低通道损耗的低功耗模式(LPM)

均衡更低损耗通道的判决反馈均衡模式(DFE)

图1、LPM模式

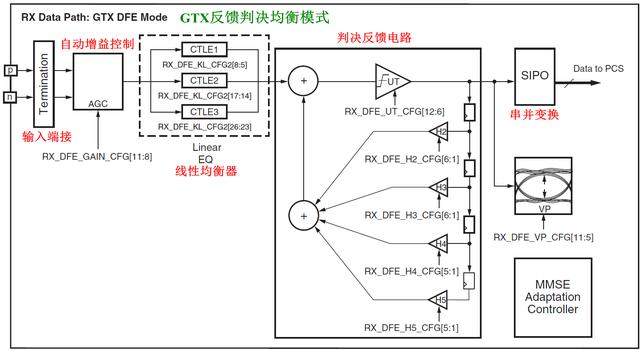

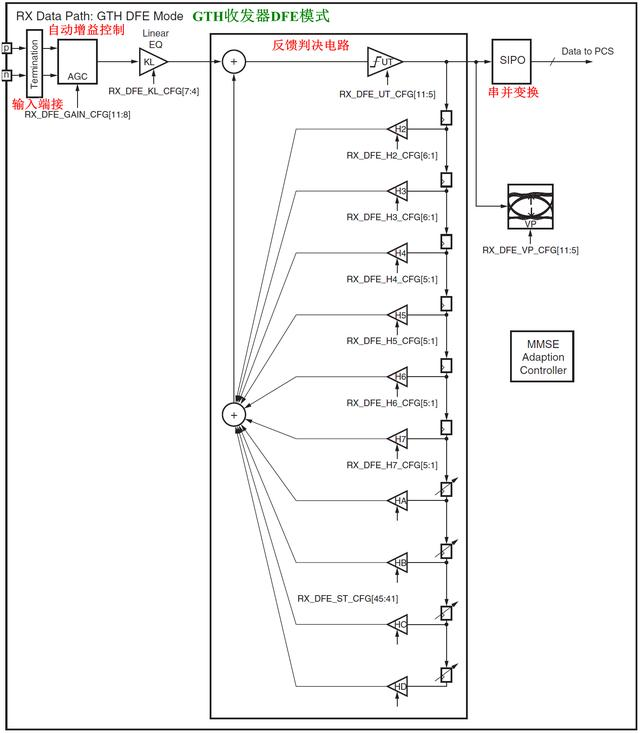

DFE模式通过提供更接近的调整滤波器参数,提供更好的传输通道补偿。但是,DFE模式不能移除发送比特的pre-cursor,只能补偿post-cursor。线性均衡器允许pre-cursor和post-cursor增益。GTX/GTH RX DFE模式是一个离散时间自适应高通滤波器,该滤波器系数TAP由自适应算法设置。

图2、GTX收发器DFE模式

图3、GTH收发器DFE模式

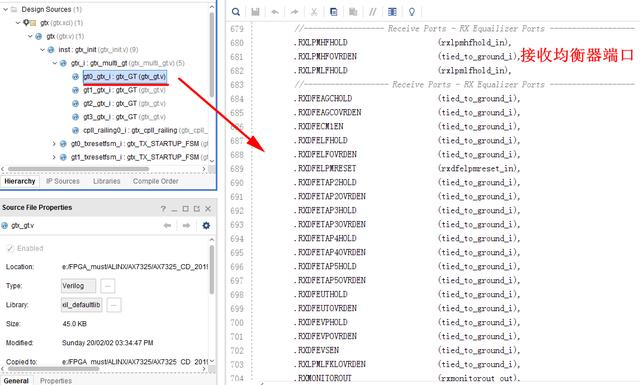

图4、GTX收发器RX均衡器配置选择

1.LPM和DFE模式选择

对于线速率高达11.2 Gb/s的短距离应用,建议使用LPM模式,在Nyquist频率下,信道损耗为12 dB或更小。

DFE模式推荐用于中长距离应用,在奈奎斯特频率下的信道损耗为8dB或者以上。DFE具有均衡信道而不放大噪声和串扰的优点。DFE还可以纠正由GTX收发器中通道不连续引起的反射。当串扰是一个问题或在单比特响应分析中识别反射时,DFE模式是最佳选择。

在8B/10B应用中或不使用数据加扰的情况下,必须仔细考虑DFE模式。为了正确地适应数据,DFE模式下的自动适应要求输入数据是随机的。

2.LPM模式使用

GTX LPM和DFE模式使用不同的CTLE块,另外,GTX收发器中,CTLE块在LPM模式下自动消除基线漂移,无需用户干预。LPM模式选择通过设置RXLPMEN端口为1’b1。

3.DFE模式使用

DFE模式利用AGC、CTLE、DFE和基线消除器来均衡通道的影响。DFE模式选择通过设置RXLPMEN端口为1’b0。

图5、RX均衡器端口

每个GTXE2_CHANNEL/GTHE2_CHANNEL收发器接收时钟恢复电路从输入的数据流中提取出恢复时钟。图6举例了CDR模块结构。

图6、CDR模块结构

GTX/GTH收发器采用相位旋转CDR结构。输入数据首先经过接收器均衡阶段,均衡后的数据由边沿采样器和数据采样器捕获。数据采样器捕获的数据被馈送至CDR状态机和下游收发器模块。

CDR状态机使用来自边缘和数据采样器的数据来确定传入数据流的相位并控制相位插值器(PIs)。边缘采样器的相位锁定在数据流的过渡区域,而数据采样器的相位则位于数据眼的中间。

图7、CDR采样器位置

CPLL或QPLL为相位内插器提供基准时钟。相位内插器依次产生精细的、均匀分布的采样相位,以允许CDR状态机具有精细的相位控制。CDR状态机可以跟踪传入的数据流,这些数据流可以与本地PLL参考时钟存在频率偏移。

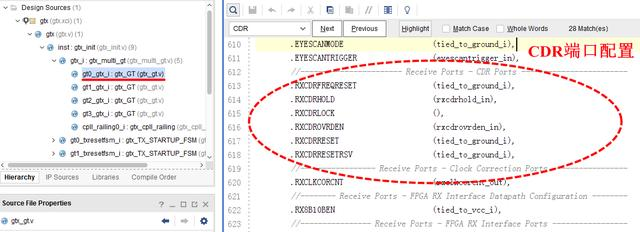

图7、CDR时钟恢复端口配置

图7显示了GTXE2_CHANNEL通道源码中CDR时钟恢复配置端口。