本文转载自:Vuko-wxh的CSDN博客

前言

RFSoC中最重要的部分是射频直采ADC和DAC的配置,因此了解内部相关原理结构可以帮助我们更好理解相关功能配置参数含义。本文参考官方手册,主要对高采样率模式、多频带操作以及IP的数据接口进行介绍。

RF-DAC 高采样率模式(第 3 代)

为了提高采样率,可以使用以下两种配置:

1. 绕过 DUC:RF-DAC 工作在 Real to Real 模式。 这种配置实现了最大指定和全带宽的采样率,但没有 DUC 功能(插值、混频器、多频带、QMC)。

2. 启用 DUC:必须启用 DUC 之后的附加图像抑制 (IMR) 插值滤波器阶段。 这将数据速率限制为在 IMR 插值滤波器之前为 IMR 模式指定的速率。

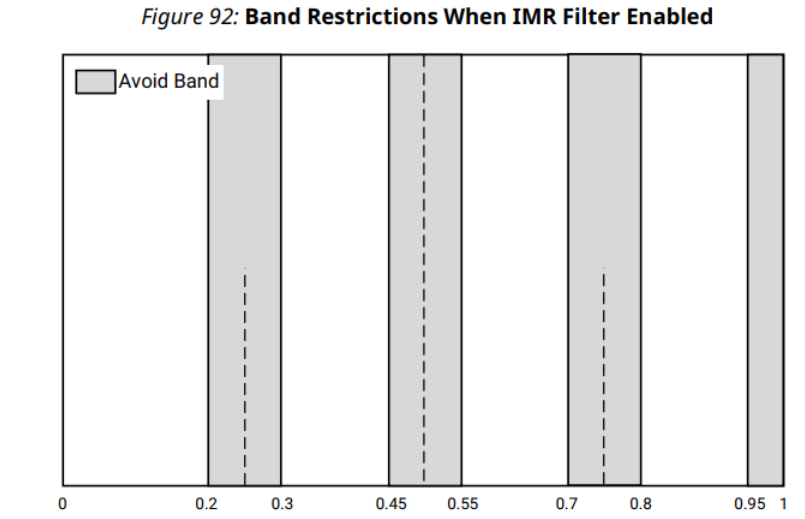

下图说明了带有 IMR 滤波器的 RF-DAC 数据路径。

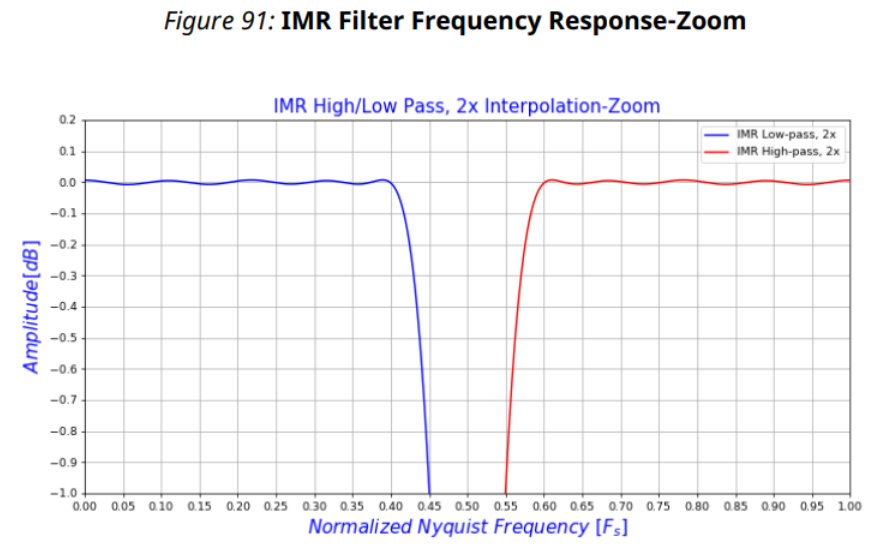

IMR 滤波器可以配置为高通或低通模式。 滤波器是对称的,在 80% 奈奎斯特频带内具有 60 dBc 的抑制和 ±0.01dB 的平坦度。

在低通模式下配置 IMR 滤波器时,来自 DUC 的原始信号被传递到 RF-DAC; 在高通模式下配置 IMR 时,第二奈奎斯特频带(在 2x 插值之前)中的图像信号被传递到 RF-DAC。 注意高通滤波器后的信号是原始信号的逆拷贝; 反转 NCO 的符号可以纠正这一点。

启用 2x IMR 滤波器时,RF-DAC 高采样率模式下可用的插值因子如下所列:

2x(仅限 IMR)、4x、6x、8x、10x、12x、16x、20x、24x、32x、40x , 48 倍, 80 倍

Image Rejection Filter Details (Gen 3)

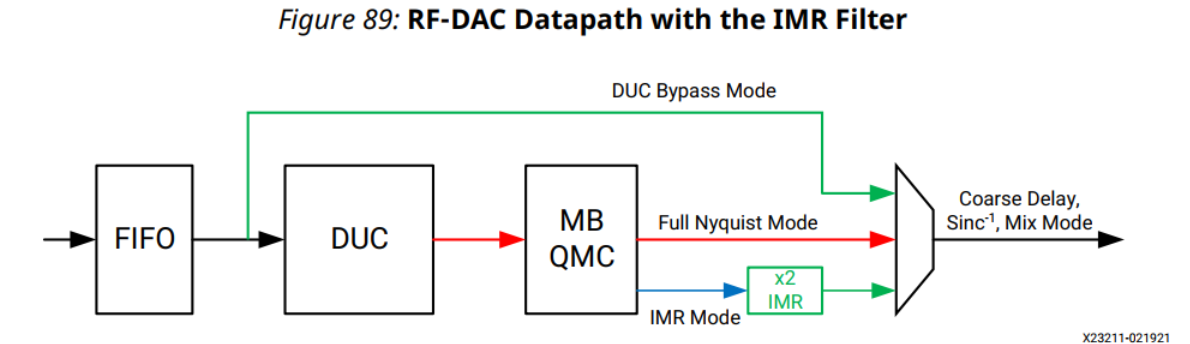

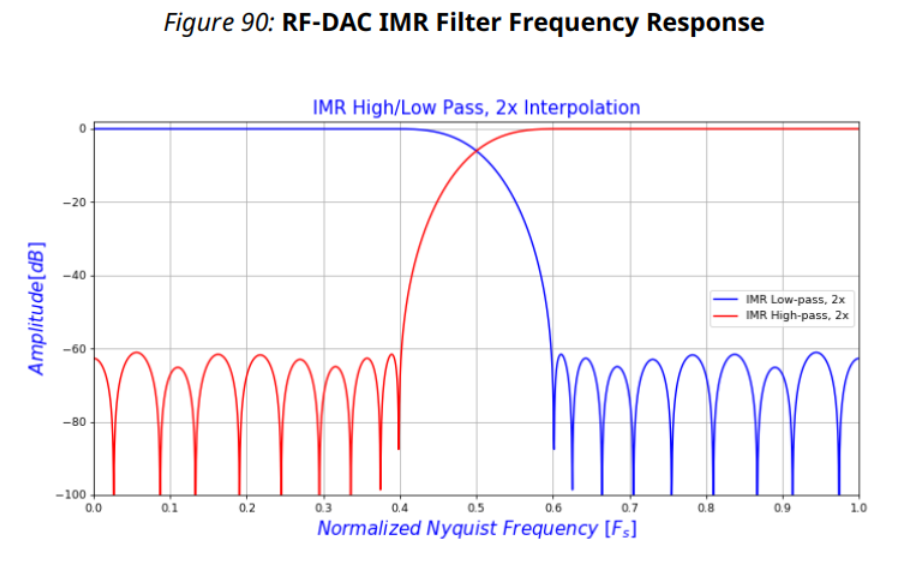

IMR 插值滤波器的系数和频率响应如下所示。

IMR 滤波器系数

N(bit) = 12 Center Tap: 4096 for low pass; -4096 for high pass First Half: 10,0,-23,0,48,0,-89,0,154,0,-256,0,432,0,-813,0,2588

下图显示了高通和低通滤波器模式之间交叉区域的放大图。

RF-DAC 数据通路模式(第 3 代)

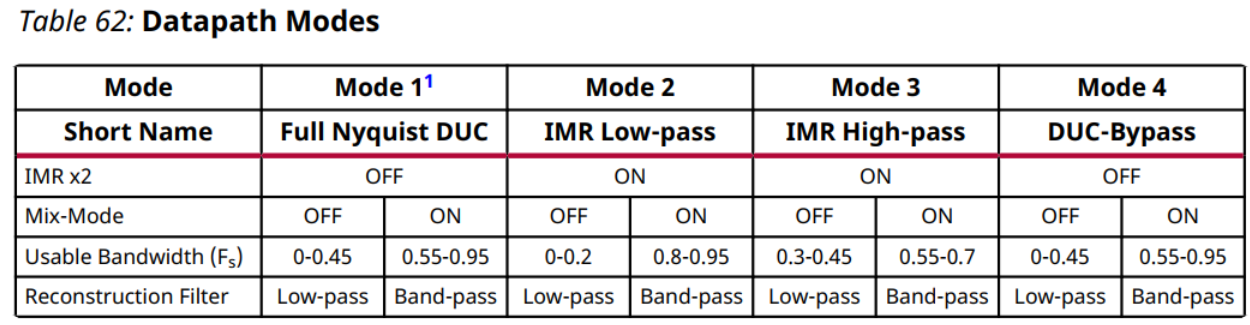

RF-DAC 数字数据通路旨在权衡性能、灵活性和功耗。 最大采样率和可用输出带宽取决于某些数据路径配置。 下表结合了不同的功能块,列出了所有可用的 RF-DAC 数据路径模式。

每对2x 多频段实部数据。 启用该对的一个 RF-DAC 输出; 另一个是关闭的。

每对2x 多频段I/Q 数据。 这对中的两个 RF-DAC 均已启用,一个用于 I,一个用于 Q。

每个块4x 多波段真实数据。 四个输入流组合在一起以在实模式下驱动 DAC0 输出。 所有其他 RF-DAC 均关闭。

每块4x 多频段I/Q 数据。 四个输入流组合起来驱动 DAC0 输出作为 I 和 DAC1 输出作为 Q。所有其他 RF-DAC 都关闭。

多频带对中的输出之间的延迟是匹配的,并且对之间的延迟是匹配的,与模式无关。

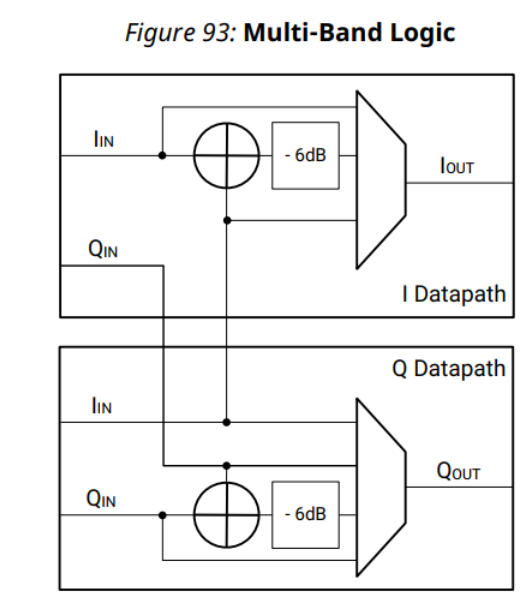

当多频段关闭时,I 和 Q 数据路径直接通过多频段逻辑模块(如下所示)。 当多频段开启时,每个数据路径的 I 和 Q 被组合并传递到 RF-DAC 前面的链中的下一个 DSP 模块。 每个 RFDAC 可以打开多频段,仅用于 I 数据路径或 Q 数据路径,或同时用于 I 和 Q。

为避免两个信号相加时的潜在溢出,在每个 I 和 Q 的加法器之后引入了 -6 dBV 缩放。因此,对双频带应用 -6 dBV 缩放,对四频带应用 -12 dBV 缩放。 可以通过 RFdc API 禁用默认的 -6 dB 缩放。

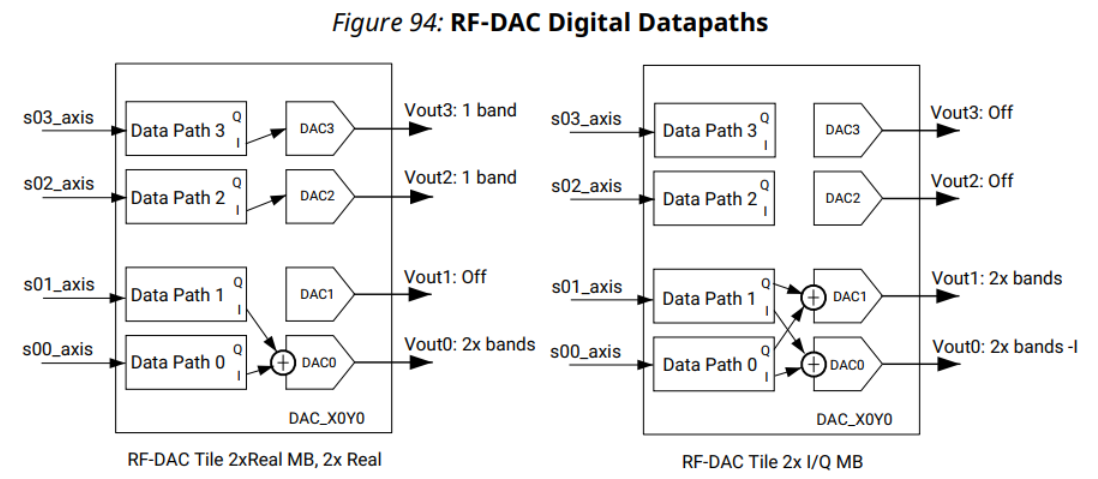

RF-DAC 多频段是通过将多个 RF-DAC DUC 模块连接到一个 RF-DAC 模拟模块来实现的。 每个 DUC 块处理一个数据带,并且可以将其混合到任何载波频率。 然后将输出求和,然后发送到模拟数据路径和 RF-DAC 输出。 如下图所示。

显示了两个示例多频带配置。 RF-DAC 块由四个 DUC 模块(数字数据路径)和四个 RF-DAC 模拟模块(模拟数据路径)组成。 在左手示例中,图块中较低的 RF-DAC 对配置为 2x 实数多频带,而顶部对是独立的 RF-DAC。 因为底部对使用了两个 DUC 块,所以 DAC1 关闭,DAC0 输出双频信号。 在右侧示例中,下对配置为 2x I/Q 多频段,而上对被关闭。

双 RF-DAC Tile (Gen 3)

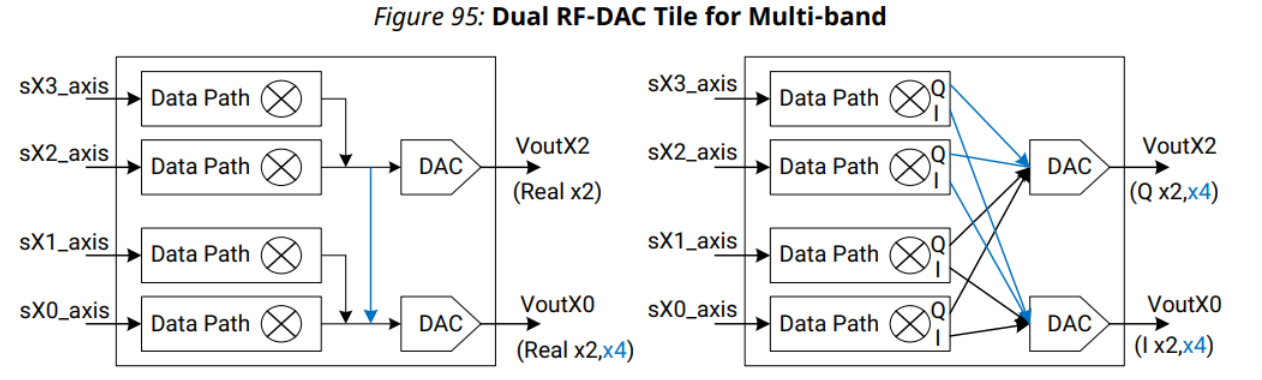

每个双 RF-DAC Tile 还集成了四个 DUC 块。 下图显示了实数和复数输出中的双频和四频配置。

RF-DAC 可编程逻辑数据接口

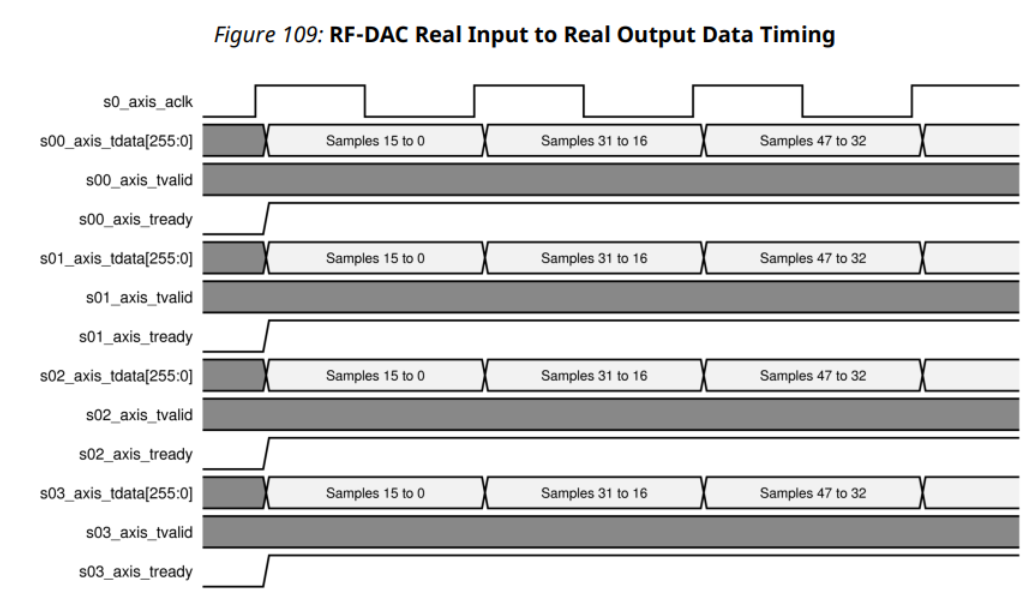

RF-DAC 块和 PL 之间的数据接口通过使用 AXI4-Stream 协议的并行数据流实现。 这些数据流输入到FIFO,在用户应用程序和 RF-DAC 块之间提供灵活的接口。 每个流的最大接口宽度为 256 位,最多可表示 16 个 16 位小端字。 数据流和相关的 FIFO 具有可配置的字数,可以灵活地在字数和时钟频率之间进行选择,以与 PL 设计接口。

每个 tile 有四个流,命名约定为 sXY_axis,其中 X 表示 RF-DAC tile 编号,Y 表示输入到该 tile 中 FIFO 的流。 下图显示了接口。

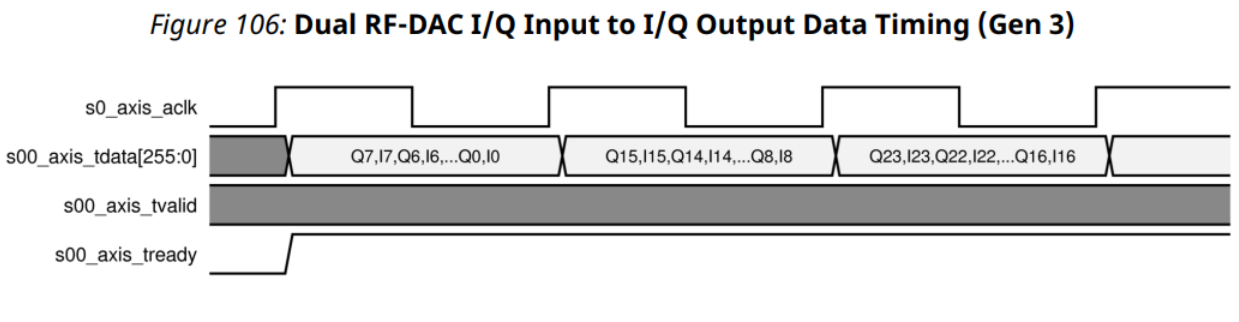

接口数据格式

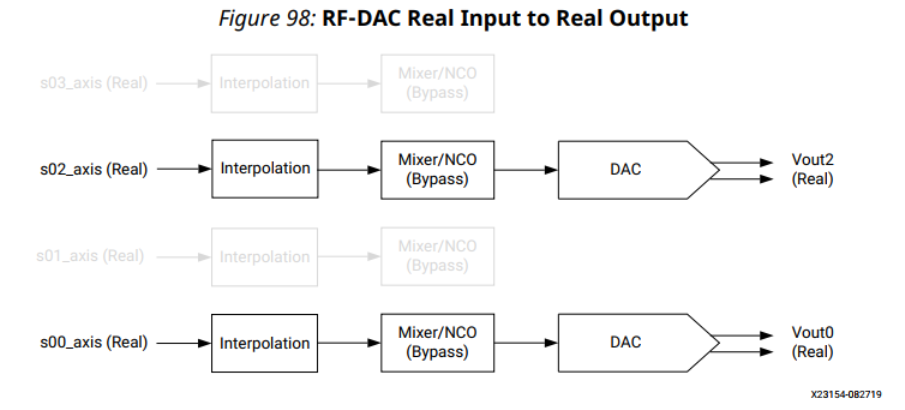

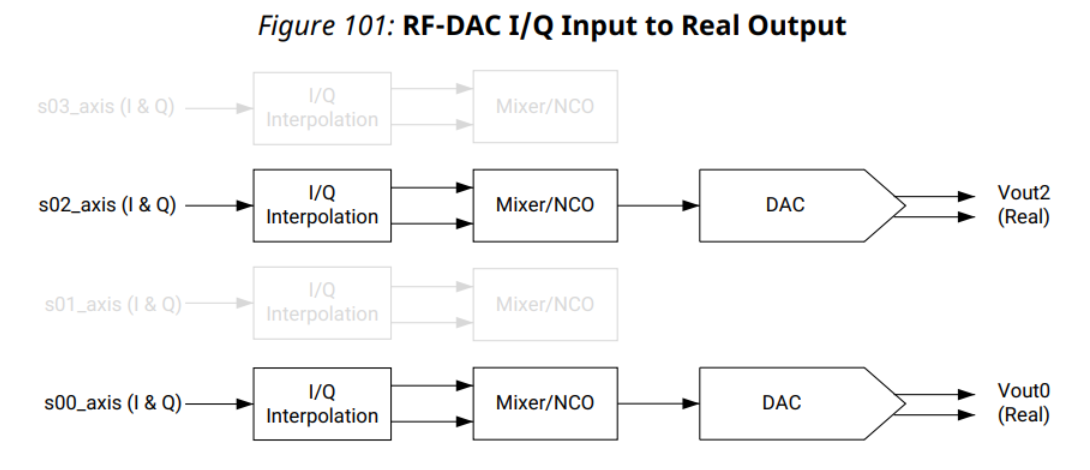

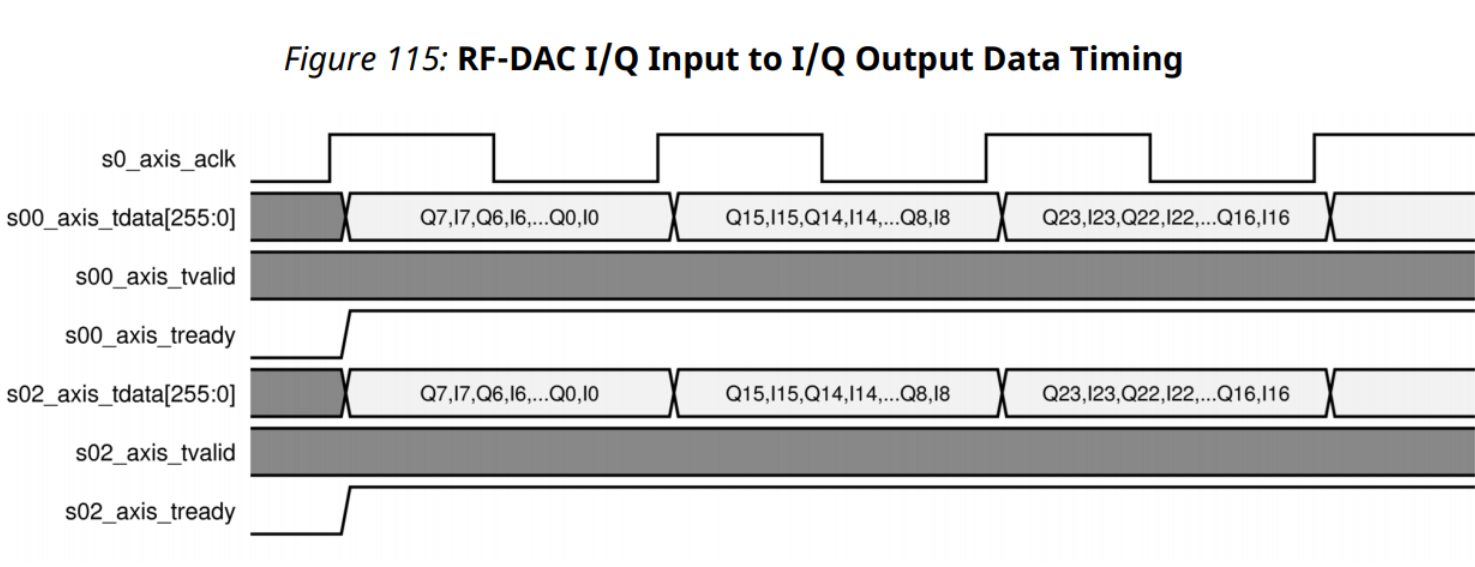

数据流代表真实数据或 I/Q 数据,具体取决于 RF-DAC 块配置。 对于 RFDAC 块,给定的流要么是真实的,要么是 I/Q 交错的。 如果 RF-DAC 配置有 I/Q 输入数据,则流的偶数样本代表 I 数据,奇数样本代表 Q 数据。 这些实数和 I/Q 配置显示在 RF-DAC IP 配置中。

在每个配置中,一个 tile 中所有启用的 RF-DAC FIFO 在上电序列完成时开始接收数据。 这由 sXY_axis_tready 输出的断言指示。 如果此时任何流的数据无效,抑制它的逻辑应包含在 PL 中。RF-DAC 不使用 sXY_axis_tvalid 输入来选通数据。

RF-DAC 接口数据和时钟速率 每个通道到 PL 的总数据速率由许多因素决定,RF-DAC 采样率、插值因子和 I/Q 或实数数据格式。 通过允许选择每个时钟的字数,FIFO 提供了一种将此数据速率连接到 PL 设计的时钟频率的方法。 唯一的要求是接口字数和时钟速率相结合,以匹配 RF-DAC 通道所需的数据速率,并且一个 tile 中的所有 RF-DAC 共享一个公共接口时钟频率。 这由以下等式表示:

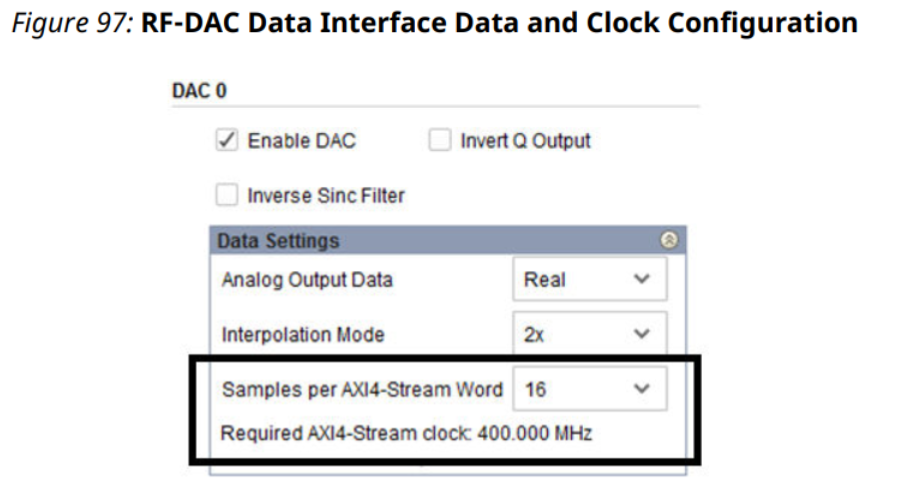

IP 内核根据 RF-DAC 采样率和数据路径设置自动计算数据速率。 如下图所示。

每个瓦片都有独立的时钟; 采样率、时钟率、PL 率和配置可以在每个瓦片的基础上指定。

PL 时钟接口

所有四个分片流的 AXI4-Stream 数据与来自 PL 的时钟同步,PL 的命名约定为 sX_axis_aclk,其中 X 代表 RF-DAC 分片编号。 此时钟必须处于 IP 内核配置屏幕上显示的所需 AXI4-Stream 时钟指定的频率。

RF-DAC 块还输出可供 PL 使用的时钟。 该输出时钟是 RF-DAC 采样时钟的分频版本,因此对其进行频率锁定。 此时钟具有 clk_dacX 的命名约定,其中 X 表示 RF-DAC 块编号。

接口 FIFO 溢出

通过FIFO 的数据速率在 RFDAC 块运行期间必须保持恒定,PL 时钟和 RF-DAC 模拟采样时钟域之间没有频率漂移。 如果这些域之间存在频率不匹配,则可能发生 FIFO 溢出。

接口 FIFO 具有确定是否发生 FIFO 溢出的内置特性,该特性通过 IP 中断机制标记给 PL。溢出有两种类型:实际溢出和边际溢出。 实际溢出表明 FIFO 读/写指针重叠,这意味着数据没有在域之间安全传输,必须采取措施。 边际溢出是一个警告,表示 FIFO 读/写指针接近重叠。 正常操作期间不应发生溢出,如果发现溢出,则表明 PL/PCB/IP 内核的时钟基础结构配置不正确。

同步

FIFO 为 RF-DAC 块提供灵活的数据和时钟接口。 但是,与所有双时钟 FIFO 一样,延迟可能会在一个 tile 和另一个 tile 之间有所不同。 虽然 tile 中的所有通道都具有相同的延迟,但某些应用程序可能需要使用多个 RF-DAC tile,并且需要在所有 RF-DAC 通道中匹配延迟。 这些应用程序可以使用多块同步 (MTS) 功能来实现这种块间同步。

RF-DAC IP 配置

RF-DAC 可以配置为多种模式。 Vivado中的 IP 内核配置屏幕上提供了基本配置选项,并且可以使用 RFdc 驱动程序 API 配置高级操作模式。

双 RF-DAC 配置选项(第 3 代)

双 RF-DAC 实输入到实输出(第 3 代)

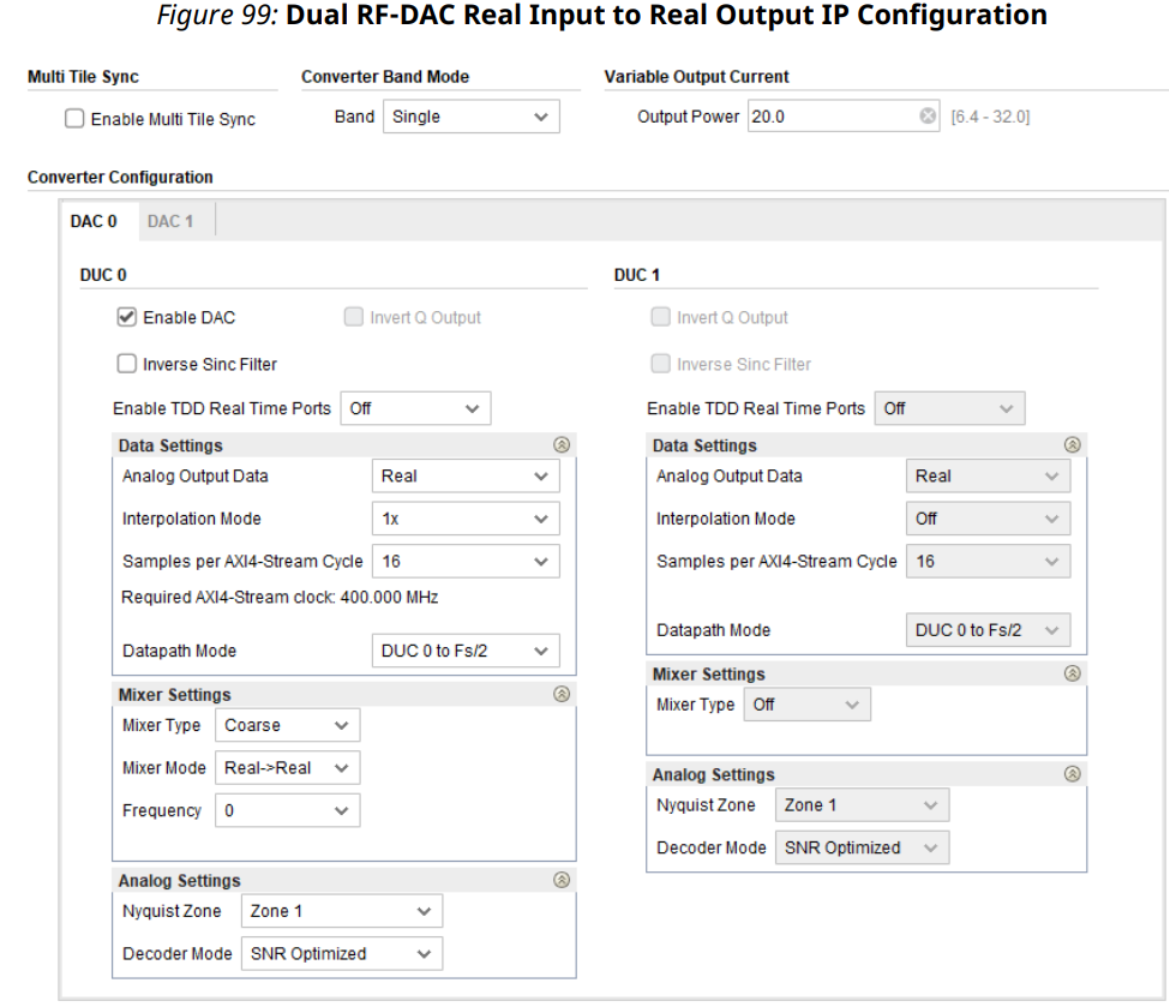

下图显示了一个双路 RF-DAC,它具有实输入到实输出、1x 插值、混频器被绕过并以 400 MHz AXI4-Stream 时钟运行。

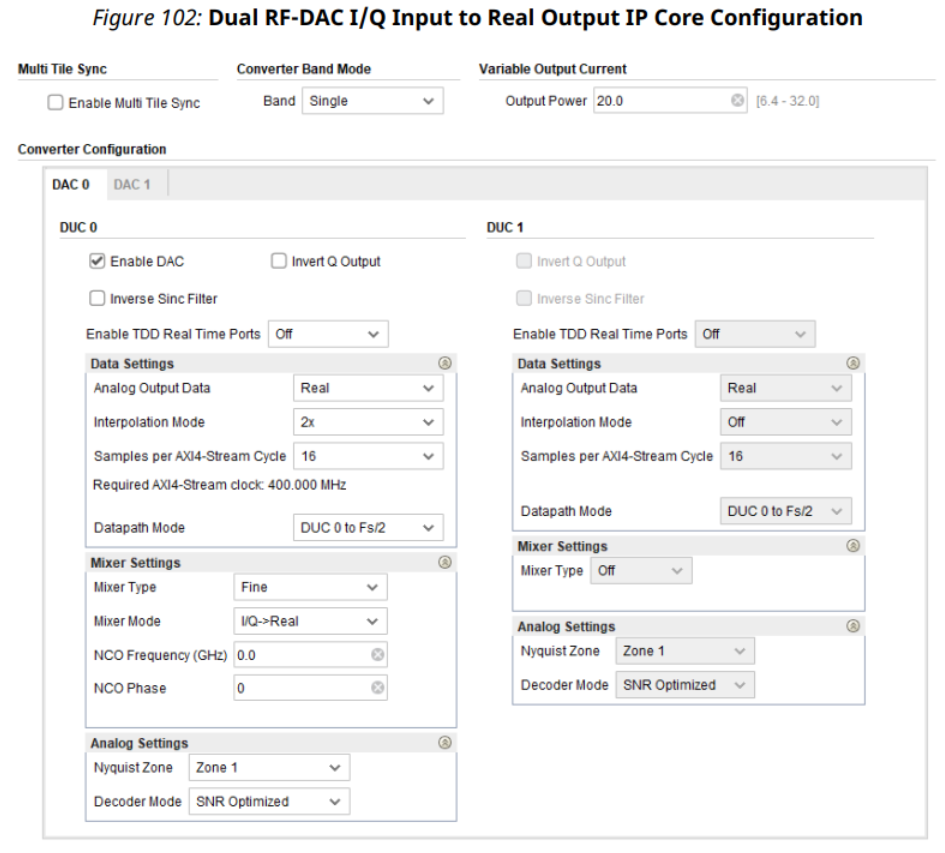

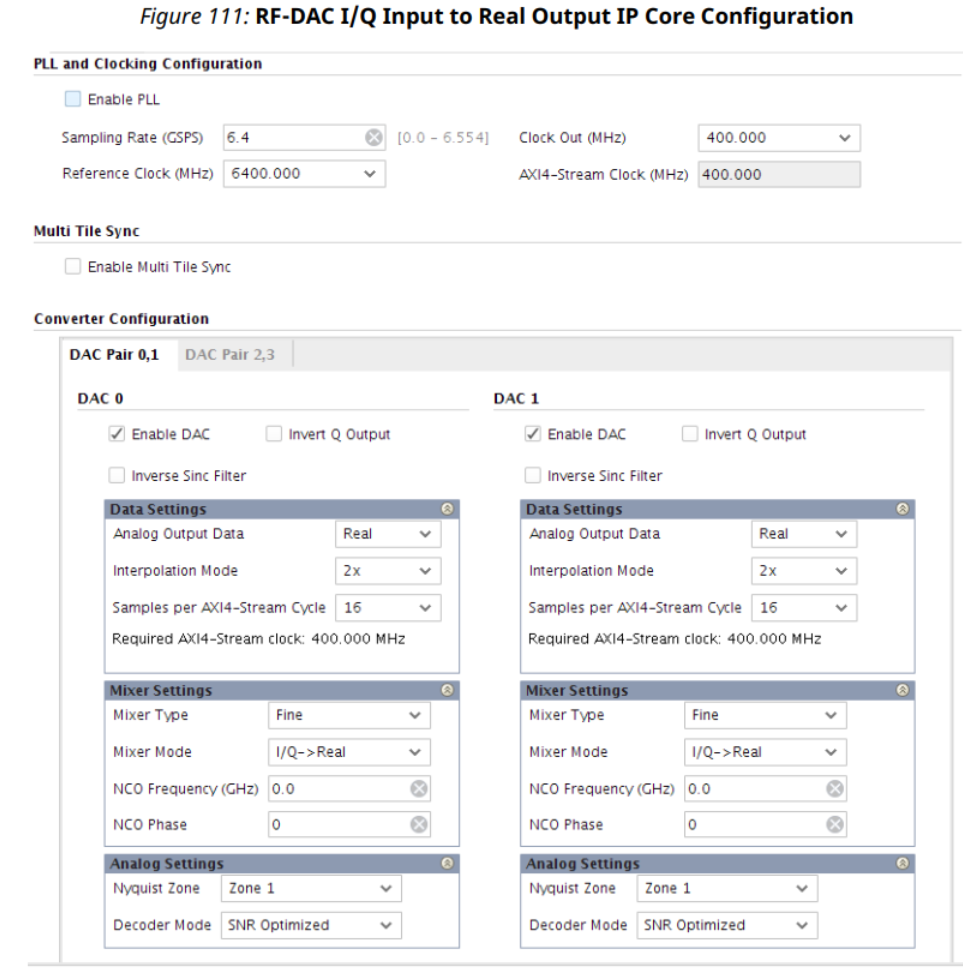

双路 RF-DAC I/Q 输入到实输出(第 3 代)

下图显示了一个双路 RF-DAC,它具有 I/Q 输入到实际输出、2x 插值、混频器被绕过并以 400 MHz AXI4-Stream 时钟运行。 输入由每个 AXI4-Stream 周期的 16 个样本组成(8 个 I 字和 8 个 Q 字)。

插值是 x2,因为 AXI4-Stream 接口上可用的带宽是有限的。

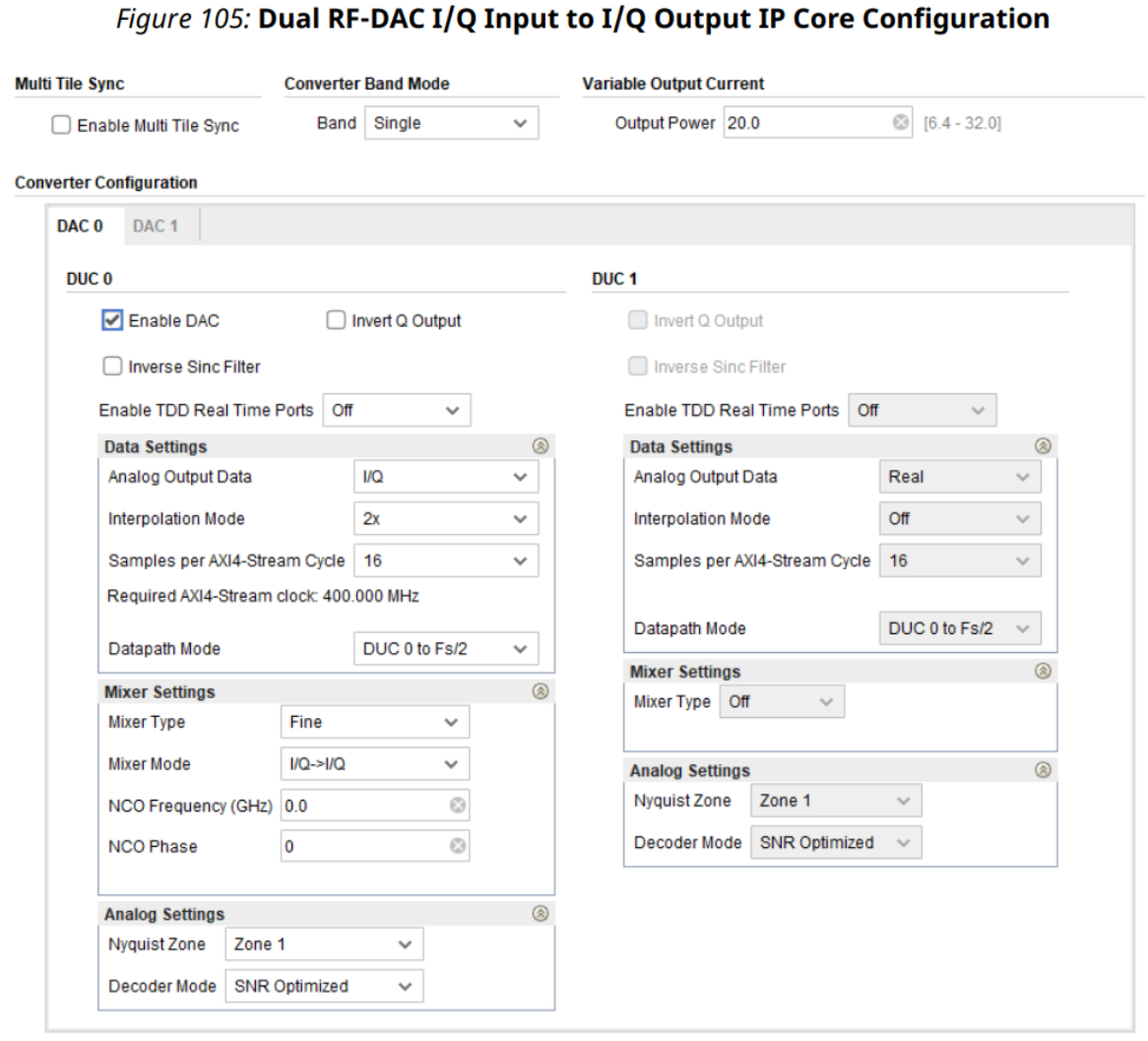

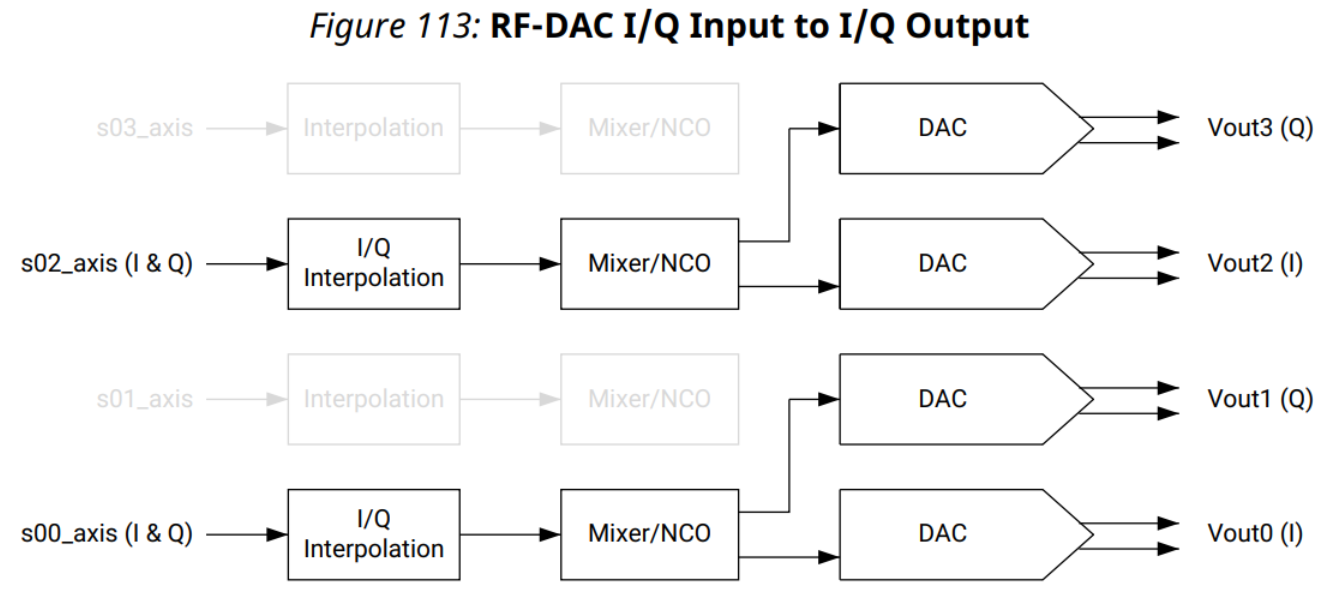

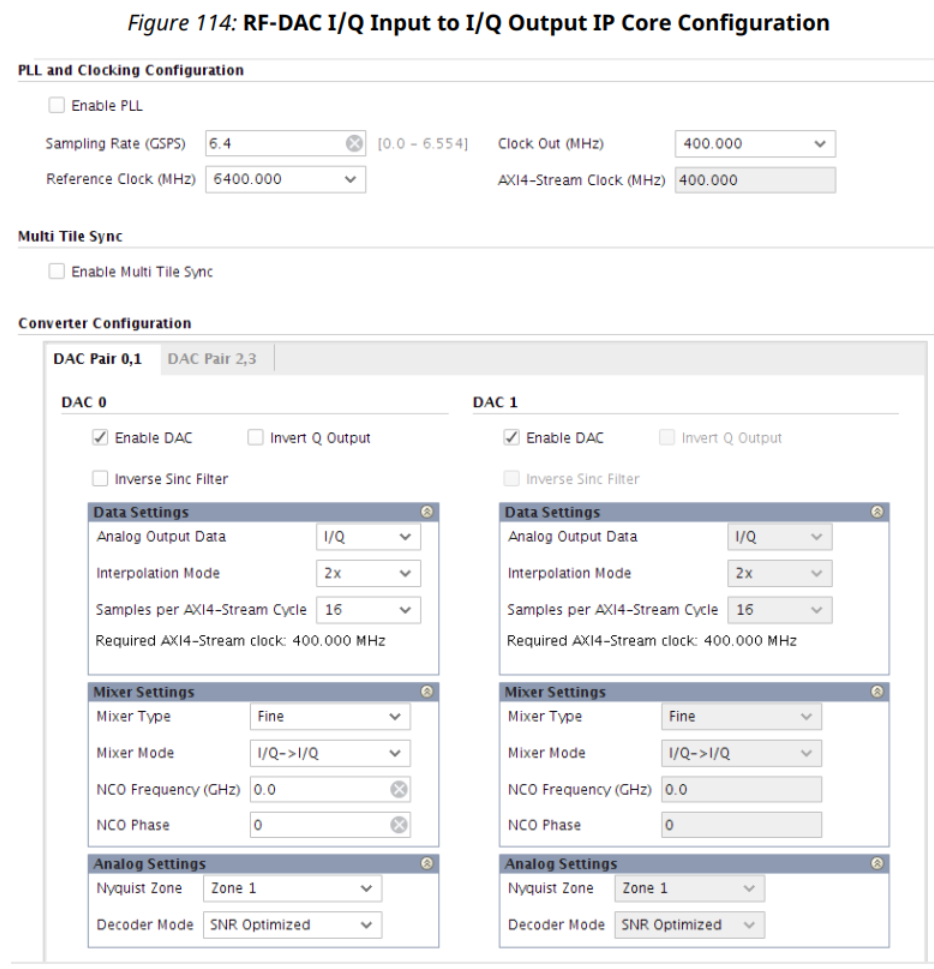

双路 RF-DAC I/Q 输入到 I/Q 输出(第 3 代)

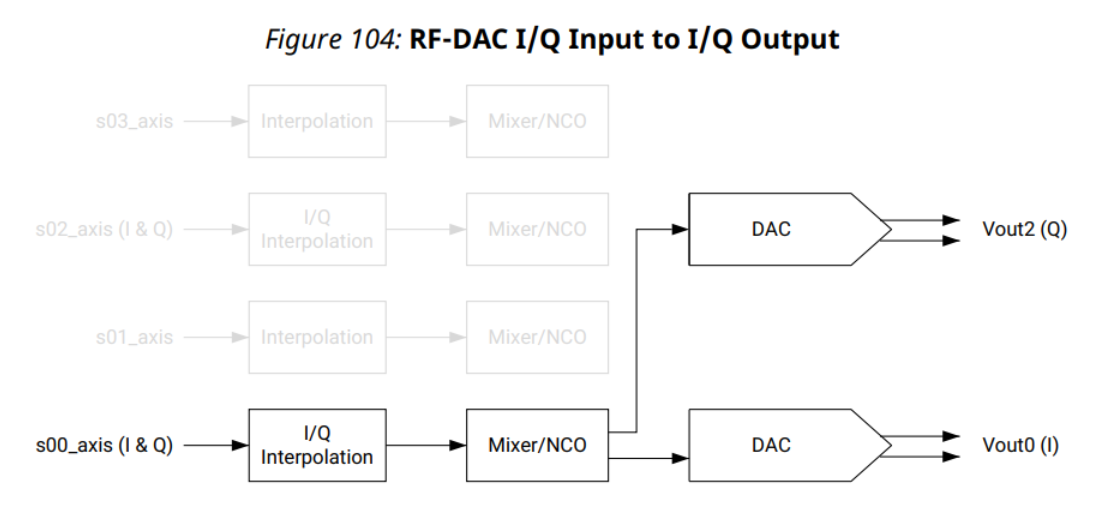

对于 I/Q 输入到 I/Q 输出,RF-DAC 是配对的。 I/Q 输出信号需要一对 RFDAC,一个用于 I 数据,一个用于 Q 数据。 如下图所示,单个 DUC 模块输出 I 和 Q 数据,这些信号被发送到两个 RF-DAC。

下图显示了一个双 RF-DAC,它具有 I/Q 输入数据到 I/Q 输出数据,具有 2x 插值,混频器被绕过,并且具有 400 MHz AXI4-Stream 时钟。

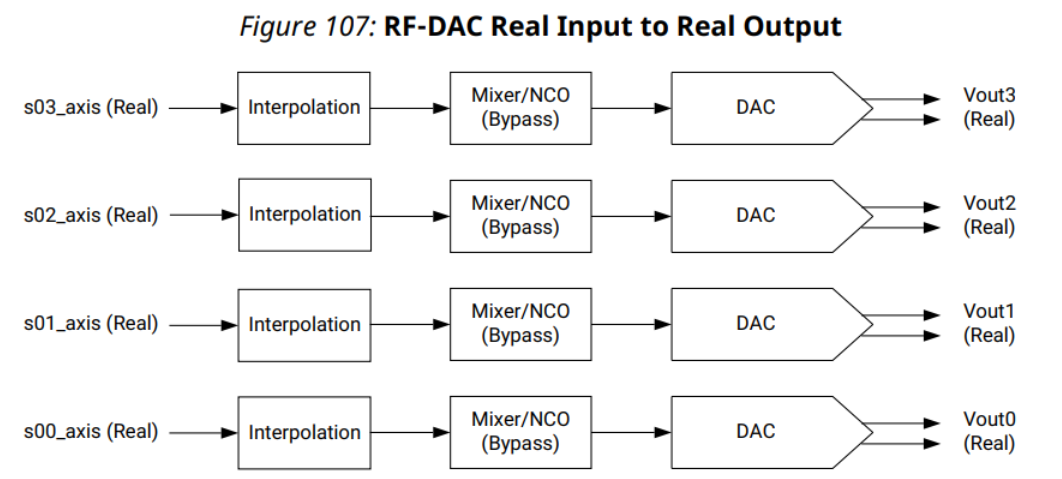

四路 RF-DAC 配置选项

下图显示了一个 RF-DAC,它具有实际输入到实际输出、1x 插值、混频器被绕过并以 400 MHz AXI4-Stream 时钟运行。

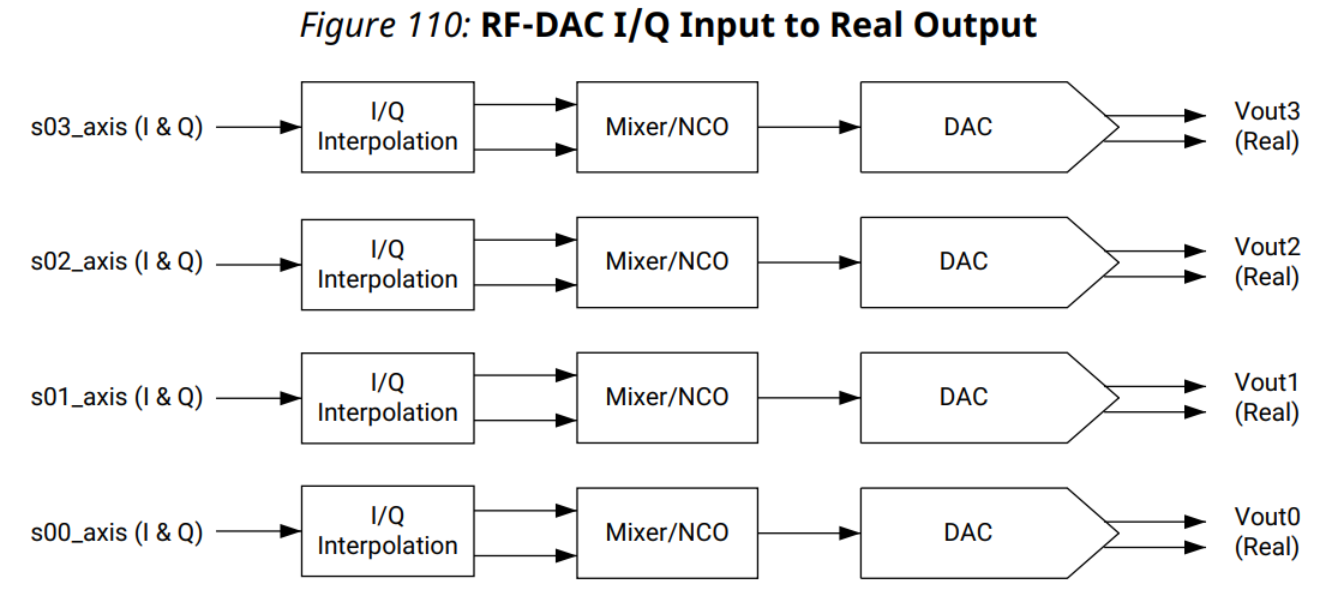

四路 RF-DAC I/Q 输入到实输出

下图显示了一个 RF-DAC,它具有 I/Q 输入到实际输出、2x 插值、混频器被绕过并以 400 MHz AXI4-Stream 时钟运行。 输入由每个 AXI4-Stream 周期的 16 个样本组成(8 个 I 字和 8 个 Q 字)。

四路 RF-DAC I/Q 输入到 I/Q 输出

对于 I/Q 输入到 I/Q 输出,RF-DAC 是配对的。 I/Q 输出信号需要一对 RFDAC,一个用于 I 数据,一个用于 Q 数据。 如下图所示,单个 DUC 模块输出 I 和 Q 数据,这些信号被发送到两个 RF-DAC。

下图显示了一个具有 I/Q 输入数据到 I/Q 输出数据的 RF-DAC,采用 2x 插值,混频器被绕过,并且具有 400 MHz AXI4-Stream 时钟。

reference