本文转载自:Vuko-wxh的CSDN博客

前言

RFSoC驱动射频直采ADC和DAC的正常工作离不开时钟,本文参考官方手册,主要对RFSOC的时钟结构以及相关配置进行介绍,并简单介绍了关于复位的操作。

时钟

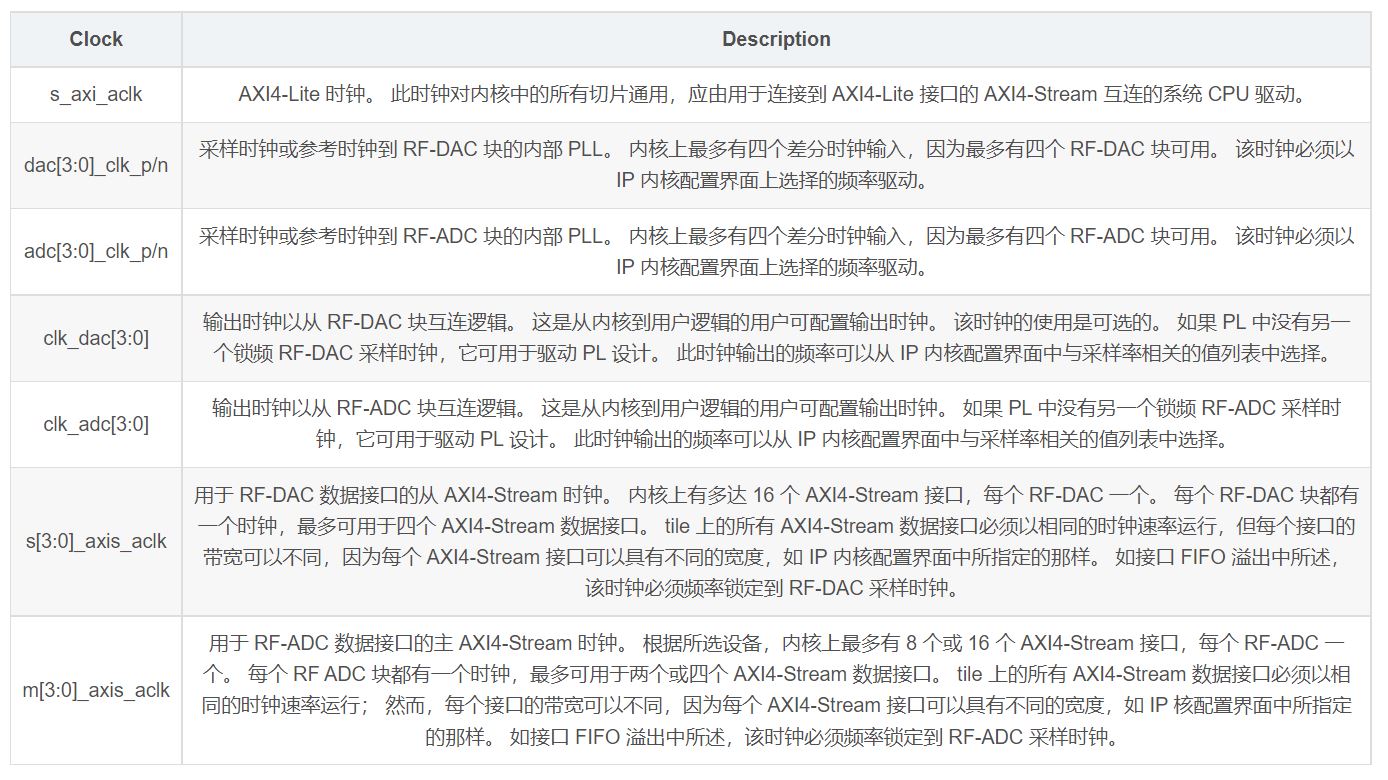

下表描述了与 Zynq UltraScale+ RFSoC RF 数据转换器 IP 内核相关的时钟。

时钟输入

时钟输入

在大多数情况下,每个 RF-ADC 或 RF-DAC 块都有自己的时钟输入。 无需在您的设计中例化时钟输入缓冲器,因为电流模式逻辑 (CML) 时钟输入缓冲器是在 tile 架构中实现的。 时钟输入缓冲器可用作 tile 的采样时钟或 tile PLL 的参考。 CML 时钟输入具有 100Ω 的片上差分终端。

时钟输入缓冲器有一个检测电路,用于测量外部时钟输入的活动。当存在时钟时,输入缓冲器被激活。 当不存在时钟时,时钟缓冲器的输出被强制进入稳定状态。 如果时钟丢失,核心将关闭 tile,但在时钟返回时将重新启动 tile,无需用户干预。 每次内核关闭tile时,复位计数寄存器都会增加。不使用 PLL 时,时钟缓冲器输出通过多路复用器进入 RFADC 或 RF-DAC 块时钟网络。 当使用 PLL 时,时钟缓冲器的输出被驱动到 PLL 作为参考时钟。

在每个RFSoC 中,每个封装都有一个专用输入 SYSREF 引脚对。 SYSREF 为多块和多设备同步提供时钟。 对于多块设计,SYSREF 连接到主块,信号必须从该块内部分配到设计中使用的所有其他块。可以使用 RFdc 软件 API 检查输入引脚上是否存在时钟。 如果未检测到时钟,则受影响的 RF-ADC 和 RF-DAC 模块不会启动并保持在时钟检测状态。

Tile 时钟结构

下图显示了 tile 高级时钟结构。 tile 中的时钟结构从来自 tile PLL 或直接来自时钟输入引脚的单个时钟源开始。

为使 tile 保持低抖动和高速时钟结构,单个输入时钟被路由到 tile 中的每个 RF-ADC 或 RF-DAC,并被分频以用于 RF-ADC 或 RF- 内的专用信号调节功能。

来自主块分频器的时钟可用于驱动 PL。 当使用输出时钟时,IP 内核会自动例化一个 BUFG_GT 缓冲器。

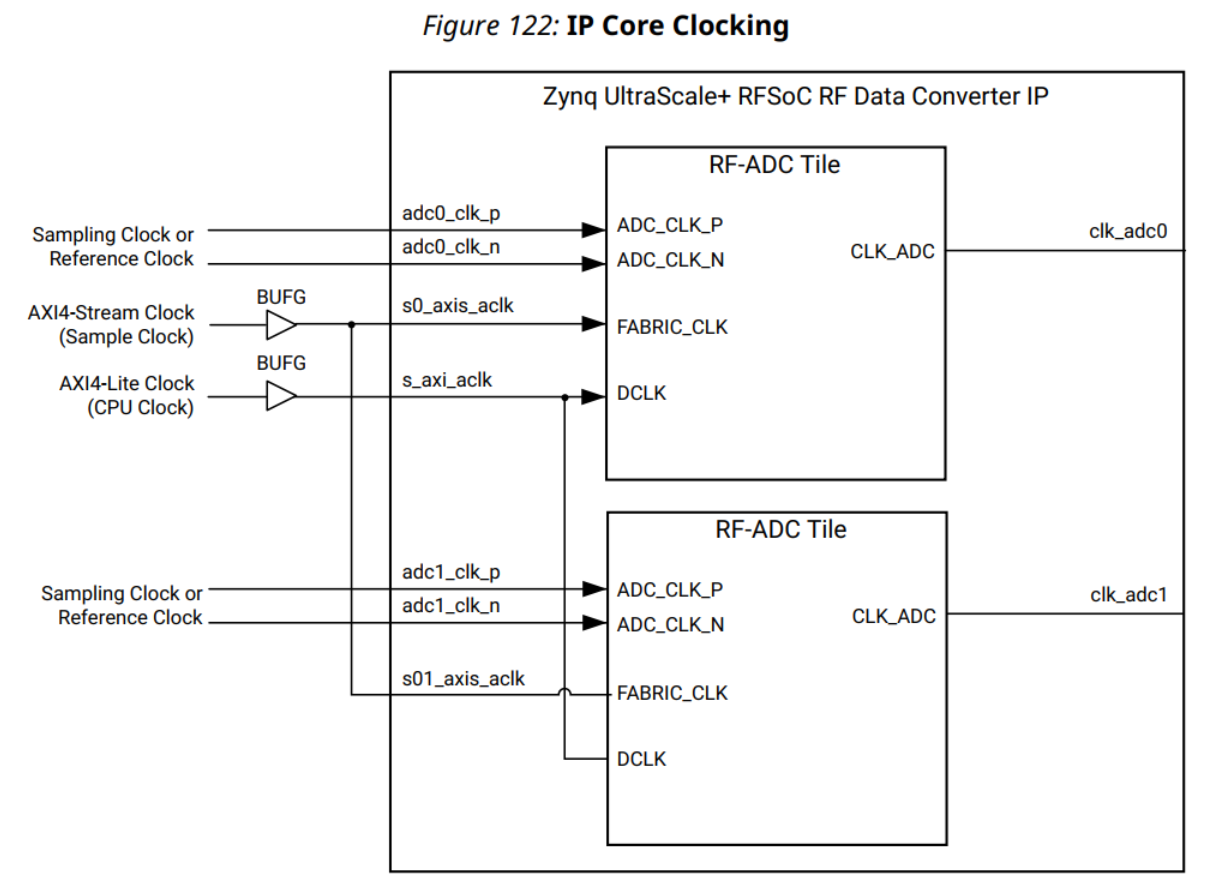

下图显示了典型 Zynq UltraScale+ RFSoC RF 数据转换器 IP 内核的时钟连接。 IP 内核根据 Vivado 中的选择自动例化和连接组成 RFADC 和 RF-DAC 块。

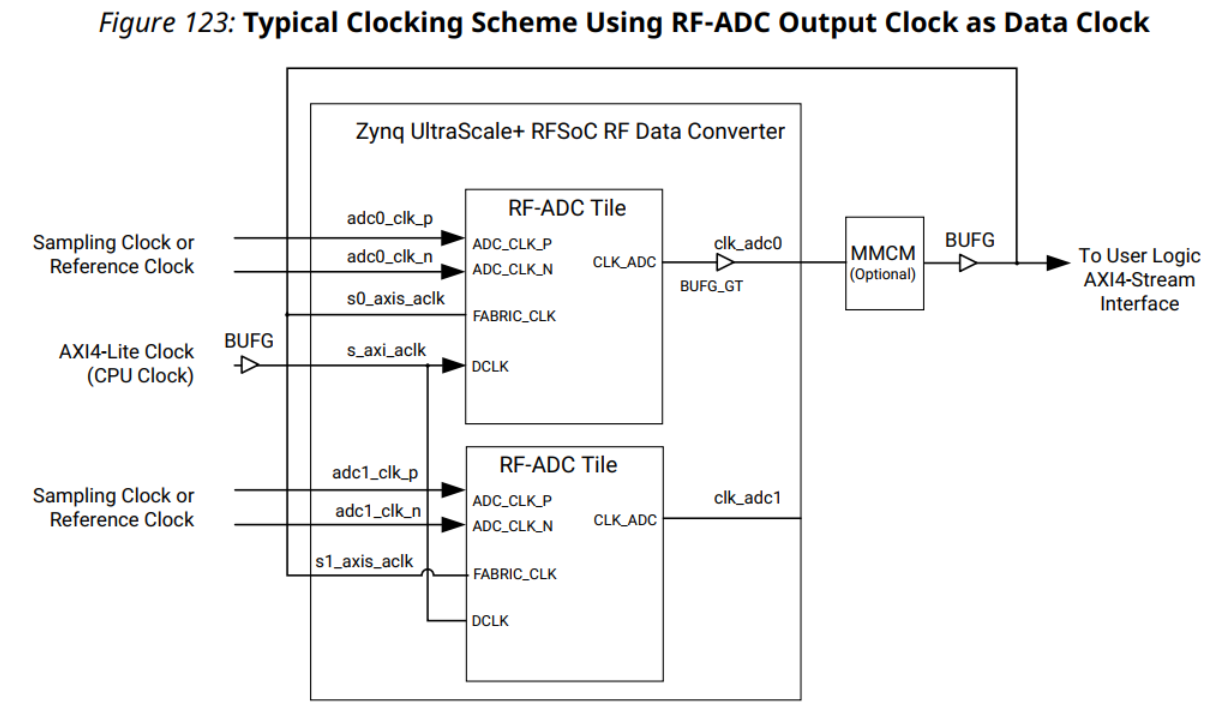

在大多数应用中,AXI4-Stream 时钟对多个转换器通用,并由外部时钟提供,如上图所示。 该时钟必须来自与 RF-ADC 和 RF-DAC 块的采样和/或参考时钟相同的主时钟源。或者,可以使用 RF-DAC 或 RF-ADC 块之一的输出来生成 AXI4-Stream 时钟,如下图所示。

片上时钟分配(第 3 代)

RFSoC 包含多个 RF-ADC 和 RF-DAC 块。 每个 tile 以自己的 tile 时钟 (T1) 独立运行。 T1 时钟可以是外部时钟,来自片上 PLL,或来自分布式采样时钟。

片上时钟分配网络允许一个块将其时钟转发到转换器块组内的相邻块。 瓦片组是相邻的瓦片集; 多个组是可能的,具体取决于应用程序要求,直到它们从设备拼贴序列中的连续拼贴构建。 瓦片组可以由 RF-DAC 瓦片、RF-ADC 瓦片或两者组成。 瓦片组对设计施加以下约束:

每个片组只能有一个源片。

不是源片的片组中的每个片必须使用转发时钟; 不允许使用不同的时钟跳过片。

当一个tile 组同时包含RF-DAC tile 和RF-ADC tile 时,源tile 必须是RF-DAC tile; 不允许将时钟从 RF-ADC 块转发到 RF-DAC 块。

来自源块的转发时钟信号可以是:

外部采样时钟

与内部 PLL 一起使用的外部参考时钟

片内PLL产生的采样时钟

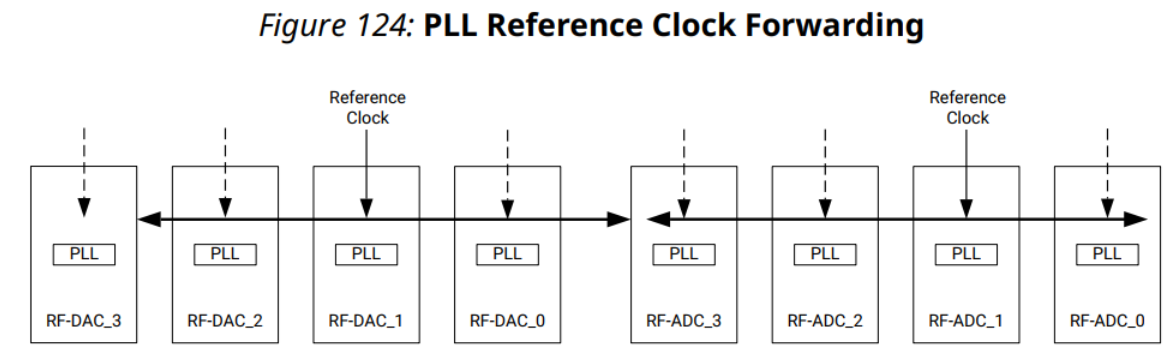

PLL 参考时钟转发(第 3 代)

任何 tile 都可以作为源 tile,以在 tile 组内转发其低频参考时钟,请注意上一节中提到的约束。 例如,在包含所有 RF-DAC 和 RF-ADC 块的块组中,源块必须是具有外部时钟输入引脚的 RF-DAC 块。

采样率时钟转发(第 3 代)

来自外部或由块内 PLL 生成的高频采样率时钟可以在块组内转发。 在这种情况下,一些额外的限制如下所列:

在第 3 代器件中,仅允许 RF-ADC Tile 3 和 Tiles 2 接受来自 RF-DAC Tile 的转发时钟。

Gen 3 Source Tile:如果 Tile 1 或 Tile 2(两个中心块)具有外部时钟输入管脚,则可以作为源 tile。Xilinx 建议将 Tile 1 作为时钟输入路径上的最佳相位平衡和最低损耗的源 tile。 Tile 2 还提供最佳相位平衡,但时钟输入路径上的损耗略高。

In-Tile Clock Divider:当 in-tile PLL 未启用时,每个 tile 都有一个独立的 1 或 2 时钟分频器。 当采样率时钟从 RF-DAC 块转发时,该块内时钟分频器不适用于双 RF-ADC 块。

转发路径时钟分频器:时钟分频器 1 或 2 位于时钟转发路径中。 此分频器仅在将采样率时钟从 RF-DAC 块转发到 RF-ADC 块时可用。 此时钟分频器具有比块内时钟分频器更高的优先级,这意味着在不允许在 RF-ADC 块中启用块内时钟分频器时绕过此转发路径分频器。

上述两种类型的时钟分频器均由 RFDC API 和 IP 自动处理。 应该注意时钟分配方案设计中时钟分频器的约束,以避免违规。

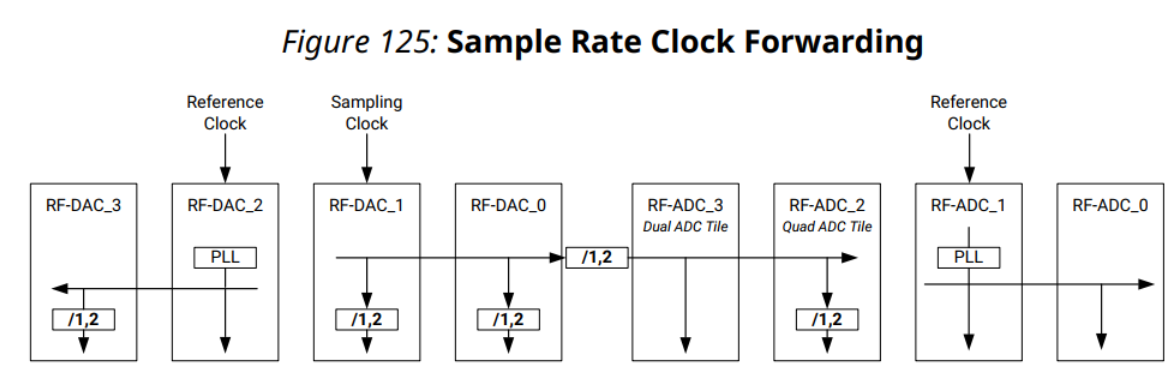

下图说明了此用例和相关约束:

该图的解释如下:

上图中共有三个 tile 组:

1. RF-DAC tile 3 和 2

2. RF-DAC tile 1 和 0,RF-ADC tile 3 和 2 3

3. RF-ADC tile 1 和 0

在 tile 组 #1 中,RF-DAC Tile 2 从外部接收参考时钟,并将其由 in-tile PLL 生成的 T1 时钟转发到 RF-DAC Tile 3。in-tile 时钟分频器不可用 在 RFDAC Tile 2 中,但对 Tile 3 可用。

在 tile 组 #2 中,RF-DAC Tile 1 从外部接收采样时钟并将其转发到 RF-DAC Tile 0、RF-ADC Tile 3 和 Tile 2。RF-DAC 中提供块内时钟分频器 Tile 1 和 0 因为两者都没有启用 PLL。 假设 RF-ADC Tile 3 是双 RF-ADC tile 而 Tile 2 是四 RF-ADC tile(这不是真实情况,仅用于说明),在 RF-ADC tile 3 中没有可用的 in-tile 时钟分频器, 但在 RF-ADC tile 2 中可用。请记住,如果在该组中启用了任何 in-tile 分频器(设置为 2),则转发路径分频器必须为 2。

在块组#3 中,RF-ADC 块1 和0 无法接收来自RF-DAC 块的转发采样率时钟。 这说明采样率时钟从 RF-ADC Tile 1 转发到 0。没有可用的块内时钟分频器,因为两个块都启用了它们的块内 PLL。

RF-DAC 采样率降额(第 3 代)

RF-DAC 的最大采样率在采样率时钟转发用例中被降额。 这适用于来自外部输入或块内 PLL 的采样时钟转发。 要获得完整的采样时钟速率,请将参考时钟分配到每个块或不使用时钟分配功能。

外部 T1 时钟转发(第 3 代)

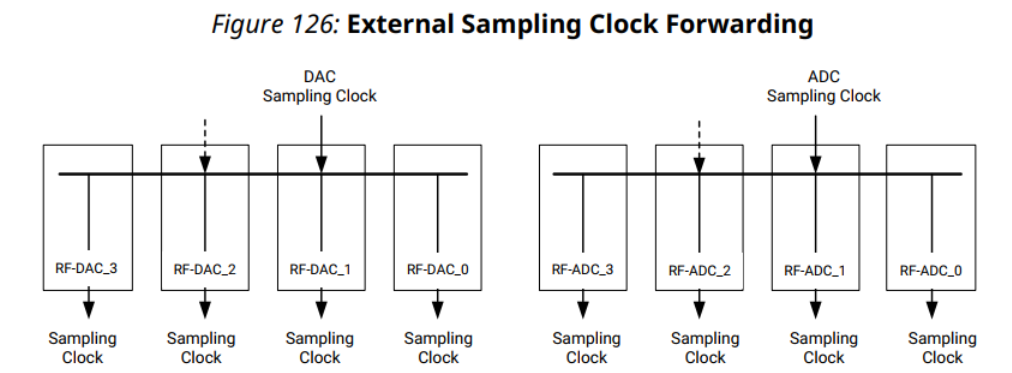

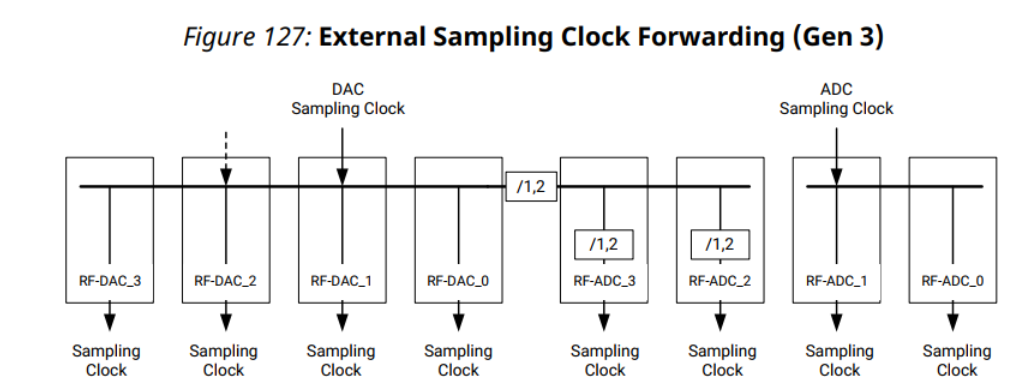

外部采样时钟可以分别在 RF-ADC 和 RF-DAC 组内转发。

外部 T1 时钟转发到 RF-ADC (Gen 3)

外部采样时钟可以通过 1 或 2 的时钟分频器从 RF-DAC 组转发到 RF-ADC Tile 3 和/或 2。Tile 3 和 2 已嵌入 1 或 2 的时钟分频器输出所需的时钟频率,请注意在这种情况下,Tile 3 和 2 中的时钟分频器仅可用于四路 RF-ADC Tile。 RF-ADC tile 0 和 1 共享另一个外部采样时钟。

参考时钟转发(第 3 代)

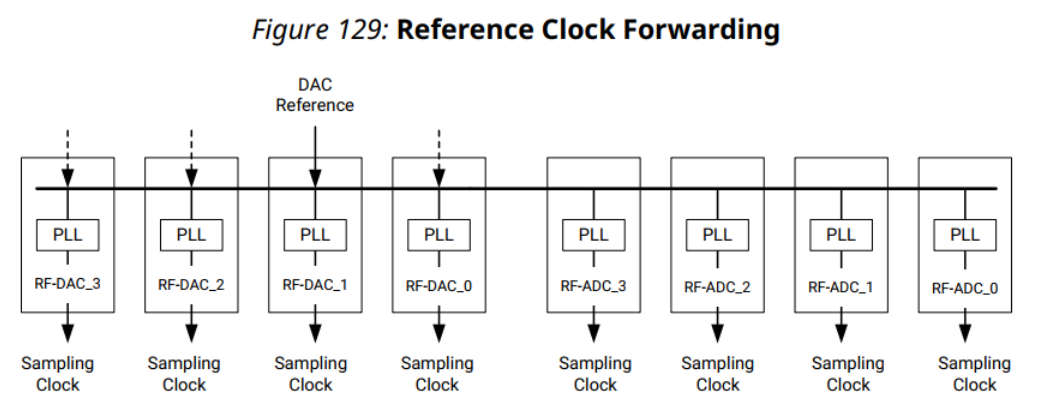

外部参考时钟可以分别在 RF-ADC 和 RF-DAC 组内转发。

RF-ADC 的参考时钟转发(第 3 代)

RF-ADC 和 RF-DAC 组的外部参考时钟转发。 源块必须来自 RF-DAC。

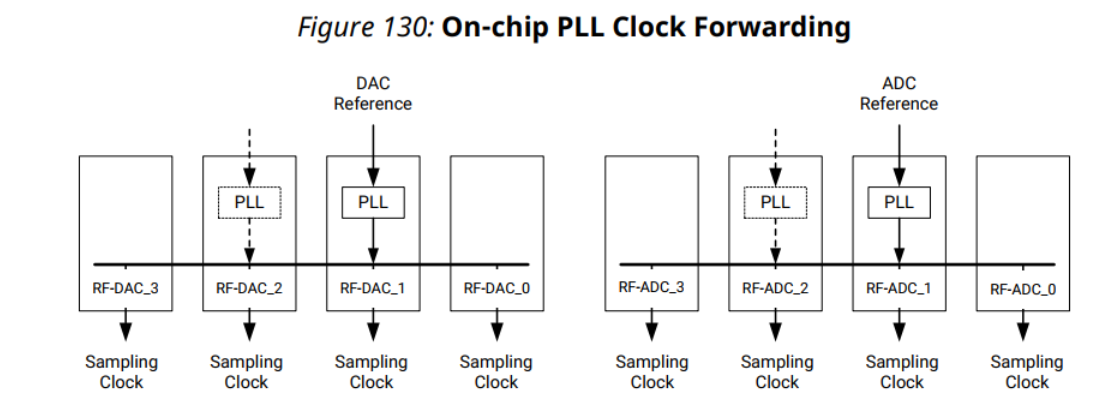

片上 PLL 时钟转发(第 3 代)

片上 PLL 生成的采样时钟分别在 RF-DAC 和 RF-ADC 组中转发。 时钟源必须选择为 Tile 1 或 Tile 2。

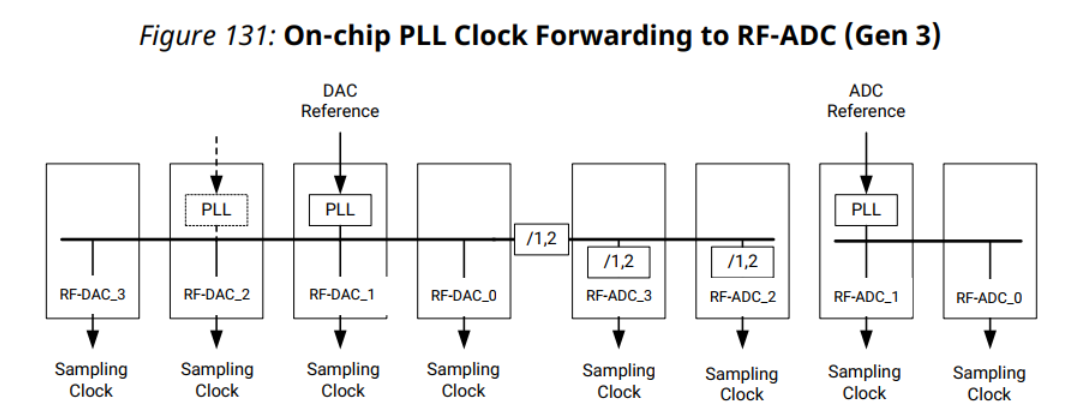

片上 PLL 时钟转发到 RF-ADC (Gen 3)

片上 PLL 产生的采样时钟从 RF-DAC 组转发到 RF-ADC Tile 3 和/或 2,Tile 3 和 2 具有内置 1 或 2 的时钟分频器以输出所需的时钟频率,请注意,在这种情况下,Tile 3 和 2 中的时钟分频器仅适用于四路 RF-ADC Tile。 RF-ADC Tile 0 和 1 共享片上 PLL 生成的时钟。

复位

为每个时钟域提供标准 AXI4-Stream 复位。 RF-ADC 和 RFDAC 的复位使用 AXI4-Lite 接口完成。 通过断言主复位寄存器的位 0 来执行完整的块复位。 可以通过写入重启寄存器来复位和禁用各个图块。 禁用tile以类似的方式实现。 按照单个tile重置程序在禁用tile后重新启动tile。 此外,需要取消断言流重置才能完成启动 FSM。

reference

1.PG269