作者:饿狼传说,文章来源:FPGA的现今未的微信公众号

计数器在FPGA设计中有着非常广泛的应用,是FPGA设计的基础。本文介绍一些计数器的常用方法和注意点。

1、定时

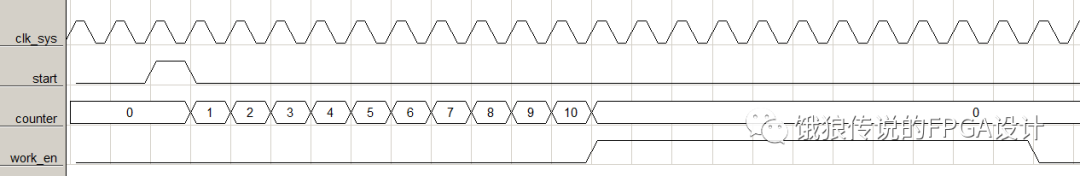

定时是最基本的用法,这个也比较好理解,就是当某个条件出现后,启动计数器计数,当计数到一定的数值后,开启另一个动作。比如下面的时序图所示:当start信号出现后,启动计数器开始计数,计到10以后,计数器清0,同时启动work_en信号,指示后续逻辑开始工作。

2、辅助控制

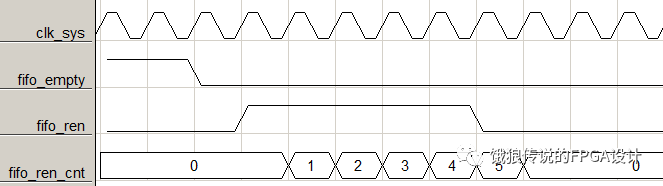

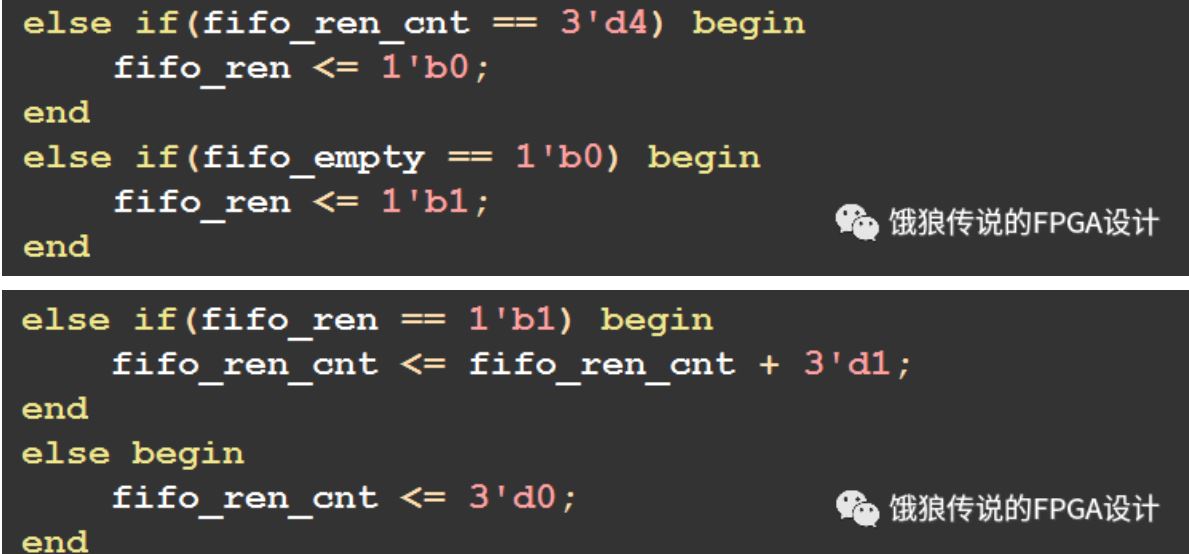

在处理控制信号的时候,需要对控制信号保持一定的时钟周期,常用的就是用计数器来计算这个时钟周期数,帮助控制信号置1或者清0,比如一个fifo,每次读使能有效的时候,需要固定的读5拍数据。这时候就可以用一个计数器来控制读使能的周期数,时序图和代码如下图所示:

3、队列调度

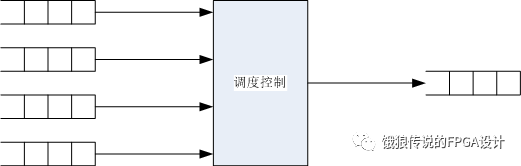

当多个输入队列的数据同时输出到一个队列时,如果对性能的需求不高,可以通过计数器来确定需要调度的队列,简化整个控制逻辑。比如如下图所示:4个队列的数据调度到同一个输出队列。

不考虑调度性能(比如调度索引信息,对性能要求相对较低),可以采用一个计数器,0/1/2/3不断的计数,当计数器为0的时候,如果队列0不空,就把队列0的索引读出来,写到输出fifo,否则队列0不做任何处理;当计数器为1的时候,如果队列1不空,就把队列1的索引读出来,写到输出fifo,否则队列1不做任何处理;当计数器为2和3的时候,处理同上。

以上为3种比较常见的计数器使用,尤其是前2种,使用的非常的广泛。计数器使用虽然方便,但是也有一些需要注意的地方,否则会给你的系统带来灾难。

1、计数器建议要有清0,或者归位的条件。比如场景1中所述的,计数到10后清0,场景2中所述的fifo_ren为0的时候清0,否则非影响下一次的计数。如果不清0,计数器就必须要有置位的条件。

2、计数器要有计数的条件,不能自由计数。即计数器的计数一定是有条件触发的。

3、要注意计数器的位宽,位宽少了,有可能永远都计不到你需要的值。