本文转载自:缘来是你远去是我的CSDN博客

1. 时序约束的概念和基本策略

答:时序约束主要包括周期约束,偏移约束,静态时序路径约束三种。通过附加时序约束可以综合布线工具调整映射和布局布线,是设计达到时序要求。

策略:附加时序约束的一般策略是先附加全局约束,然后对快速和慢速例外路径附加专门约束。附加全局约束时,首先定义设计的所有时钟,对各时钟域内的同步元件进行分组,对分组附加周期约束,然后对FPGA输入输出PAD附加偏移约束、对全组合逻辑的PAD TO PAD路径附加约束。附加专门约束时,首先约束分组之间的路径,然后约束快、慢速例外路径和多周期路径,以及其他特殊路径。

2. 时序约束的目的

答:FPGA时序约束的目的是:

1)提高设计的工作频率(减少了逻辑和布线延时);

2)获得正确的时序分析报告;(静态时序分析工具以约束作为判断时序是否满足设计要求的标准,因此要求设计者正确输入约束,以便静态时序分析工具可以正确的输出时序报告)

3)指定FPGA的电气标准和引脚位置。

3. Vivado约束文件中应该对时钟进行哪些约束?

在Vivado中,时钟约束是通过设计约束文件(.xdc文件)来实现的。以下是应该对时钟进行的一些常见约束:

时钟频率:指定时钟的最大频率和最小周期,以确保时序正确性。

create_clock -period

时钟延迟:指定时钟与其它信号之间的延迟或者相位关系。

set_clock_delay -clock

set_clock_latency -clock

create_generated_clock -name

时钟域:定义时钟域,并指定时钟域之间的同步关系。

create_clock -period

set_input_jitter -clock

set_output_jitter -clock

set_false_path -from

set_multicycle_path -from

set_max_delay -from

set_min_delay -from

set_clock_groups -asynchronous -group

set_clock_groups -synchronous -group

时钟缓存:设置FPGA内部的时钟缓存单元,以确保时序正确性和稳定性。

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets

set_property CLOCK_DEDICATED_ROUTE TRUE [get_nets

set_property CLOCK_DEDICATED_ROUTE AUTO [get_nets

需要注意的是,在进行时钟约束时,应该参考芯片厂商提供的相关文档和工具,以帮助精确地进行约束和检查。并且,所有时钟都应该进行约束,而不仅仅是主时钟。

4. 什么情况需要做时序约束?

答:当设计仅有一个时钟信号,且频率低于50MHz,逻辑电路简单(7级以下),不需要对设计进行时序约束。

当设计超过50MHz,或者设计较为复杂时,需要进行时序约束。

5. 时序设计的实质

答:电路设计的难点在时序设计,时序设计的实质就是满足每一个触发器的建立/保持时间的要求。

6. FPGA设计中对时钟的使用?(例如分频等)

答:FPGA芯片有固定的时钟路由,这些路由能有减少时钟抖动和偏差。需要对时钟进行相位移动或变频的时候,一般不允许对时钟进行逻辑操作,这样不仅会增加时钟的偏差和抖动,还会使时钟带上毛刺。

一般的处理方法是采用FPGA芯片自带的时钟管理器如PLL,DLL或DCM,或者把逻辑转换到触发器的D输入。

7. 什么是时钟抖动?

答:时钟抖动是指芯片的某一个给定点上时钟周期发生暂时性变化,也就是说时钟周期在不同的周期上可能加长或缩短。它是一个平均值为0的平均变量。

8. 什么是亚稳态?为什么两级触发器可以防止亚稳态传播?

答:亚稳态是指触发器无法在某个规定的时间段内到达一个可以确认的状态。

使用两级触发器来使异步电路同步化的电路为一位同步器,用来对一位异步信号进行同步。两级触发器可防止亚稳态传播的原理:假设第一级触发器的输入不满足其建立保持时间,它在第一个脉冲沿到来后输出的数据就为亚稳态,那么在下一个脉冲沿到来之前,其输出的亚稳态数据在一段恢复时间后必须稳定下来,而且稳定的数据必须满足第二级触发器的建立时间,如果都满足了,在下一个脉冲沿到来时,第二级触发器将不会出现亚稳态,因为其输入端的数据满足其建立保持时间。

同步器有效的条件:第一级触发器进入亚稳态后的恢复时间 + 第二级触发器的建立时间 <= 时钟周期。

9. 如何防止亚稳态?

答:解决方法:1 降低系统时钟

2 用反应更快的FF

3 引入同步机制,防止亚稳态传播

4 改善时钟质量,用边沿变化快速的时钟信号,关键是器件使用比较好的工艺和时钟周期的裕量要大。

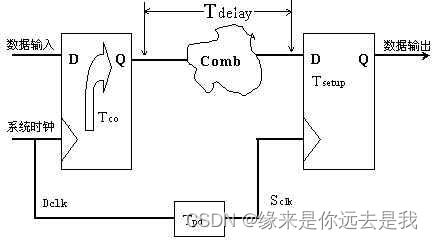

10. 统最高速度计算(最快时钟频率)和流水线设计思想

答:同步电路的速度是指同步系统时钟的速度,同步时钟愈快,电路处理数据的时间间隔越短,电路在单位时间内处理的数据量就愈大。假设Tco是触发器的输入数据被时钟打入到触发器到数据到达触发器输出端的延时时间;Tdelay是组合逻辑的延时;Tsetup是D触发器的建立时间。假设数据已被时钟打入D触发器,那么数据到达第一个触发器的Q输出端需要的延时时间是Tco,经过组合逻辑的延时时间为Tdelay,然后到达第二个触发器的D端,要希望时钟能在第二个触发器再次被稳定地打入触发器,则时钟的延迟必须大于Tco+Tdelay+Tsetup,也就是说最小的时钟周期Tmin =Tco+Tdelay+Tsetup,即最快的时钟频率Fmax =1/Tmin。FPGA开发软件也是通过这种方法来计算系统最高运行速度Fmax。因为Tco和Tsetup是由具体的器件工艺决定的,故设计电路时只能改变组合逻辑的延迟时间Tdelay,所以说缩短触发器间组合逻辑的延时时间是提高同步电路速度的关键所在。由于一般同步电路都大于一级锁存,而要使电路稳定工作,时钟周期必须满足最大延时要求。

故只有缩短最长延时路径,才能提高电路的工作频率。可以将较大的组合逻辑分解为较小的N块,通过适当的方法平均分配组合逻辑,然后在中间插入触发器,并和原触发器使用相同的时钟,就可以避免在两个触发器之间出现过大的延时,消除速度瓶颈,这样可以提高电路的工作频率。这就是所谓"流水线"技术的基本设计思想,即原设计速度受限部分用一个时钟周期实现,采用流水线技术插入触发器后,可用N个时钟周期实现,因此系统的工作速度可以加快,吞吐量加大。注意,流水线设计会在原数据通路上加入延时,另外硬件面积也会稍有增加。

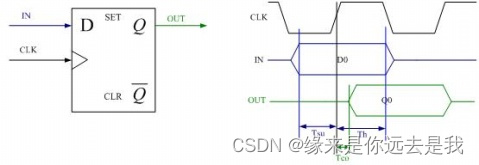

11. 建立时间setup和保持时间holdup时间概念、区别

答:建立时间是指在时钟边沿前,数据信号需要保持不变的时间。如不满足setup time,这个数据就不能被这一时钟打入触发器,只有在下一个时钟上升沿,数据才能被打入触发器。

保持时间是指时钟跳变边沿后数据信号需要保持不变的时间。如果hold time不够,数据同样不能被打入触发器。

图1 建立时间与保持时间示意图

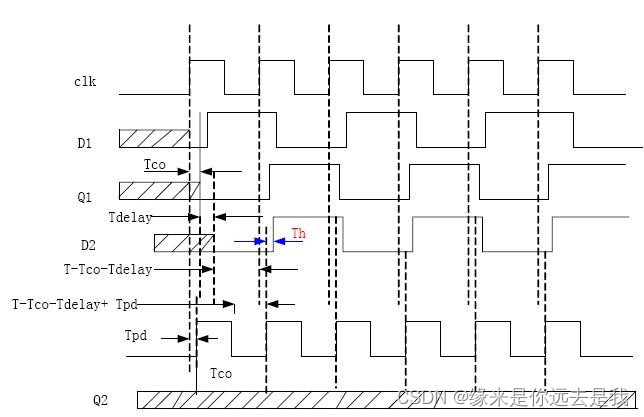

例 1:图2为统一采用一个时钟的同步设计中一个基本的模型。图中Tco是触发器的数据输出的延时;Tdelay是组合逻辑的延时;Tsetup是触发器的建立时间;Tpd为时钟的延时。如果第一个触发 器D1建立时间最大为T1max,最小为T1min,组合逻辑的延时最大为T2max,最小为T2min。问第二个触发器D2立时间T3与保持时间T4应该满足什么条件,或者是知道了T3与T4那么能容许的最大时钟周期是多少?

图2 同步设计中的一个基本模型

为了便于分析,我们讨论两种情况即,第一:时钟的延时Tpd为零。第二:时钟的延时Tpd不为零。

下面通过时序图来分析:设第一个触发器的输入为D1,输出为Q1,第二个触发器的输入为D2,输出为Q2;

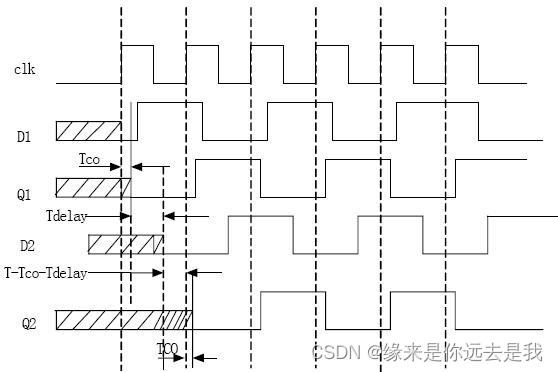

时钟统一在上升沿进行采样,为了便于分析我们讨论两种情况即第一:假设时钟的延时Tpd为零,其实这种情况在FPGA设计中是常常满足的,由于在FPGA设计中一般是采用统一的系统时钟,也就是利用从全局时钟管脚输入的时钟,这样在内部时钟的延时完全可以忽略不计。这种情况下不必考虑保持时间,因为每个数据都是保持一个时钟节拍同时又有线路的延时,也就是都是基于CLOCK的延迟远小于数据的延迟基础上,所以保持时间都能满足要求,重点是要关心建立时间,此时如果D2的建立时间满足要求那么时序图应该如图3所示。

从图中可以看出如果:T - Tco - Tdelay > T3即:Tdelay < T - Tco - T3

那么就满足了建立时间的要求,其中T为时钟的周期,这种情况下第二个触发器就能在第二个时钟的升沿就能稳定的采到D2,时序图如图3所示。

图3 符合要求的时序图

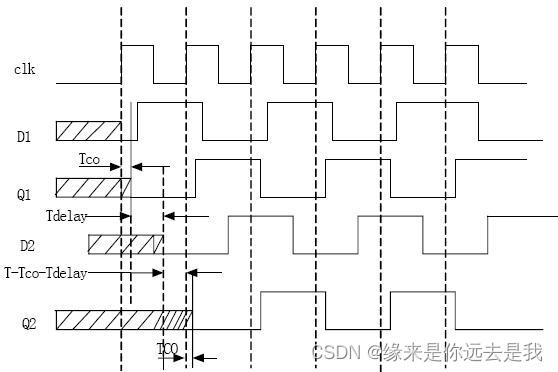

如果组合逻辑延时过大使得 T - Tco - Tdelay < T3

那么将不满足要求,第二个触发器就在第二个时钟的升沿将采到的是一个不定态,如图4所示。那么电路将不能正常的工作。

图4 组合逻辑的延时过大时序不满足要求

从而可以推出T – Tco–T2max >= T3,这也就是要求的D2的建立时间。

从上面的时序图中也可以看出,D2的建立时间与保持时间与D1的建立与保持时间是没有关系的,而只和D2前面的组合逻辑和D1的数据传输延时有关,这也是一个很重要的结论。说明了延时没有叠加效应。

第二种情况如果时钟存在延时,这种情况下就要考虑保持时间了,同时也需要考虑建立时间。时钟出现较大的延时多是采用了异步时钟的设计方法,这种方法较难保证数据的同步性,所以实际的设计中很少采用。此时如果建立时间与保持时间都满足要求那么输出的时序如图5所示。

图5 时钟存在延时但满足时序

从图5中可以容易的看出对建立时间放宽了Tpd,所以D2的建立时间需满足要求:

Tpd+T – Tco–T2max >= T3

由于建立时间与保持时间的和是稳定的一个时钟周期,如果时钟有延时,同时数据的延时也较小那么建立时间必然是增大的,保持时间就会随之减小,如果减小到不满足D2的保持时间要求时就不能采集到正确的数据,如图6所示。

这时即T – (Tpd + T – Tco – T2min) < T4,就不满足要求了,所以D2的保持时间应该为:

T– ( Tpd + T – Tco – T2min ) >=T4 即Tco+T2min – Tpd >=T4

从上式也可以看出如果Tpd=0也就是时钟的延时为0那么同样是要求Tco+T2min > T4,但是在实际的应用中由于T2的延时也就是线路的延时远远大于触发器的保持时间即T4,所以不必要关系保持时间。

图6 时钟存在延时且保持时间不满足要求

下面用数字来说明一下加深理解(以下举例暂不考虑hold time):

建立时间Tsetup=Tdelay+ Tco- Tpd

假设Tco(触发器固有的建立时间)= 2ns

假设1,Clock Delay =0,Data delay="0",那么数据port的新数据必须在时钟port的时钟沿到来之前2ns赶到数据port,才能满足触发器的Tco。

假设2,Clock delay="0",data Delay = 3ns,那么数据port的新数据必须在时钟port的时钟沿到来之前5ns就得赶到数据port,其中的3ns用来使新数据从数据port赶到触发器的D端(由于data Delay),剩下的2ns用来满足触发器的Tco。

假设3,Clock delay="1ns",data Delay = 3ns,由于时钟port的时钟沿推后1ns到达触发器的时钟端,那么数据port的新数据只需在时钟port的时钟沿到来之前4ns赶到数据port即可。

假设4,假设时钟的周期T=4ns,即你的系统需要运行在250M频率上,那么以上的假设中,假设2显然是不成立的,也就是说在假设2的情况下,你的系统运行频率是低于250M的,或者说在250M系统里是有setup time violation的。在假设2的情况下,由于Tco及Tpd均是FPGA的固有特性,要想满足4ns的T,那么唯一你能做的就是想方设法减小Tdelay,也就是数据路径的延时。即所谓的找出关键路径,想办法优化之。

总结,在实际的设计中,对于一个给定的IC,其实我们很容易看到T,Tpd,Tsetup,Th都是固定不变的(在跨时钟域时,Tpd会有不同),那么我们需要关心的参数就是Tdelay,即数据路径的延时,控制好了这个延时,那我们的设计就不会存在建立时间和保持时间不满足的情况了!

例2:有个著名的笔试题,这样说道:时钟周期为T,触发器D1的建立时间最大为T1max,最小为T1min,该触发器的数据输出延时为Tco。组合逻辑电路最大延迟为 T2max,最小为T2min。假设D1在前,D2去采样D1的数据(实际就是对图2的文字描述),问,触发器D2的建立时间T3和保持时间应满足什么条件。这里给出一个简易公式供大家死记一下,

以下两个公式确定了D2的Tsetup和Thold:

1) D1的Tco + max数据链路延时 + D2的Tsetup < T(即T3 < T - Tco - T2max)

2) D1的Tco + min数据链路延时> D2的Thold(即T4< Tco + T2min)

其实上面的式2可以从T3+T4=T推出,不过要注意把1)中的T2max改为T2min即可。总之,建立时间长了,保持时间就短了。

实际中,某条数据链路延时是一个定值,只不过要求它落在区间{T2min,T2max}。这也是T2min和T2max的实际意义。

从现实设计出发,个人觉得这个题改为考T2max和T2min更合适,那是不是有更多人犯晕呢?!hoho