本文转载自: 无界逻辑(微信号:wujieluoji)微信公众号

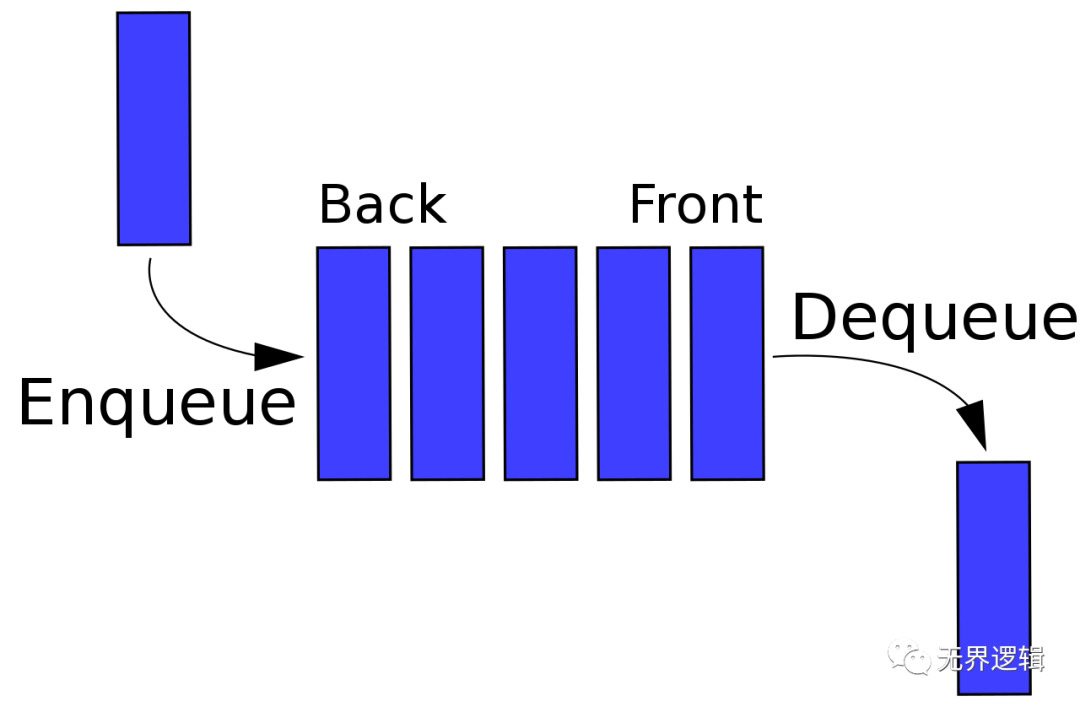

FIFO:First in, first out,先进先出;其主要作用是:数据缓存,位宽转换,时钟域处理,通常作为模块之间的桥梁,存在与逻辑设计中。

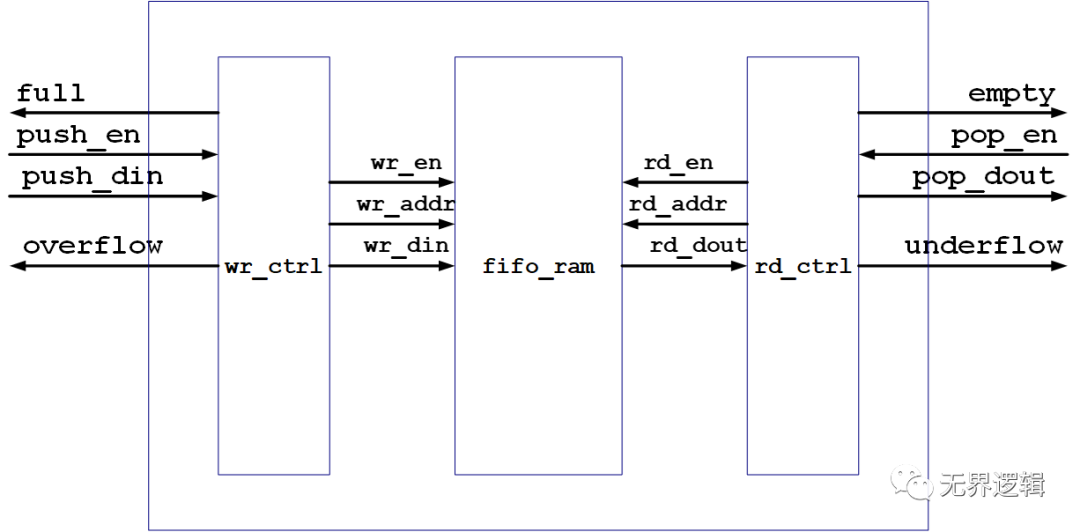

典型同步FIFO由两部分组成:

1.FIFO控制器;

2.FIFO存储实体(Memory、Reg);

其中FIFO控制器包括FIFO写控制逻辑和FIFO读控制逻辑;

FIFO写控制逻辑主要功能:

FIFO读控制逻辑主要功能:

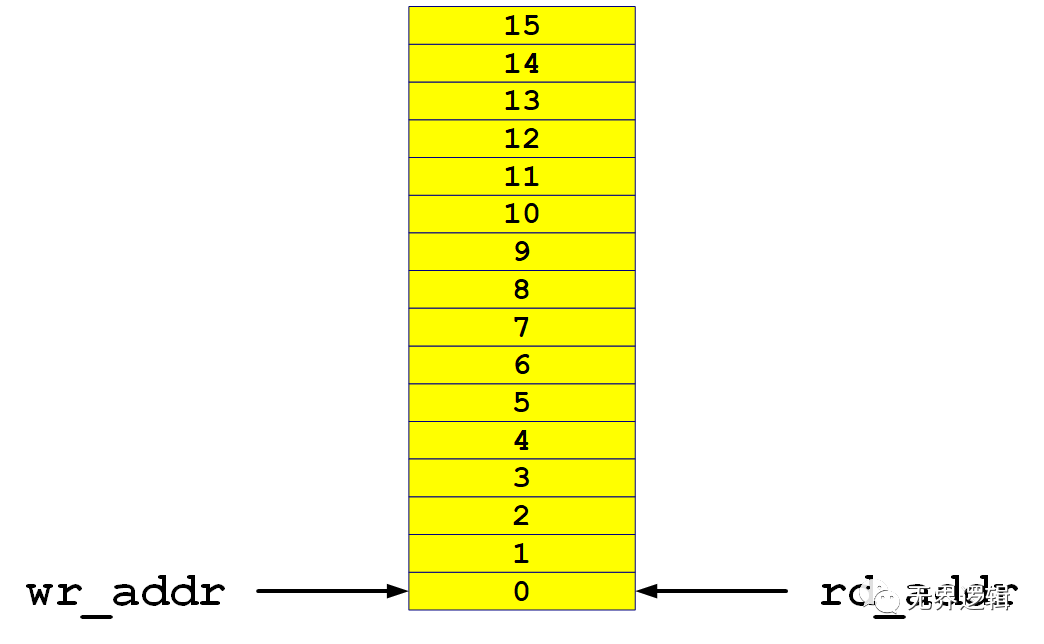

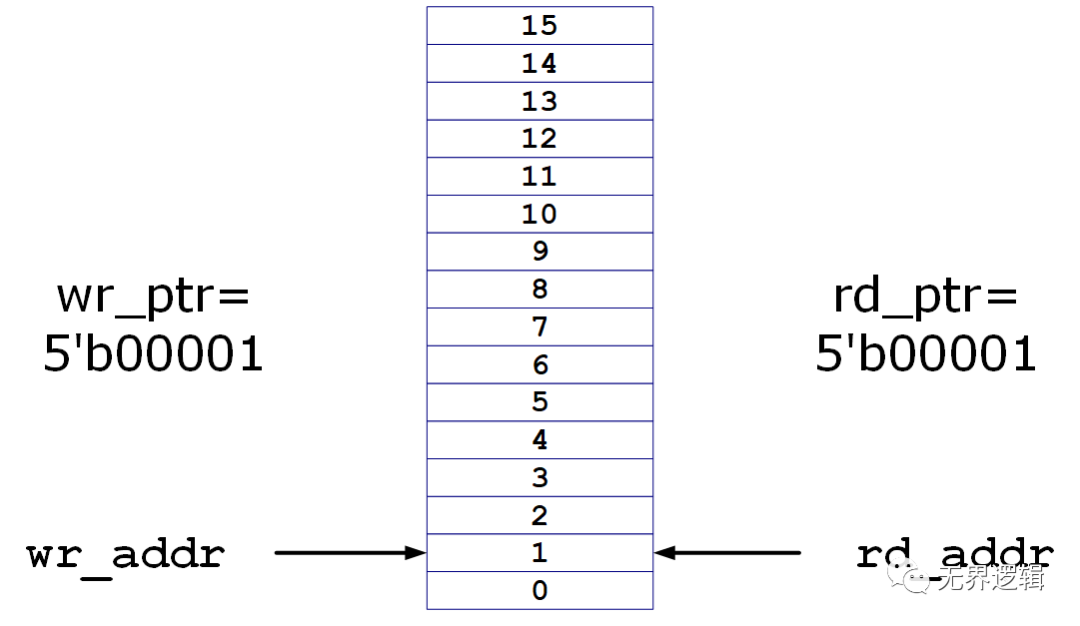

如下图所示,FIFO读写过程的地址控制:

1.当FIFO初始化(复位)时wr_addr与rd_addr同指到0x0,此时FIFO处于空状态;

2.当FIFO进行写操作时,wr_addr递增,与rd_addr错开,此时FIFO处于非空状态;

wr_addr增加到FIFO DEPTH时,发生卷绕,追上了rd_addr,此时FIFO满;

3.当FIFO进行读操作时,fifo_read_addr递增;

可以看出wr_addr==rd_addr是无法区分FIFO是空还是满。

那么,如何判断FIFO空满状态呢?

FIFO空满状态的产生有两种方法:

方法一:为产生FIFO空满标志,引入FIFO Count计数器,FIFO Count寄数器用于指示FIFO内部存储数据个数;

(1)当只有写操作时,FIFO Count加1;只有读操作时,FIFO Count减1;其他情况下,FIFO Count保持;

(2)当FIFO Count为0时,说明FIFO为空,fifo_empty置位;

(3)当FIFO Count等于FIFO_DEPTH时,说明FIFO已满,fifo_full置位;

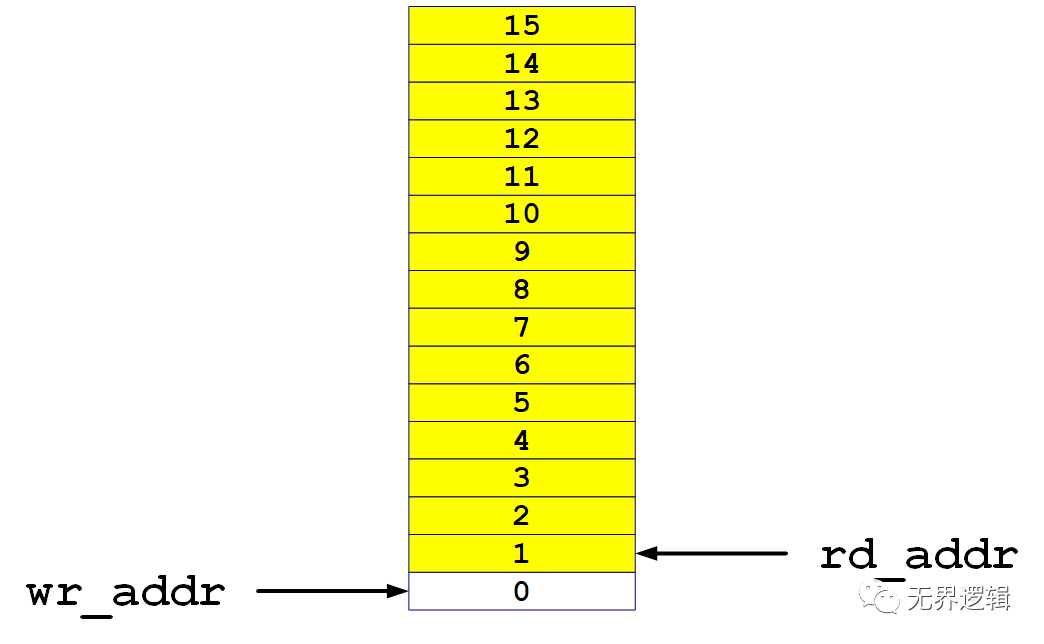

方法二:使用wr_addr和rd_addr判断,如下图所示,wr_addr和rd_addr位宽是4bit就够了,我们扩展一位,设置wr_ptr和rd_ptr为5bit。

当wr_ptr[4:0]==rd_ptr[4:0]时,表示空;

当wr_ptr[4]!=rd_ptr[4] 且wr_ptr[3:0]==rd_ptr[3:0]时,表示满;写指针已经转了一圈追上了读指针;

FIFO溢出状态产生:

(1)当fifo空时,继续发起pop操作,则fifo下溢。

(2)当fifo满时,继续发起push操作,则fifo上溢。

同步FIFO设计是不是很简单?

特别需要你掌握的是FIFO空满判断的第二种方法;