本文转载自:FPGA的现今未

最近有人私信问了一个问题,如何设计占空比为50%的三分频电路。一看到这个话题,突然想起了与它的点点滴滴。虽然三分频在上学的时候就已经会了,但是在毕业找工作的面试中,以及前几年的准备跳槽的面试中都忘记了……刚好在这里回忆下。

非50%占空比的三分频

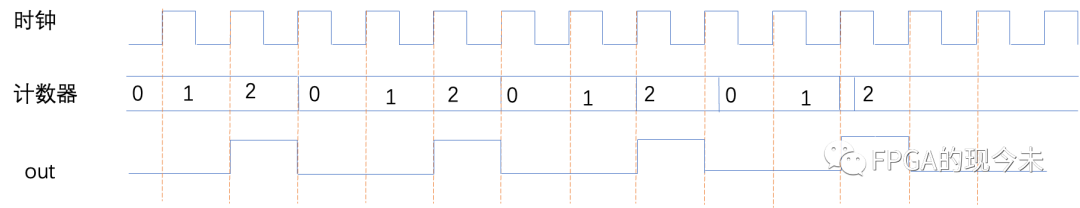

对于三分频,如果不考虑占空比,那其实是非常简单的一个问题,直接上一个波形图:

这是占空比为1/3的波形图,通过一个简单的计数器即可实现。

50%占空比的三分频

那么对于占空比为50%的三分频电路如何处理呢?这也是面试中问的比较多的一个问题,为了讨论问题的简单,我们这里讨论三分频,然后给出N(奇数)分频的通用解法。对于50%占空比的三分频时序如下图所示:

1、产生一个N=3的计数器cnt;

2、产生2个单脉冲信号(en_1和en_2),这里其实就是产生2个占空比为1/3的三分频信号,其中en_1在cnt=0的时候产生,en_2在cnt=2的时候产生。PS:如果是任意奇数分频,比如N分频,那en_2在cnt=(N+1)/2的时候产生;

3、分别对en_1和en_2做翻转。对于en_1,采用时钟的上升沿对其采样,当en_1=1的时候翻转一次,得到信号div_1;对于en_2,采用时钟下降沿对其采样,当en_2=1的时候翻转一次,得到信号div_2;

4、将div_1和div_2做异或即得到3分频电路,即上图中的out信号。

我们可以看到out信号的上升沿和时钟的上升沿对齐,但是out信号的下降沿和时钟的下降沿对齐。

总结

不知道为啥数字设计面试的时候比较流行这个题目,对于应届生的面试还可以理解说是为了考察基本功,但是社招的面试的时候聊这个题目感觉就没有意义了,毕竟工作中从来不会这么用。