本文转载自:FPGA开源工作室

1. DDS IP概述

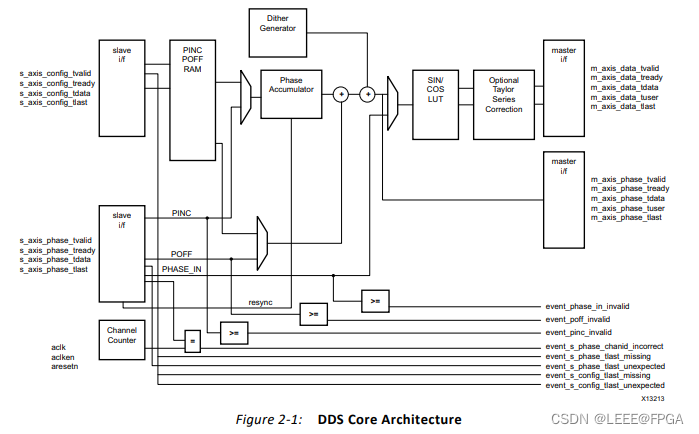

直接数字合成器(DDS)或数控振荡器(NCO)是许多数字通信系统中的重要部件。正交合成器用于构造数字下变频器和上变频器、解调器,并实现各种类型的调制方案,包括PSK(相移键控)、FSK(频移键控(frequency shift keying))和MSK(minimum shift keyed)。数字生成复数或实数正弦曲线采用查找表方案。查找表存储正弦曲线的样本。数字积分器用于生成合适的相位自变量,该相位自变量由查找表映射到期望的输出波形。简单的用户界面接受系统级参数,例如所需的输出频率和所生成波形的杂散抑制。

•相位生成器和SIN/COS查找表可以单独生成,也可以与可选抖动一起生成,以提供完整的DDS解决方案。

•光栅化功能消除了相位截断产生的相位噪声。

•正弦、余弦或正交输出。

•可选的累积相位的每通道重新同步。

•查找表可以存储在分布式或块RAM中。

•可选相位抖动扩展谱线能量,以获得更大的杂散自由动态范围(SFDR)。

•相位抖动或泰勒级数校正选项使用最少的FPGA资源提供高动态范围信号。支持18dB到150dB的SFDR。

•多达16个独立的时分复用信道。

•使用高达48位相位累加器的精细频率分辨率,带有DSP切片或FPAGA逻辑选项。

•3位至26位带符号输出采样精度

IP 文档连接:PG141

2. DDS IP 架构

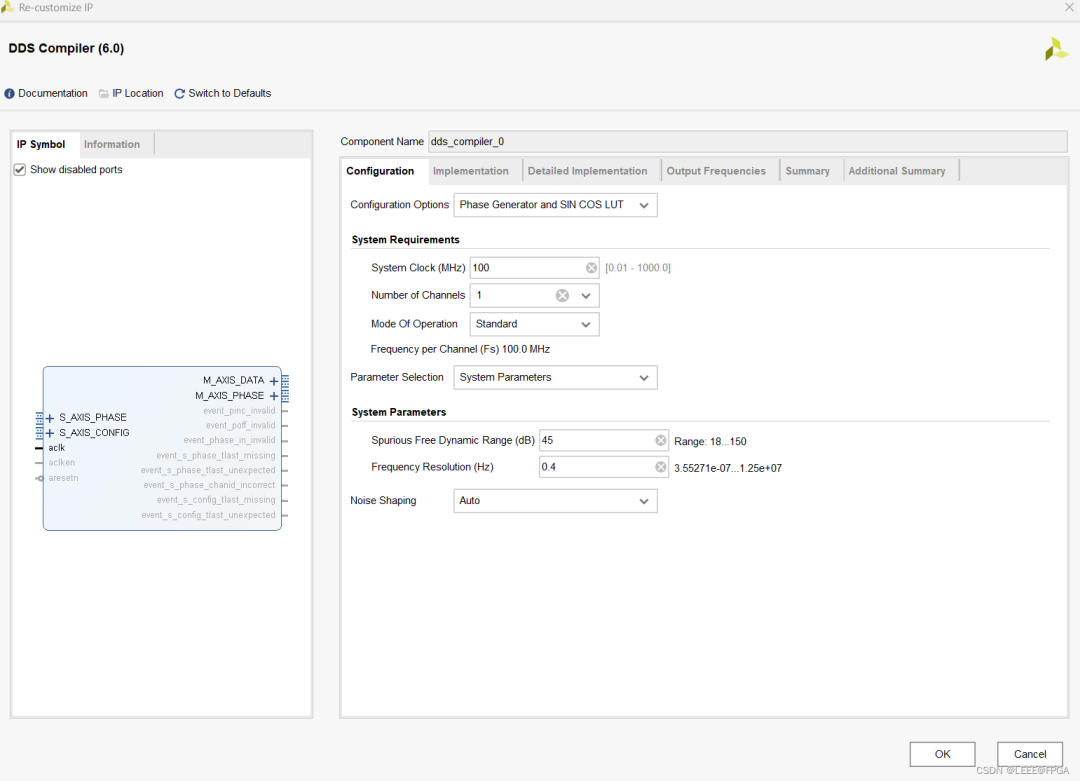

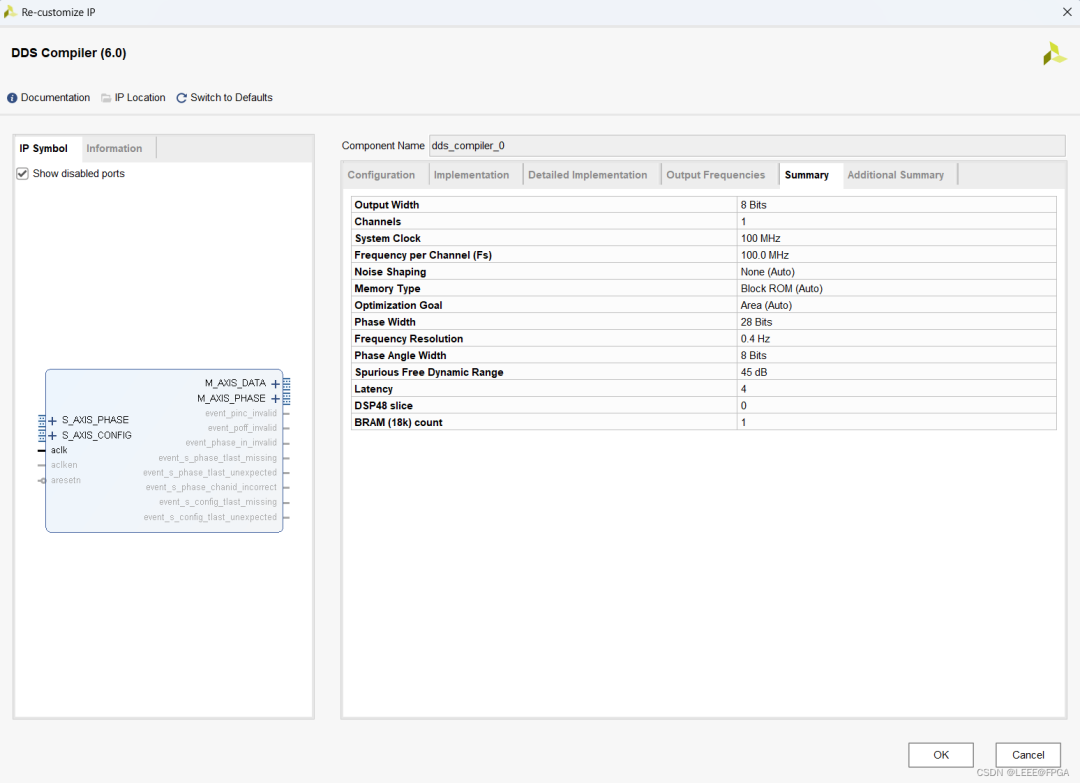

3. DDS IP 配置

(1)Component Name 可以修改IP核名字

(2)Configuration options 配置选项:这里我们选择phase generator and sin cos LUT

(3)system clock(系统时钟) 100MHz(范围0.01—1000MHZ);通过奈奎斯特定理可知,最大输出的频率为50MHz,实际测得输出最大频率为50MHz,当输出的频率超过25MHz的时候频率就开始不稳定;要想输出更大的频率,可以通过增加系统时钟来实现;

(4)Number of channels(通道数选择) 1;最多可以选择16个通道输出,本项目为实现任意可调频率输出只用到单通道输出即可;

(5)Frequency per channel (每通道频率)100MHz;通过系统时钟除以通道数得到每通道的频率;

(6)Parameter selection (参数选择) system parameters;系统参数,为了更精确的输出任意频率,选择系统参数模式;

(7)Spurious free dynamic range(伪动态自由范围)48(决定输出正余弦数据位宽n,范围为6*(n-1)~6*n,后面选择正弦或者余弦输出时位宽为8位,如果正余弦同时输出则位宽为16位,正弦为高8位,余弦为低8位)

(9)Frequency resolution(频率分辨率) 0.02910383045673370361328125(决定相位位宽,由相位位宽函数可得出频率分辨率,分辨率越精确,可调输出频率越精确,相位位宽函数在后面讲到)

(10)Noise shaping(噪声整形):控制是否相位截断、抖动或泰勒级数校正使用;

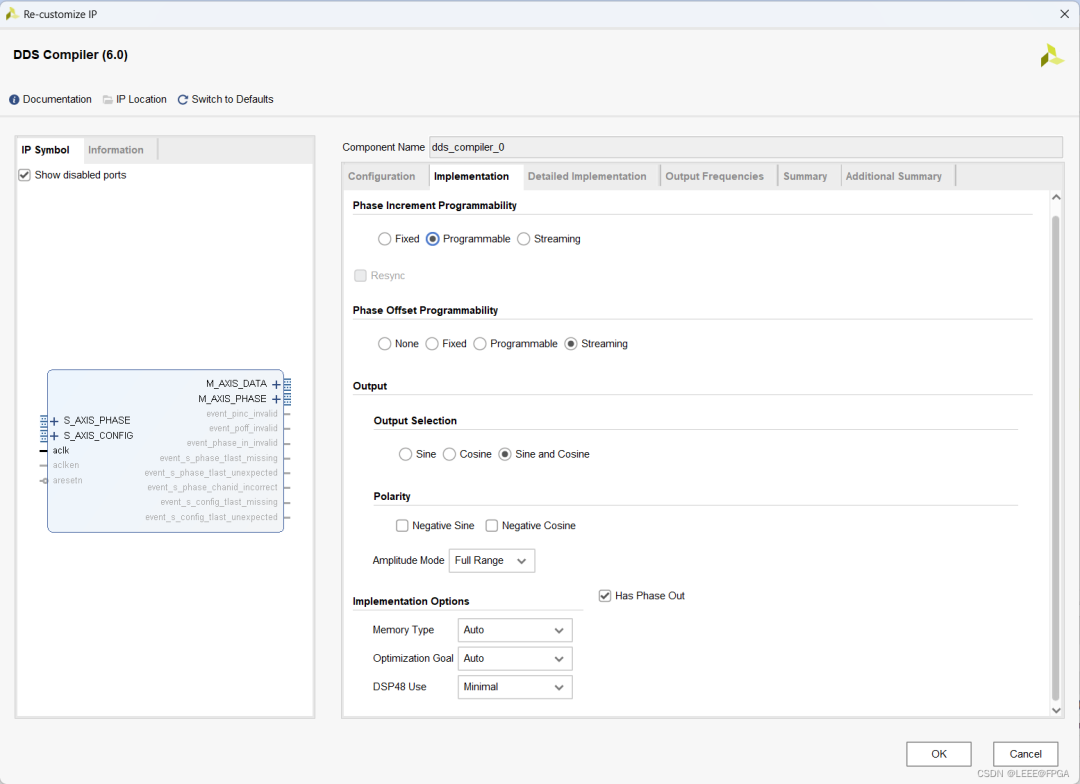

1)Phase increment programmability(相位增量可编程性)

Fixed(固定模式);固定输出频率,不可任意调整;

Programmable(可编程模式);根据设计需求选择相位增量可编程模式,通过频率输出函数可知,输入不同相位增量时可输出不同频率,频率输出函数后面讲到;

Streaming(流水模式);

(2)Phase offset programmability

None(无);选择无相位偏移;

Fixed(固定模式);固定相位偏移;

Programmable(可编程模式);可以调整波形相位;

Streaming(流水模式);

(3)Output selection(输出选择)

Sine and cosine(正弦和余弦);如果用到正弦和余弦同时输出,则高8位表示正弦输出,低8位表示余弦输出;

Sine(正弦);选择正弦输出即可;

Cosine (余弦);

(4)Polarity (极性)没用上,不用选;

Negative sine(负极性正弦);

Negative cosine(负极性余弦);

(5)Implementation options(实现选项)

Memory type(内存类型:它控制SIN/COS查找表的实现):auto默认选择自动、distribution rom(分布rom)、block rom(块rom)

Optimization goal(优化目标:选择控制实现决策的目标是最高速度还是最低资源):auto默认选择自动、area(区域)、speed(速度)

DSP48 use(控制相位累加器和后续添加阶段(相位偏移或抖动噪声添加)的实现):minimal(默认最小)、maximal(最大)

4. FPGA 实验

调用DDS IP核实现扫频信号,我这里设计的扫频范围是1KHz–10KHz,通过控制频率控制字来更改输出的波形的频率,让其在1KHz到10KHz直接变化,又让其从10KHz变化到1KHz。

DDS_top:

module dds_top(

input wire aclk,

input wire reset_n,

output valid,

output signed [7:0] sin,

output signed [7:0] cos

);

wire s_axis_phase_tvalid;

wire [31 : 0] s_axis_phase_tdata;

wire s_axis_config_tvalid;

wire [31 : 0] s_axis_config_tdata;

wire m_axis_data_tvalid;

wire [15 : 0] m_axis_data_tdata;//输出为16位,高8位是sin波形,低8位是cos波

wire m_axis_phase_tvalid;

wire [31 : 0] m_axis_phase_tdata;

assign valid = m_axis_data_tvalid;

assign sin =m_axis_data_tdata[15:8];

assign cos =m_axis_data_tdata[7:0];

dds_ctl Udds_ctl(

.aclk(aclk),//100mhz

.reset_n(reset_n),

.phase_tvalid(s_axis_phase_tvalid),

.phase_tdata(s_axis_phase_tdata),

.config_tvalid(s_axis_config_tvalid),

.config_tdata(s_axis_config_tdata)

);

dds_compiler_0 UDDS (

.aclk(aclk), // input wire aclk

.s_axis_phase_tvalid(s_axis_phase_tvalid), // input wire s_axis_phase_tvalid

.s_axis_phase_tdata(s_axis_phase_tdata), // input wire [31 : 0] s_axis_phase_tdata

.s_axis_config_tvalid(s_axis_config_tvalid), // input wire s_axis_config_tvalid

.s_axis_config_tdata(s_axis_config_tdata), // input wire [31 : 0] s_axis_config_tdata

.m_axis_data_tvalid(m_axis_data_tvalid), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata), // output wire [15 : 0] m_axis_data_tdata

.m_axis_phase_tvalid(m_axis_phase_tvalid), // output wire m_axis_phase_tvalid

.m_axis_phase_tdata(m_axis_phase_tdata) // output wire [31 : 0] m_axis_phase_tdata

);

endmodule

dds_ctl

//config_tdata -- detla=Fout*2^32/Fclk

module dds_ctl(

input aclk,//100mhz

input reset_n,

output wire phase_tvalid,

output wire [31 : 0] phase_tdata,

output wire config_tvalid,

output wire [31 : 0] config_tdata

);

//参数定义

parameter F_word_1KHz = 32'hA7C5 ;//1KHz频率控制字 M = 1_000*2^32/100_000_000

parameter F_word_10KHz = 32'h68DB8 ;//10KHz频率控制字 M = 10_000*2^32/100_000_000

parameter F_word_change = 32'h1 ;//1KHz-10KHz变化精度

//信号定义

reg [31:0] config_data_reg ;//频率控制字寄存器

reg max_flag ;//当频率控制字最大时,拉高

//max_flag

always @(posedge aclk or negedge reset_n)begin

if(!reset_n)begin

max_flag <= 1'b0;

end

else if(config_data_reg >= F_word_10KHz)begin

max_flag <= 1'b1;

end

else if(config_data_reg == F_word_1KHz)begin

max_flag <= 1'b0;

end

end

//控制频率控制字均匀变化

always @(posedge aclk or negedge reset_n)begin

if(!reset_n)begin

config_data_reg <= F_word_1KHz;

end

else if(max_flag == 1'b1)begin

config_data_reg <= config_data_reg - F_word_change;

end

else begin

config_data_reg <= config_data_reg + F_word_change;

end

end

//输出

assign phase_tvalid = 1'b1;

assign phase_tdata = 32'h0;//设置相位控制字为0

assign config_tvalid = 1'b1;

assign config_tdata = config_data_reg;

endmodule

tb

`timescale 1ns / 1ps

module tb(

);

reg aclk;

reg reset_n;

wire valid;

wire signed [7:0] sin;

wire signed [7:0] cos;

initial begin

aclk =0;

reset_n =0;

#1000;

reset_n =1;

end

always #(5) aclk =~aclk;

dds_top Udds_top(

.aclk(aclk),

.reset_n(reset_n),

.valid(valid),

.sin(sin),

.cos(cos)

);

endmodule

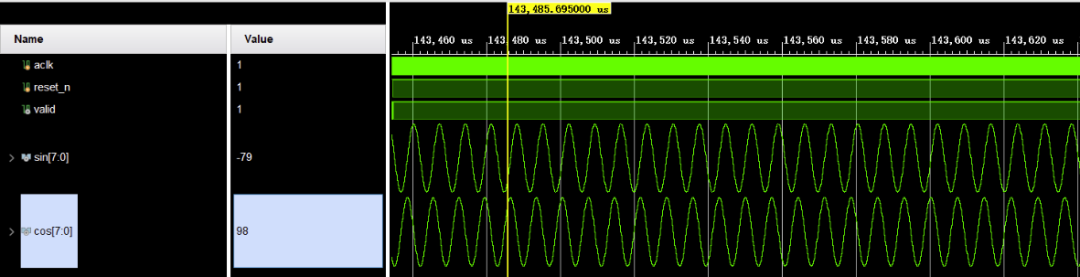

仿真波形: