本文转载自:OpenFPGA

实现 FPGA 设计最耗时的要素之一通常不是设计,而是实现想要的时序性能。为了实现所需的时序收敛,我们可能需要通过插入流水线并使用约束来准确定义时钟、它们的关系甚至逻辑元件的位置来调整设计。

Vivado 具有许多功能可用于帮助我们了解设计的实现以及实现中可能出现的问题。这些工具之一是设计分析报告(The Design Analysis Report),它使用户能够了解设计挑战(例如拥塞)并对设计或约束进行更改。

设计分析报告可以通过在 GUI 中打开或通过 TCL 控制台生成。它将提供以下信息:

. 时序– 提供有关路径的时序和物理特性的信息。

. 复杂性– 提供有关布线复杂性和 LUT 分布的信息。

. 拥塞– 提供有关路由拥塞的信息。

让我们看一下在实例上的设计报告。该项目具有 MicroBlaze 处理器、DDR 内存和定制 RTL 模块。

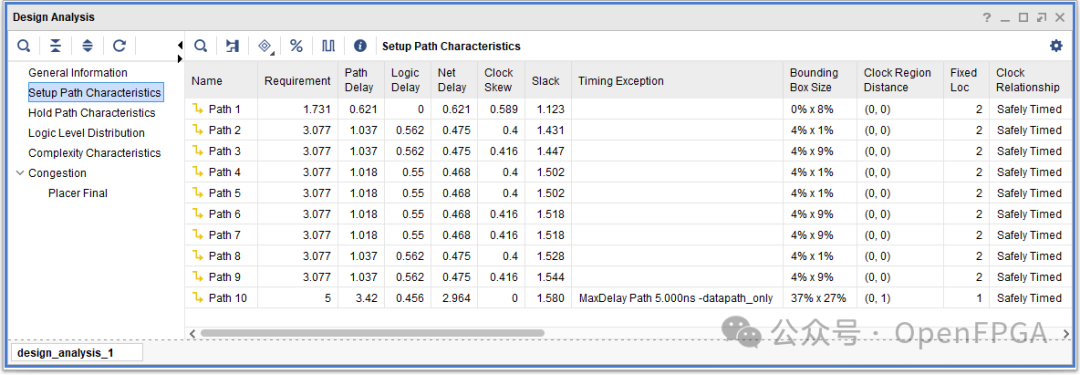

使用“报告设计分析”对话框,可以配置时序分析以仅提供建立(最大)或保持信息(最小值)或同时提供建立和保持(min_max)。

我们还可以选择时序报告的最大路径数。在此示例中,报告了十个最差的建立和保持路径。在“ Timer Settings”选项上,如果需要,可以选择互连时序、设备速度等级和multi-corner配置。

一个非常有趣的选项是在时序中设置逻辑电平分布选项。此选项将报告按时钟驱动的逻辑级别数量。

通过点击特定的路径,我们可以打开时序路径并获取特定时序路径的更多信息。

报告时序路径将提供关于具有选定数量的逻辑电平的时序路径的详细信息。

为了获得有关时序路径的更多信息,可以生成有关从起点到终点的特定路径的更详细的时序报告。

正如预期的那样,时序报告提供了大量信息,包括:

. 路径要求——低于 2 ns 的路径要求很难满足,尤其是在较旧的设备上。还必须仔细考虑低于 4 ns 的路径要求。

. 数据路径– 如果逻辑延迟大于总延迟的 50%,设计人员需要检查数据路径逻辑深度和单元类型。纠正逻辑延迟需要修改 RTL 或综合选项。如果网络延迟在布线中占主导地位,则应检查物理特性(例如高扇出)。

. 逻辑路径– 检查 CLR、PRE、RDT 和 CE 等端点,这些端点可能是由控制结构产生的高扇出网络。检查 DSP 和 BRAM 是否具有输出寄存器以提高时序性能。

. 物理– 检查 IO 列或 SLR 边界的交叉,这会导致高网络延迟或大偏差。还可以检查因过度的平面规划而导致的过于激进的布局限制。

. 属性– 检查设计中使用的属性,包括 LUT 组合,这可以节省逻辑利用率,但也会增加拥塞。

复杂性分析将报告租金指数(rent exponent,它是网表分区的端口数和单元数之间的关系)、平均扇出和叶单元的分布。在设计分析报告中,租金指数和扇出表明了设计的复杂性和潜在的布局布线问题。

如果租金指数低于 0.65 并且扇出低于 4,则该设计被视为低风险,预计不会出现布局布线问题。在 0.65 和 0.85 之间以及扇出在 4 和 5 之间,复杂性被认为很高,并且设计可能难以在不拥塞的情况下进行布局。设计复杂性非常高,租金指数高于 0.85,扇出约为 5。在这种情况下,设计在综合实现过程中可能会失败。

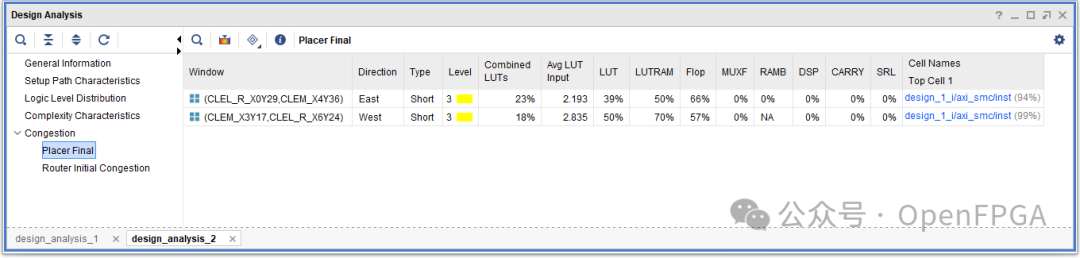

设计分析的最后一个要素是拥塞报告。这将显示 CLB 块中的拥塞情况。当关键路径位于拥塞区域时,拥塞可能会导致时序问题。

拥堵情况报告为八个级别。除非时序要求很严格,否则 3 级或更低级别不是问题。4 – 5 级可能会导致时序收敛问题,并且可能需要其他技术(例如,扩展逻辑策略)。

如果拥塞大于6,设计很可能无法满足时序并且可能无法实现。

使用设计分析报告,我们可以探索当我们尝试通过调整 RTL、约束或工具设置来实现时序收敛时可能导致问题的设计区域。设计分析报告为我们提供了正确指引,确保我们的努力可以取得最佳结果。