文章来源:FPGA入门到精通

本系列文章将详细介绍Vivado软件的使用方法,帮助初学者快速掌握AMD FPGA开发。

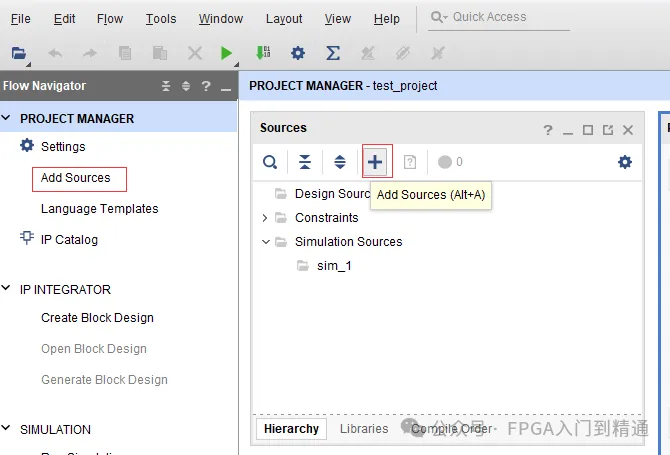

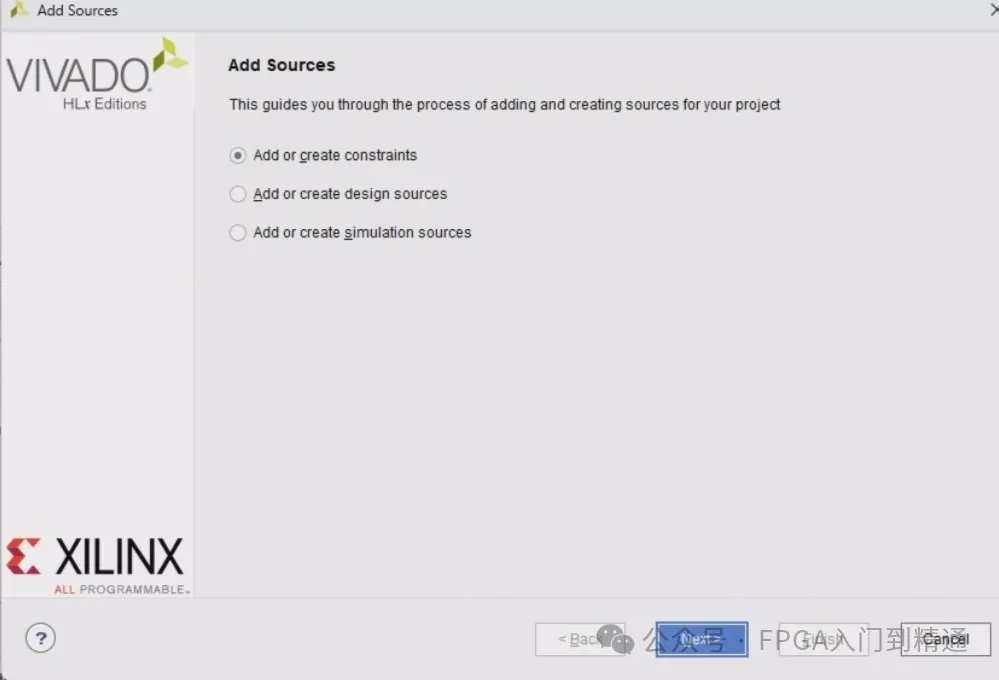

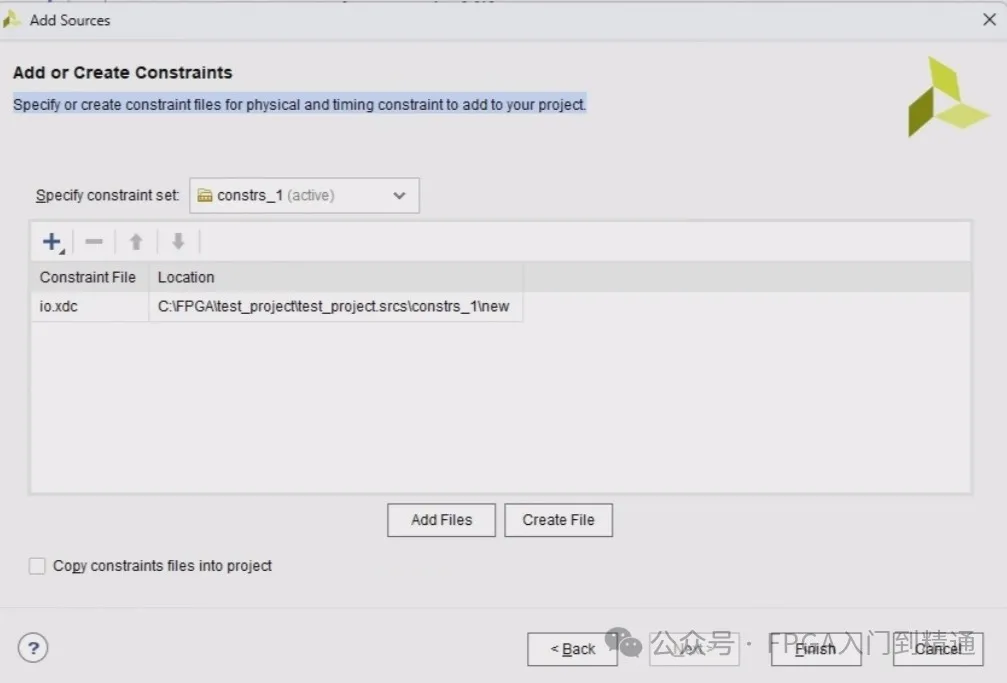

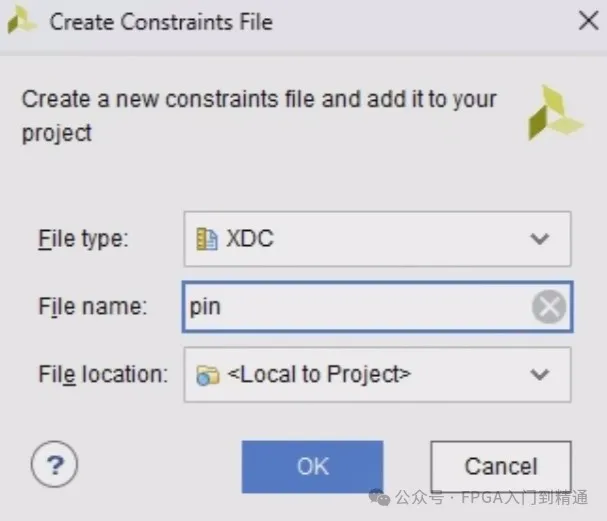

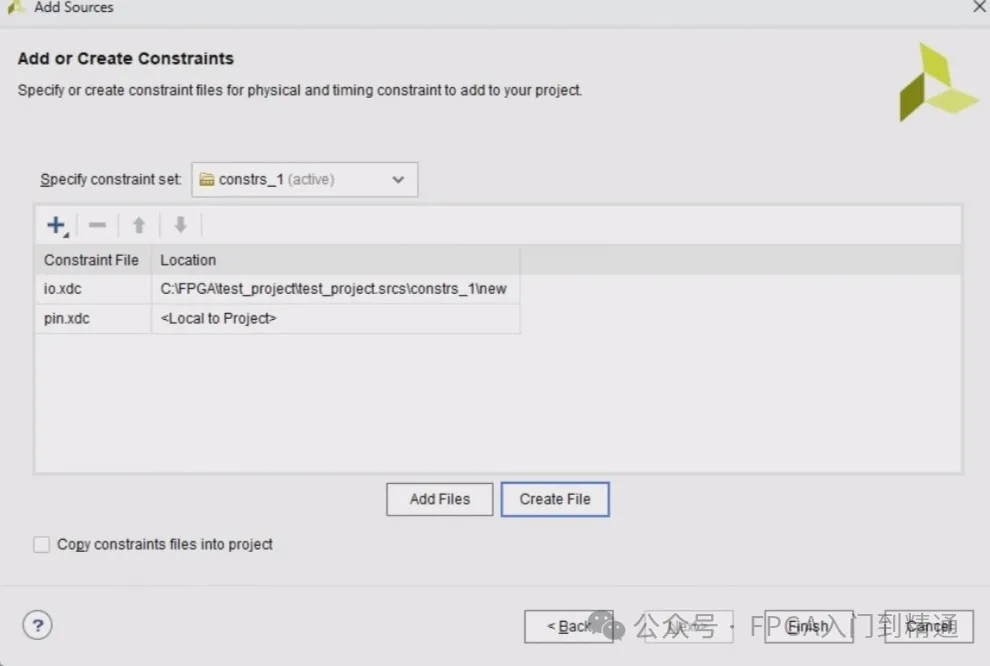

本文将详细介绍vivado添加或新建约束文件步骤和方法。

一、什么是约束文件?

FPGA约束文件,简单来说,就是用来告诉FPGA芯片上的组件们怎么摆放位置,以及它们之间如何连接的一组规则。

想象一下你要装修房子,你会有一个设计图,上面标明了家具怎么摆放,电路怎么布置。FPGA约束文件就类似这个设计图,不过它是给FPGA芯片用的。

这个文件里面会包括各种信息,比如哪些信号线要连接到哪个引脚上,哪些信号是时钟信号,它们的工作频率是多少,还有各个信号之间的时序关系等。

FPGA在配置的时候会根据这些约束来优化硬件的布局和布线,确保设计能够按照预定的方式工作。

如果你要设计一个基于FPGA的系统,写好约束文件是非常关键的,它直接影响到你的设计能否正确实现,以及性能如何。

这就好比你要装修房子,设计图不准确,可能会导致家具放不下,电路有问题,所以一定要认真对待。

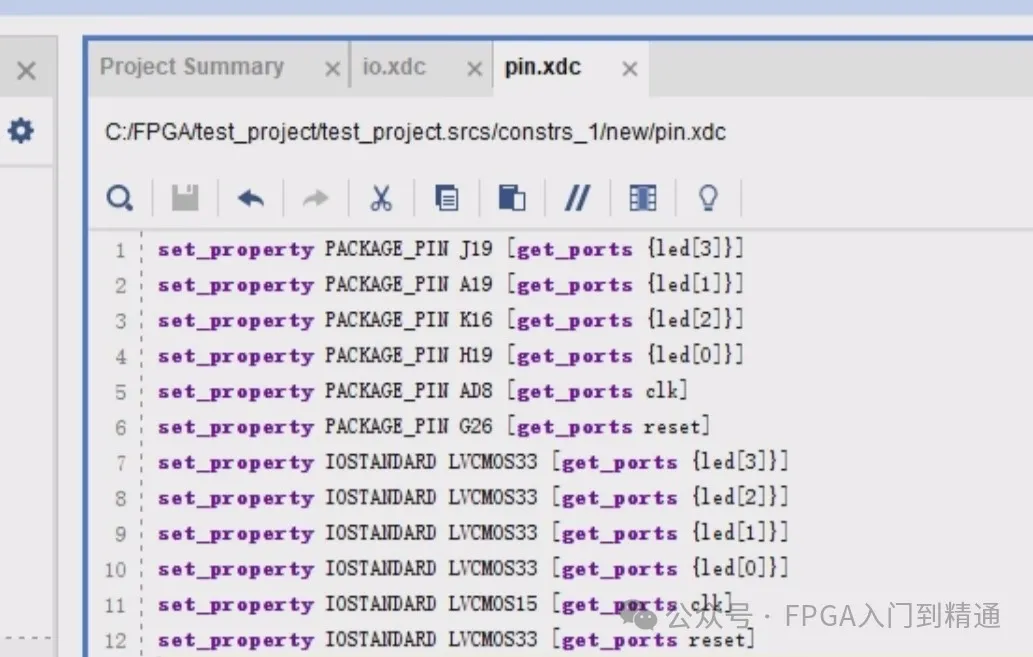

FPGA约束文件通常可以分为时序约束 (Timing Constraints)、引脚约束 (Pin Constraints)。

时序约束:用于指定设计中的时钟和数据路径的时序要求。

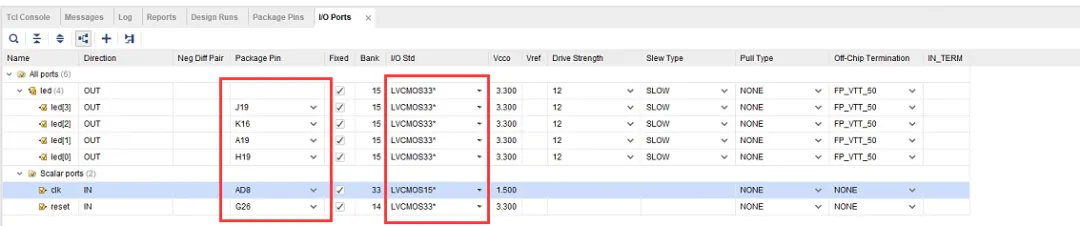

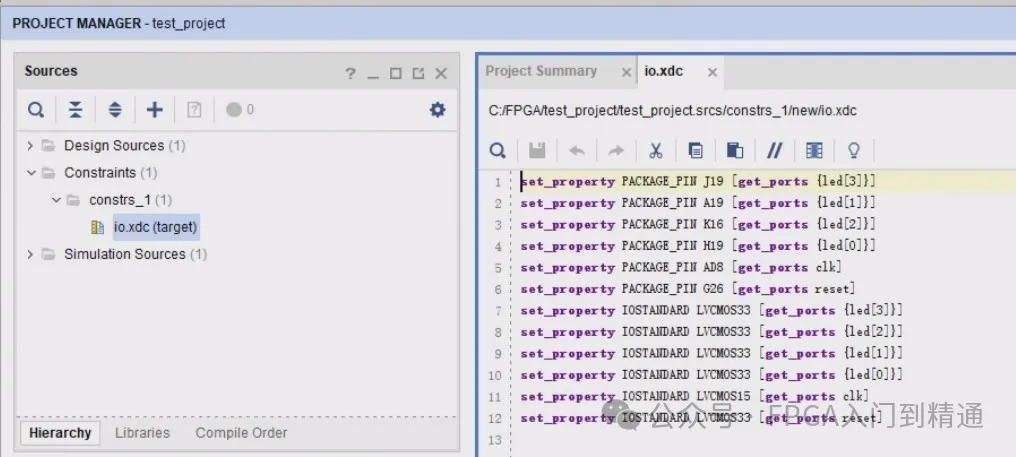

引脚约束:用于指定特定信号应该映射到FPGA芯片的引脚分配、I/O标准和引脚电压等。

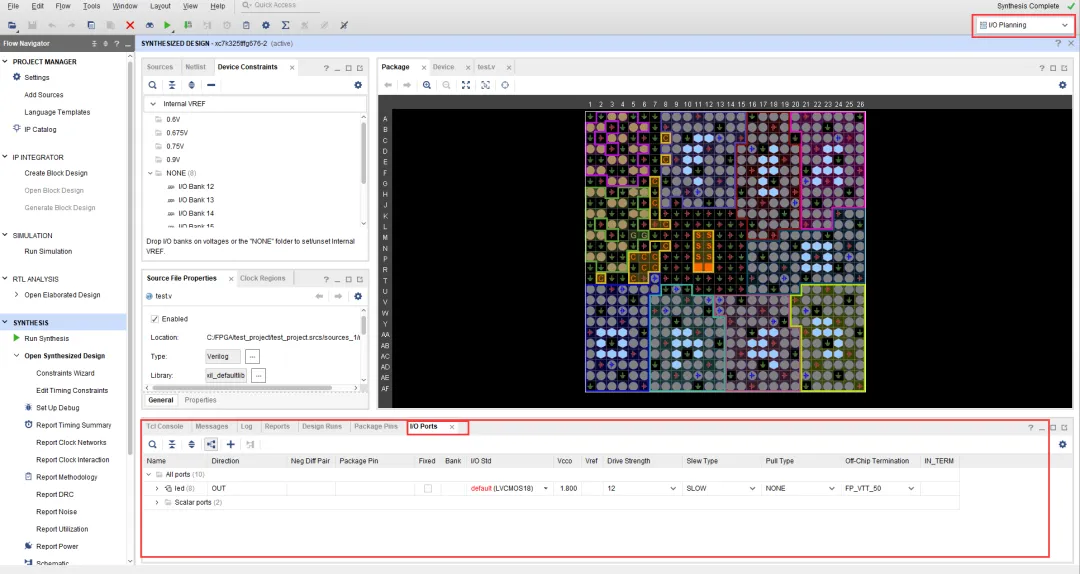

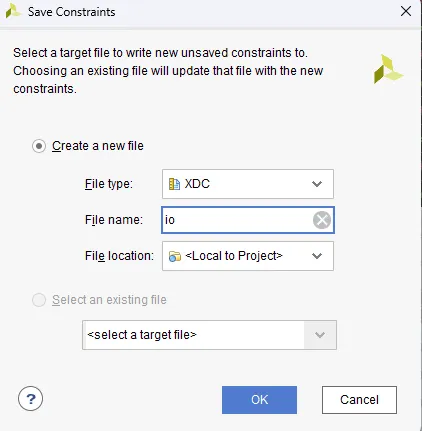

1、Vivado 中 IO planning 功能