作者: FPGA的现今未

最近在一个项目中,使用的单板是一块老单板,因为外部接口刚好满足需求,所以就拿过来直接用了。单板上的FPGA是K7 325T的芯片,项目使用的资源LUT不到20%,REG不到10%,但是偶尔有一些时序问题……

问题分析

对于一个占用资源如此少的项目,以团队的经验按理来说是不应该有时序问题的。我们通过时序分析报告,发现时序分析不通过原因是几条线路的走线比较长导致的。本想在device中看看到底有多长,但是突然发现,整个FPGA的资源全部集中在芯片的下面部分,它大体是这么个样子:

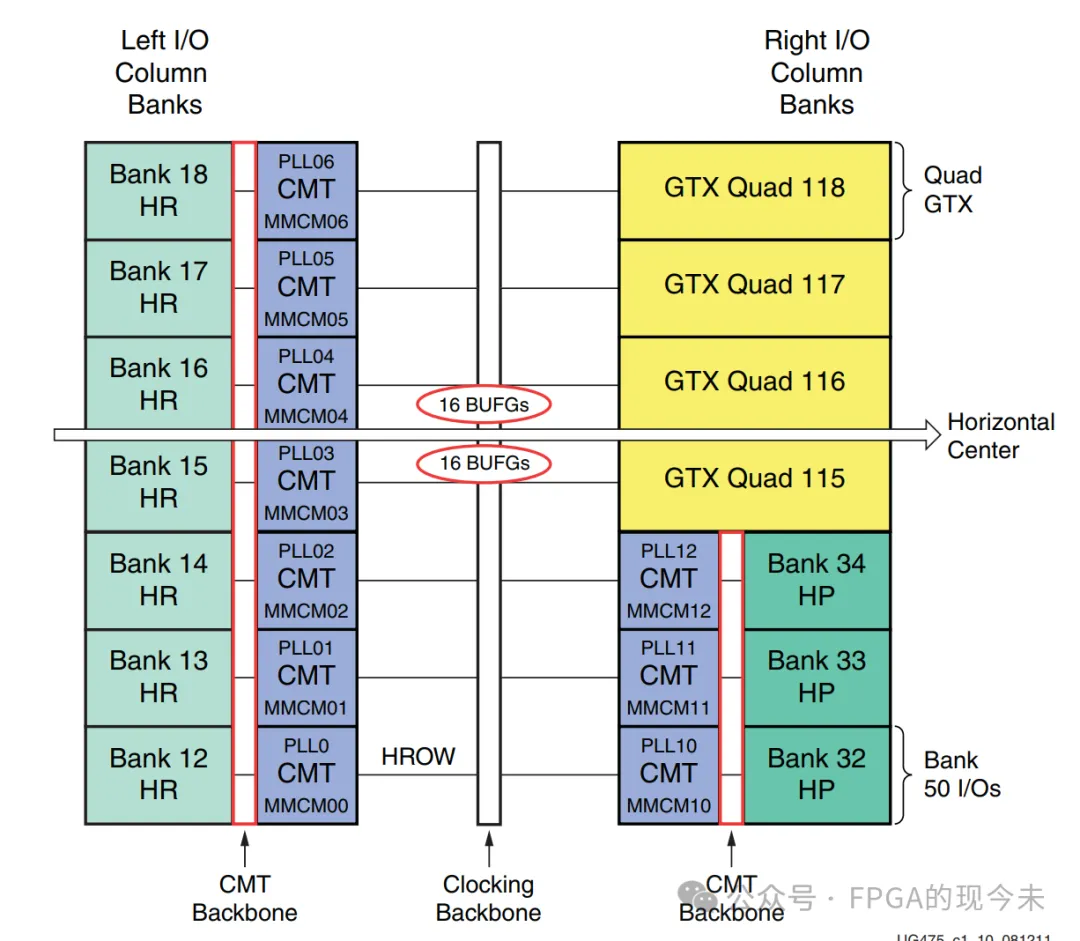

从图上我们可以看到,整个FPGA的上半部分,几乎没有消耗逻辑资源,所有消耗的逻辑资源几乎全部集中在下面了,为什么会这样呢?想到肯定和外部接口有关,通过分析管脚的分配,果然发现了问题。我们知道325T的bank示意图如下图所示:

解决方案

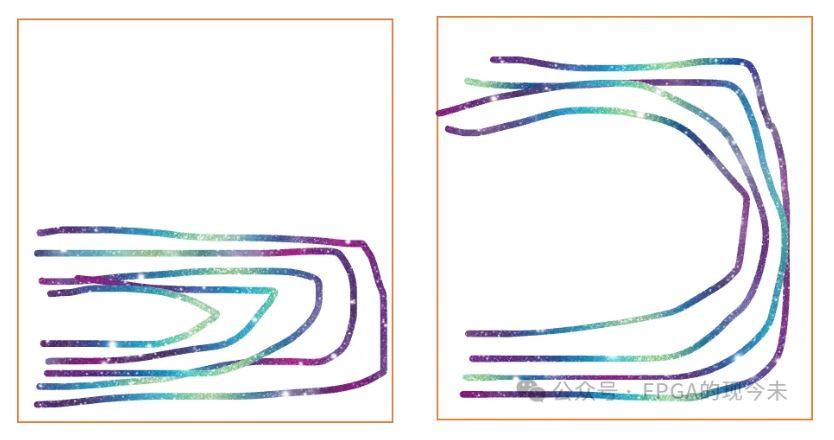

如何解决这种问题,从根本上讲,在项目前期,FPGA开发人员和硬件开发人员要充分沟通,根据FPGA项目中模块的数据流来合理分配管脚。比如在本问题中,DDR接口是固定的在HP bank,对于并行接口,输入部分我们可以考虑在bank12、bank13,输出部分我们可以考虑在bank14和bank15,这样对于数据流来说,vivado最终布局布线的结果,可能大体是如下图左边这样的(该示意图画的比较理想,但是不影响该问题的说明)。当然我们也可以把输入输出接口分开点,贯穿整个芯片,那最终的布局布线结果可能是下图右边这样的。这样使得数据流在FPGA内部是有序的。

当后续模块增加后,我们可以通过合理的布局,比如通过pblock的方式,规划内部数据流的走向。这种方案尤其是对于多die的芯片,更为重要。这部分在基于xilinx的跨die FPGA的逻辑设计中有详细介绍。

当然对于本案例中的问题不可能采用上述的方式来解决,这里还有第二种方案,就是打拍,根据走线过长的路径的分析,在中间适当的插入reg,本案例中,路径过长是由于输入的iddr位置固定,导致iddr输出后的数据,所经历的组合逻辑较多导致。这里将iddr的输出数据打2拍后,解决该问题。

总结

(1)、在FPGA项目前期,要提前规划好FPGA内部的数据流走向,防止数据流互串;

(2)、对于较复杂的项目,可以通过pblock的方式手动布局来规划数据流走向。