来源:FPGA入门到精通

AMD(原Xilinx)等FPGA制造商采用多die技术,将多个逻辑芯片(die)集成到一个封装中,以实现更高的逻辑密度、更快的数据传输速度和更低的功耗。

今天分享下多die FPGA芯片的相关知识和概念。

一、多die FPGA概述

1、什么是多die FPGA?

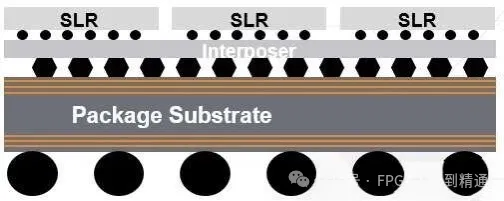

多die FPGA,也称为SSI(Stacked Silicon Interconnect)技术,是一种将多个独立的逻辑芯片通过高密度互连技术堆叠在一个封装内的FPGA设计。

这个die实际就是SLR(Super Logic Region),通过Interposer连接在一起,每个die可以看成一个小FPGA芯片。

这种设计允许FPGA拥有更大的逻辑资源、更高的I/O密度和更优的性能表现 。

2、多die FPGA的优势

(1)更高的逻辑资源

多die FPGA通过集成更多的逻辑单元,提供了比单die FPGA更多的逻辑资源,能够处理更复杂的任务。

(2)增强的I/O能力

由于可以集成更多的I/O单元,多die FPGA能够支持更多的外部接口,满足高速数据传输的需求。

(2)优化的功耗表现

通过更高效的互连技术和电源管理,多die FPGA在提供高性能的同时,也能保持较低的功耗。

二、Xilinx多die FPGA架构解析

1、SLR(Super Logic Region)

Xilinx的多die FPGA由多个SLR组成,每个SLR相当于一个独立的FPGA die,拥有自己的逻辑资源、内存和I/O资源。

SLR之间的连接通过专用的互连技术实现,确保了高效的数据交换 。

2、SLL(Super Long Line)

SLL是连接不同SLR的长线路,它们是多die FPGA中的关键互连资源。

SLL提供了不同SLR之间的高速数据通道,但资源有限,因此在设计时需要合理规划数据流以避免时序问题 。

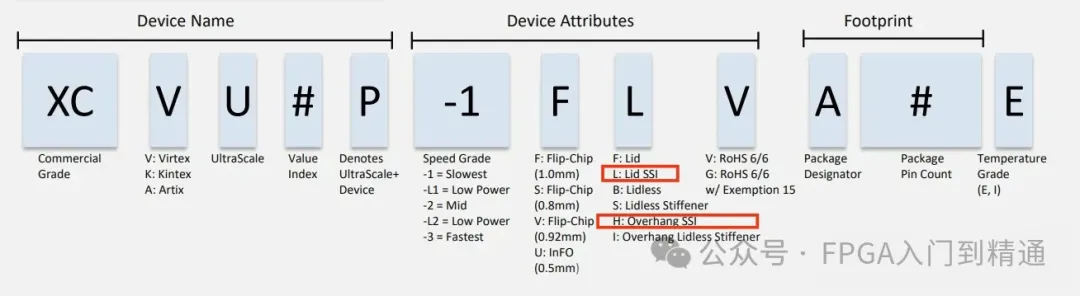

三、如何判断Xilinx芯片是否为多Die

1、芯片型号识别

首先,可以通过芯片的型号来进行初步判断。Xilinx的多Die芯片型号通常会在数据手册中明确标注,如下图红框中。

UltraScale和UltraScale+系列中的大部分芯片都是多Die芯片。

2、 Vivado Tcl Console命令

在Vivado项目中,可以通过Tcl Console执行特定命令来查询芯片是否为多Die。

TCL命令:

get_property SLRS [get_parts <芯片型号>]

此命令可以返回芯片的SLR数量。

如果SLR_COUNT大于1,则表示该芯片是多Die芯片,否则为单die芯片。

四、多Die芯片设计注意事项

1、时序收敛问题

多Die芯片由于SLR之间的连接使用Super Long Line(SLL)资源,这些资源有限,可能导致时序收敛问题。

设计时需要特别注意跨SLR的信号传输。

跨die时钟信号不需要特殊处理,Interposer上有专用的全局时钟走线。

对于其它信号,Xilinx提供了多种方法来处理跨die信号,包括使用LAGUNA寄存器和自动流水打拍的方式。

在实践中,通过在跨die数据流的两侧插入打拍逻辑,可以有效解决时序收敛问题 。

在多die FPGA中,复位信号的处理尤为重要。由于复位信号需要跨多个die传播,不当的设计可能导致时序问题。

一种有效的解决方案是将复位信号先同步到各个die,然后只复位一个die的逻辑,从而简化了复位信号的传播

2、资源分配

在多Die芯片上,合理分配资源至各个SLR是至关重要的。

建议不要使单个SLR的资源使用率过高,以避免资源拥塞,一般不超过80%。

3、Master SLR识别

在多Die芯片中,通常有一个Master SLR,它负责配置FPGA的电路、DNA_PORT和EFUSE_USER等。识别Master SLR对于设计至关重要。

TCL命令:

get_slrs -filter IS_MASTER

五、设计策略与实践

1、模块划分

在设计初期,应该根据SLR的数量和大小来划分模块,确保每个SLR的资源利用率均衡。

2、数据流设计

设计时应考虑数据流在不同SLR之间的流动,避免复杂的数据交换,以减少跨SLR的通信需求。

3、时钟管理

虽然跨SLR的时钟不需要特殊处理,但合理的时钟树设计仍然是必要的,以确保时序的准确性。

4、约束文件编写

在编写约束文件时,需要特别注意跨SLR的信号约束,以避免布线拥塞和时序问题。