来源:FPGA技术实战

1.1 概述

Atmel®AT24C01C/02C提供1024/2048位的串行电可擦除可编程只读存储器(EEPROM),其组织为128/256个字,每个字8位。这两种设备都包含级联功能,最多允许八个设备共享一条通用的2线总线。这些设备被优化用于许多工业和商业应用,其中低功率和低电压操作是必不可少的。

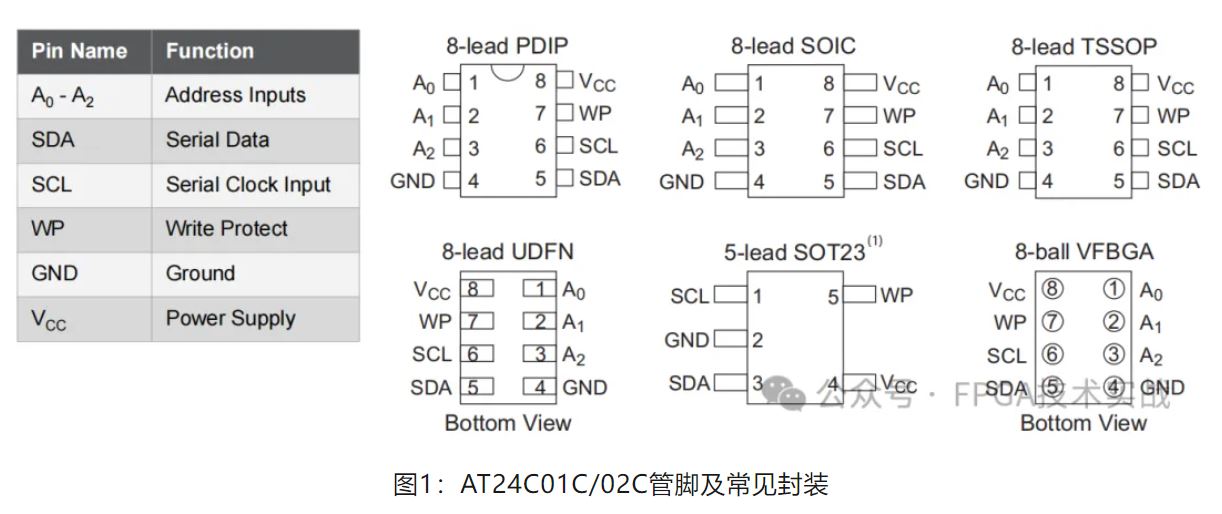

AT24C01C/02C有节省空间的8引脚PDIP、8引脚SOIC、8引脚TSSOP、8引脚UDFN、5引脚SOT23和8球VFBGA封装。此外,整个系列的工作电压为1.7V至5.5V VCC。

串行时钟(SCL):SCL输入用于将上升沿沿时钟数据输入每个EEPROM设备,并将下降沿沿时钟数据输出每个设备。该引脚是开漏极驱动的。

串行数据(SDA):SDA引脚是双向的,用于串行数据传输。该引脚是开漏极驱动的。

设备/页面地址(A2、A1、A0):A2、A1和A0引脚是AT24C01C/02C的硬接线设备地址输入。在单个总线系统上可以寻址多达八个1-Kbit或2-Kbit设备。

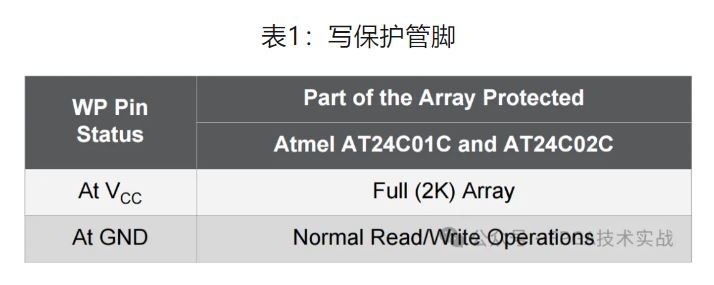

写保护(WP):AT24C01C/02C有一个写保护引脚,可提供硬件数据保护。当连接到地(GND)时,写保护引脚允许正常的读/写操作。当写入保护引脚连接到VCC时,写入保护功能被启用,并如表1所示进行操作。

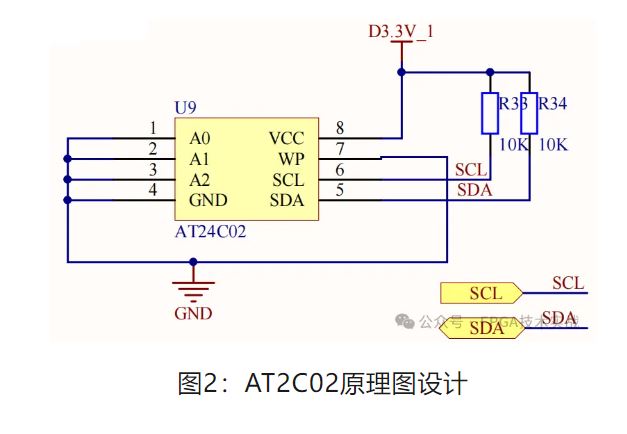

1.3 原理图设计

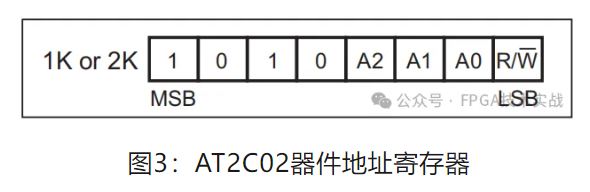

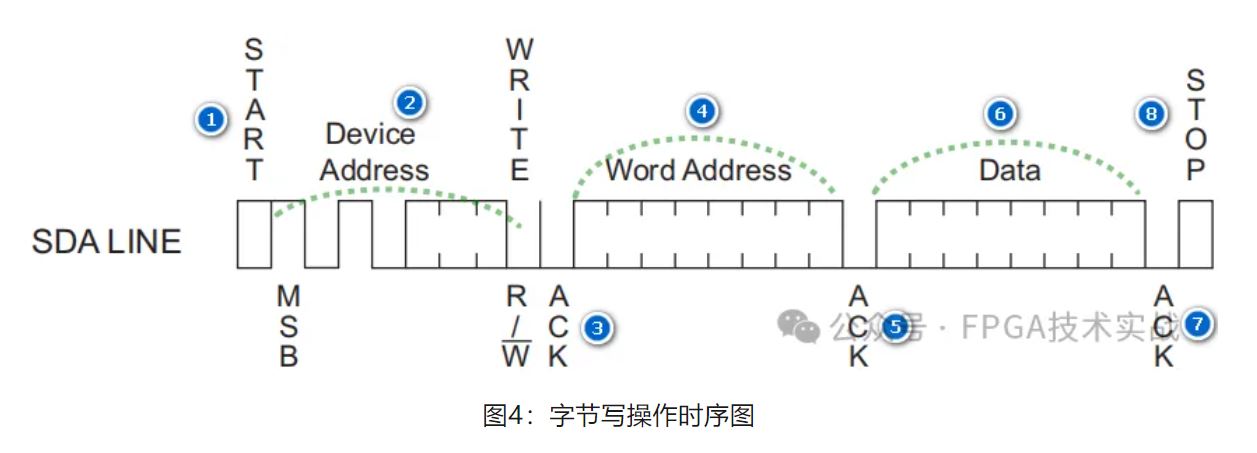

设备地址字由前四个最高有效位的强制性“1010”(0xA)序列组成,如图4所示,这对所有串行EEPROM设备都是通用的。

接下来的三个位是1K和2K EEPROM的A2、A1和A0设备地址位。这三个位必须与其相应的硬接线输入引脚A2、A1、和A0进行比较,以便部件进行确认。设备地址的第八位是读/写操作选择位。如果该位为高,则启动读操作,如果该位低,则启动写操作。

(1)单字节写操作

⑤从机接收到写地址后,回传应答信号(ACK)给主机;

⑥主机收到从机回传的应答信号(ACK)后,发送写Data给从机;

⑦从机接收到写数据后,回传应答信号(ACK)给主机;

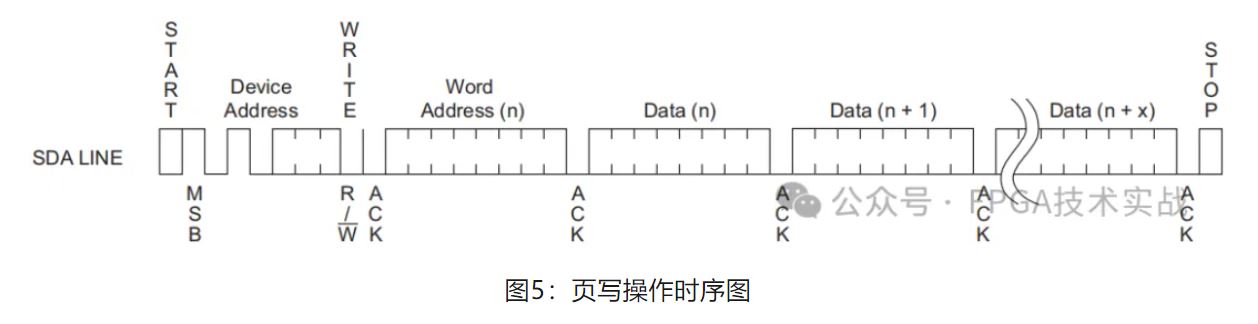

Atmel AT24C02,2K串行EEPROM:内部组织32页,每页8字节,2K需要一个8位数据字地址用于随机字寻址。

页面写入与字节写入相同,但主机在第一个数据字被计时后不会发送停止条件。相反,在EEPROM确认接收到第一个数据后,主机最多可以发送七个字节。在接收到每个数据字之后,EEPROM将以ACK作为响应。主机必须在“停止”条件下终止页面写入序列。

在接收到每个数据字之后,数据字地址的低三位在内部递增。较高的数据字地址位不递增,保留存储器页行位置。当内部生成的字地址到达页面边界时,下面的字节被放置在同一页面的开头。如果超过八个数据字被传输到EEPROM,数据字地址将“翻转”,并且先前的数据将被覆盖。

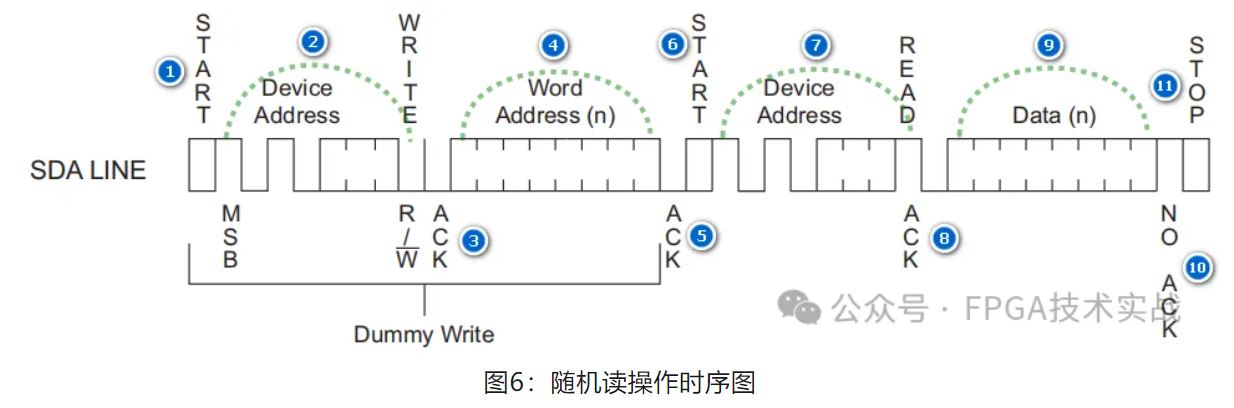

⑤从机接收到读地址后,回传应答信号(ACK)给主机;

⑥主机再次产生起始信号(START)给从机;

⑦主机将控制命令(含器件地址DEveice address、READ)给从机;

⑧从机接收到读命令后,回传应答信号(ACK)给主机;

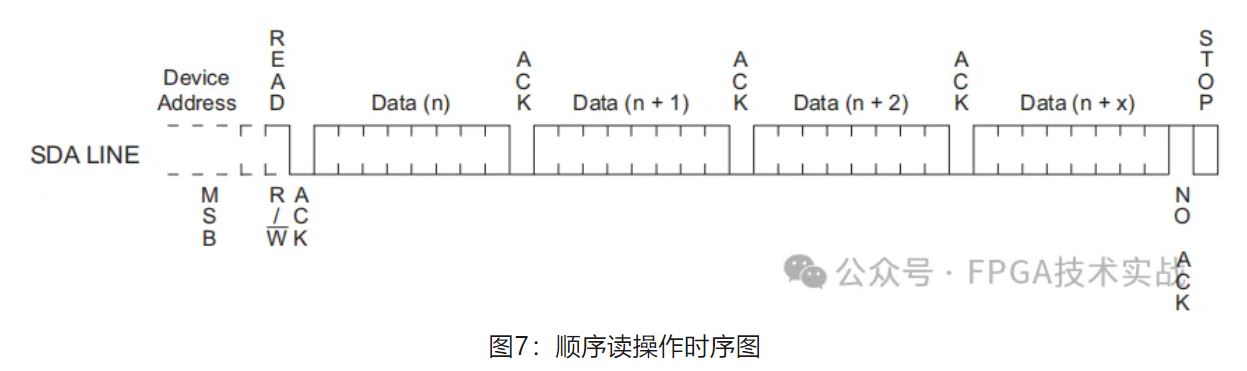

(2)顺序读操作

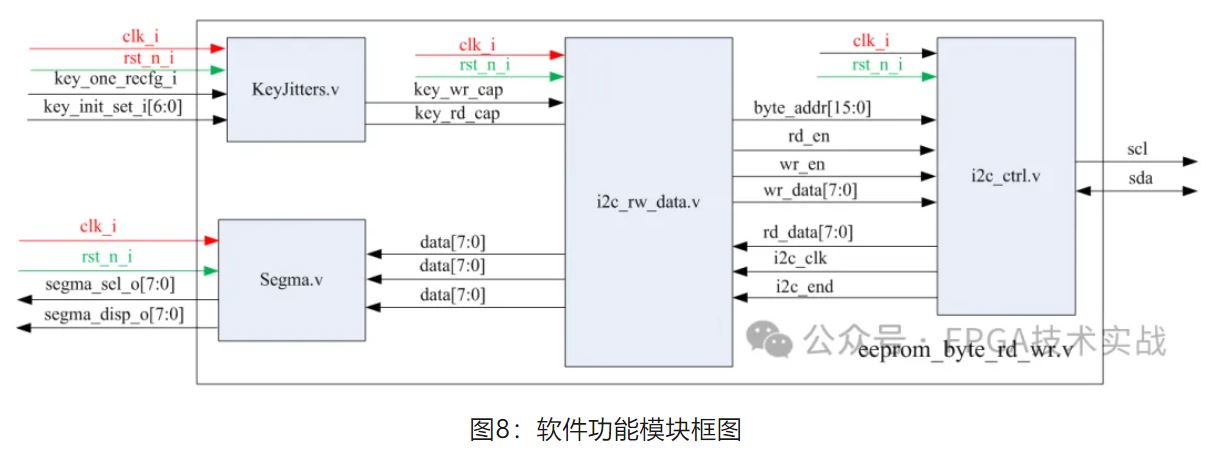

(1)软件实现

本文要利用FPGA通过I2C接口实现AT24C02 EEPROM读写操作。具体功能如下:

(1)I2C总线接口读写功能;

(2)将读出的数据显示在数码管上;

各个模块功能:

(5)KeyJitters.v实现按键操作消抖功能。