作者:张海军,来源:傅里叶的猫

前言:本文章为FPGA问答系列,我们会定期整理FPGA交流群(包括其他FPGA博主的群)里面有价值的问题,并汇总成文章,一方面是希望能帮到不经常看群消息的小伙伴,另一方面也算是我们的技术积累。

Q:在Vivado的Post-Synthesis Timing Simulation中,为何前100ns的数据不变化?从下面的图可以看到,时钟一直有,复位也变成了高,代码非常简单,这里就不show出来了,就是一个简单的计数器。为什么刚解复位的那几个周期,数据一直没用变化?如果换成是功能仿真,就没有这个问题。

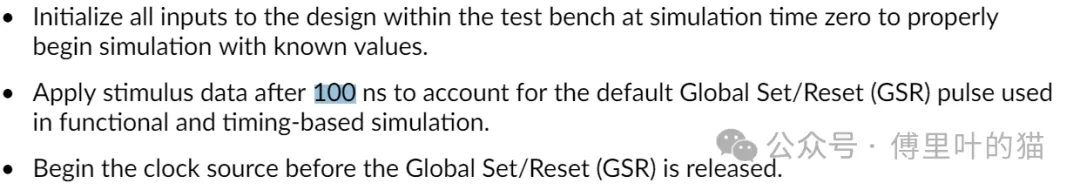

A:这跟GSR有关系,在timing-based simulation中,仿真器会等待这个100ns的GSR释放后才会使激励生效。而功能仿真由于跟timing和器件特性无关,因此不会有这个问题。