作者:FPGA入门到精通

在FPGA设计的世界中,同步与异步设计是确保时序准确性的基石。本文将详细介绍下FPGA设计中的同步适中就好与异步时钟,帮助读者在实际项目中应用这些概念。

一、同步时钟

同步设计要求所有的时钟信号都是同源的,或者它们的频率和相位满足一定的整数倍关系。

这保证了在任何给定的时刻,设计中的所有触发器都能稳定地采样数据。

1、同源同频同相位

在最简单的同步设计中,所有时钟信号都是完全同步的,没有时序问题。

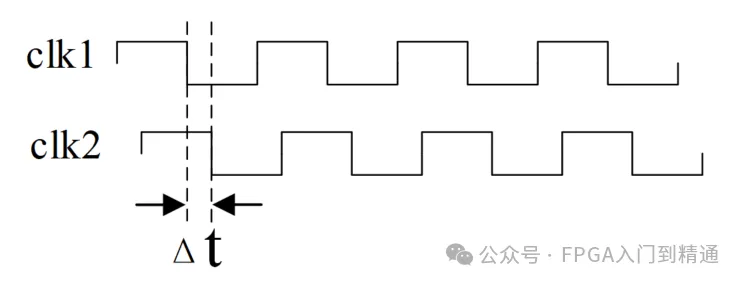

2、同源同频不同相位

即使存在相位差异,只要这个差异是固定的,系统仍然可以认为是同步的。

3、同源不同频但存在整数倍分频比

一个时钟可能是另一个时钟的整数倍,这种情况下,通过确保数据在时钟边沿正确采样,可以实现同步操作。

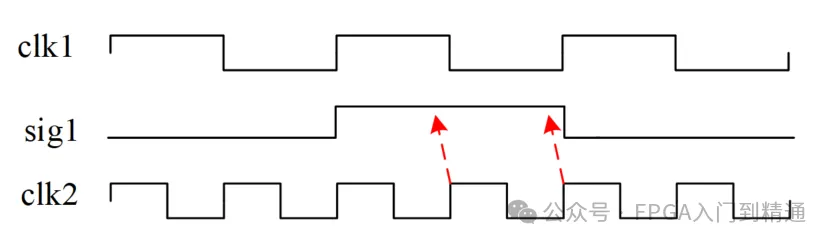

二、异步时钟

异步设计中,时钟信号可能来自不同的源,或者它们的频率比不是整数倍,跨时钟域传输信号处理不好的话,容易出现建立时间和保持时间的违规。

1、不同源时钟

最常见的异步情况,时钟信号的相位和频率都不匹配。

2、同源但频率比不是整数倍

即使来自同一源,如果频率比不是整数倍,也会导致时序问题。

三、设计实践建议

在设计中优先考虑同步逻辑,因为它更容易进行时序分析和优化。

当必须处理异步信号(跨时钟域传输)时,使用两级触发器或异步FIFO来确保数据的一致性和稳定性。

对于跨时钟域的设计,确保充分理解潜在的时序风险,并采取适当的同步化措施。

文章来源:FPGA入门到精通