作者:FPGA入门到精通

Block Design(图形化设计模块)是Vivado中一个非常关键的组件,它允许设计者以图形化的方式快速搭建和验证复杂的数字电路设计。

本文将详细介绍Vivado Block Design的使用流程,旨在帮助读者从基础到高级技巧,全面掌握这一工具。

一、概述

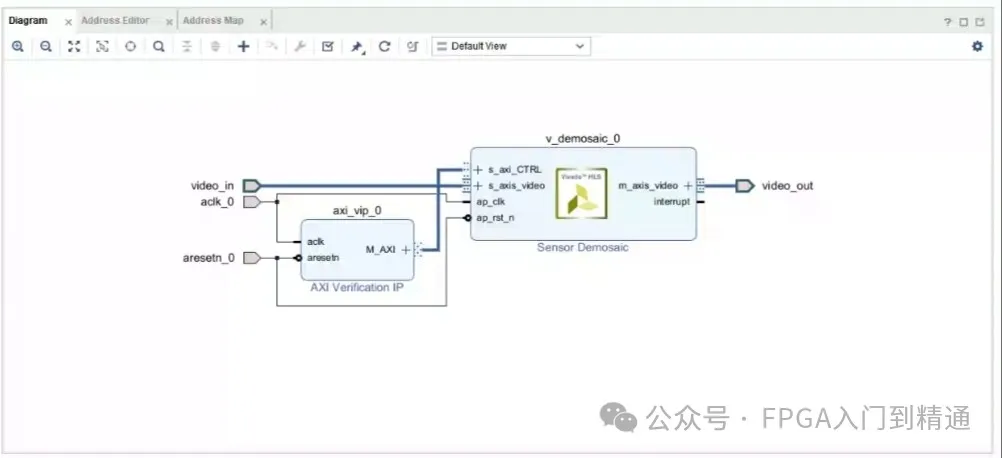

Vivado Block Design提供了一种直观的设计方法,通过将IP模块和逻辑模块以图形化的方式连接起来,可以快速构建电路结构。

Block Design本质上是一个容器,用于放置IP并通过连线相互关联 。

这种设计方式不仅提高了设计效率,也使得设计过程更加直观易懂 。

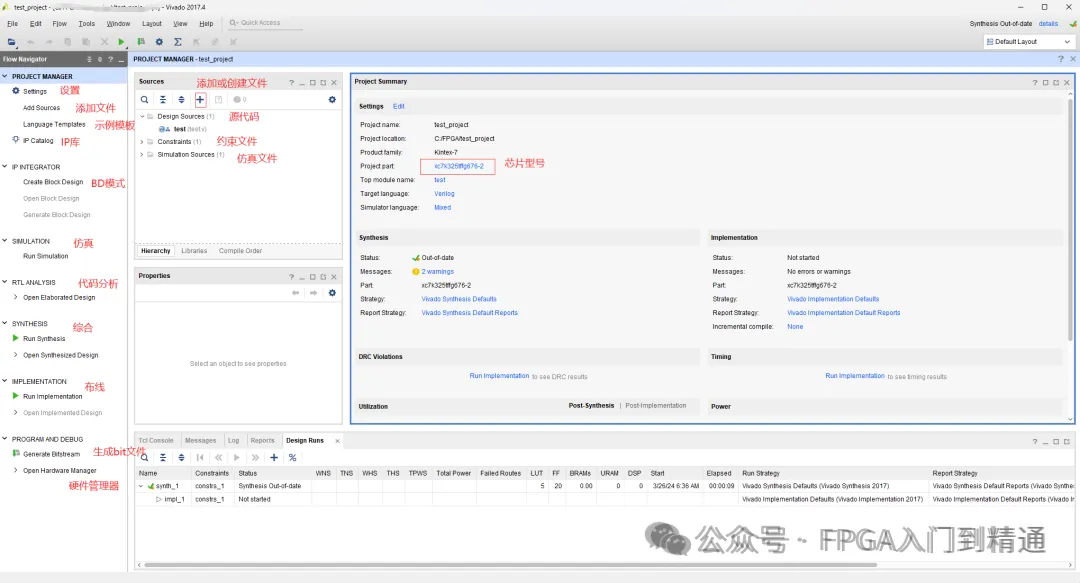

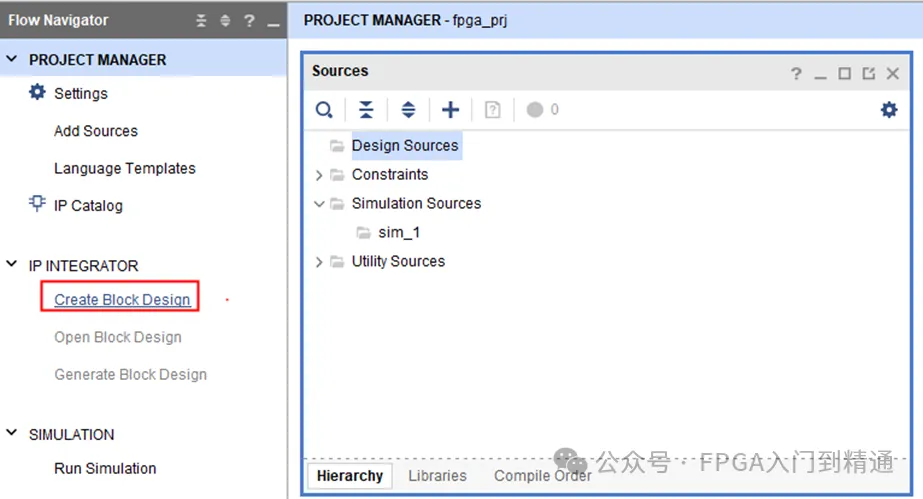

二、新建Block Design

首先,在Vivado中选择FPGA芯片型号,新建FPGA工程。

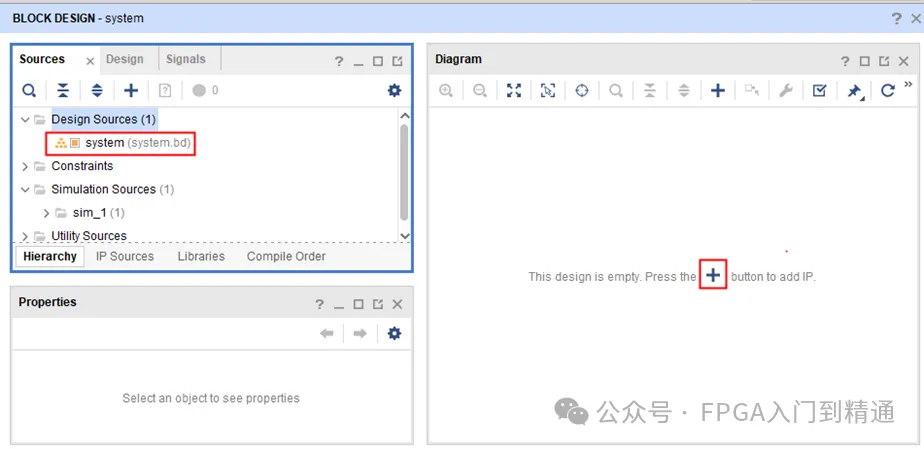

点击左侧导航栏【PROJECT MANGER】中的“Create Block Design”,创建一个BlockDesign。

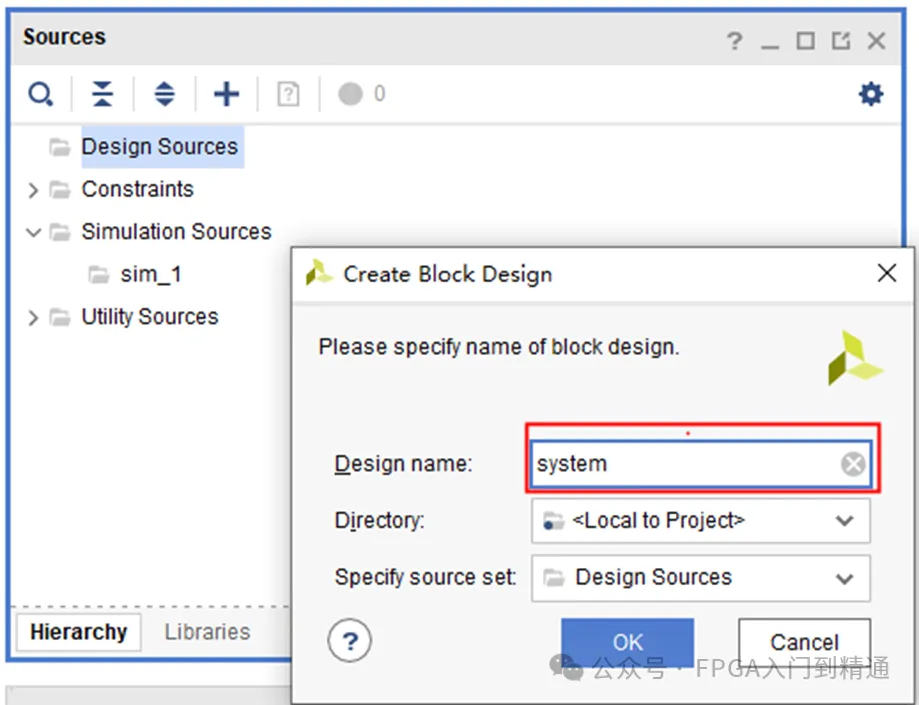

弹出Block Design新建界面,可以命名为system 或其他自定义名称。

创建成功后,自动打开BlockDesign界面。

三、添加和配置IP

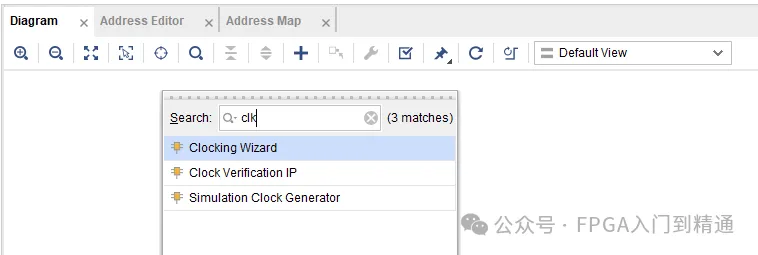

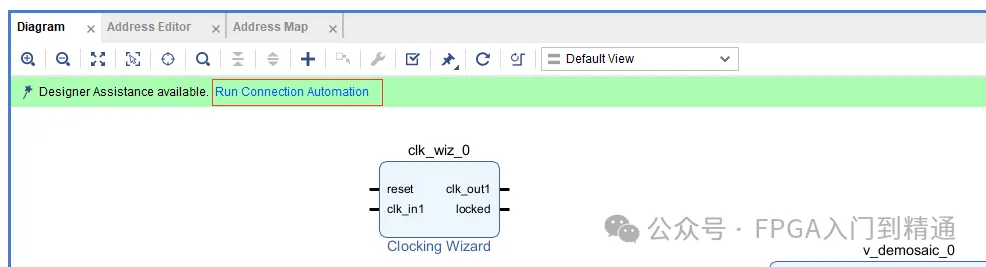

在Block Design中,可以通过点击"+"号添加所需的IP模块。

例如,添加clk_wiz_0进行时钟设置,或添加HDMI输出IP并设置相应的时钟和参数。

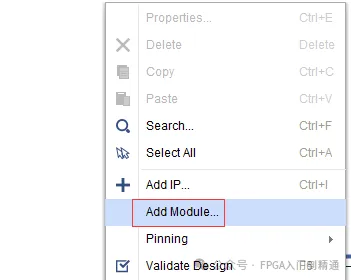

对于RTL文件或Block Design,可以通过"Add Module..."选项将其添加到设计中 。

四、连接模块

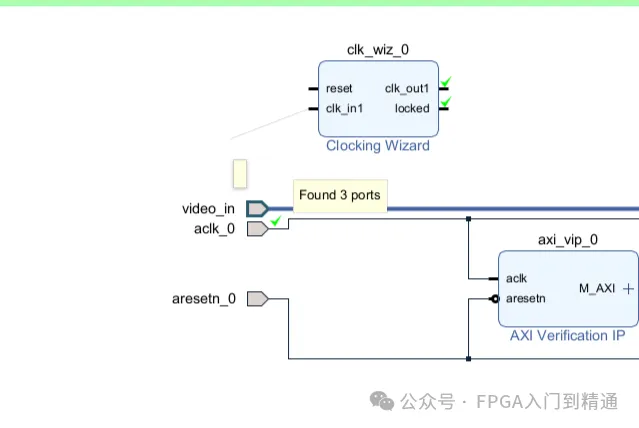

使用鼠标拖动连接线,将IP模块的接口相互连接,形成数据和控制流。

Vivado提供了自动连接的功能,但有时候可能连接会出错,也可以手动调整连接以满足设计需求 。

五、配置和优化

对每个IP模块进行配置,包括设置参数、选择选项和定义接口。

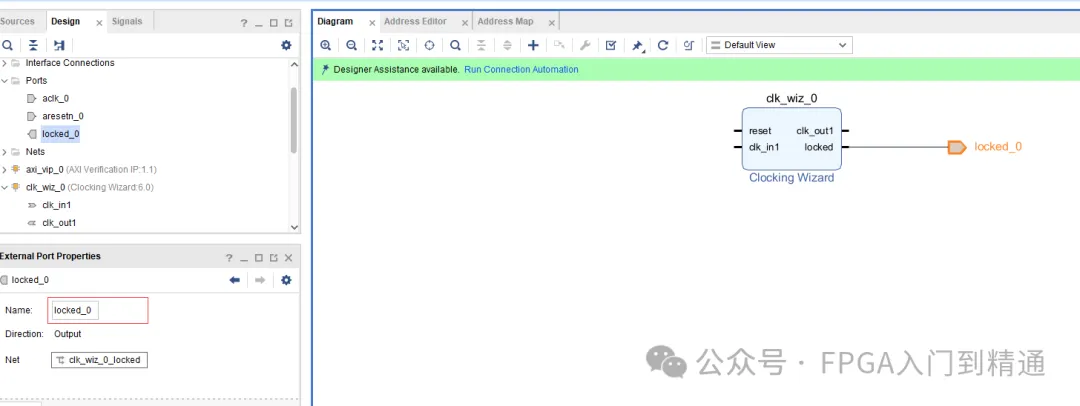

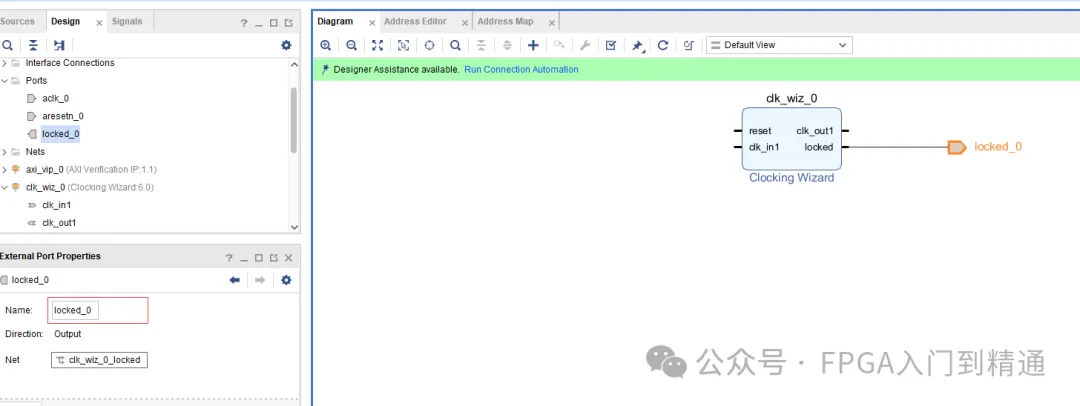

此外,可以对信号命名进行修改以符合设计习惯,并通过"make External"将IO端口引出到外部 。

单击已经引出的信号,还可以修改名字。

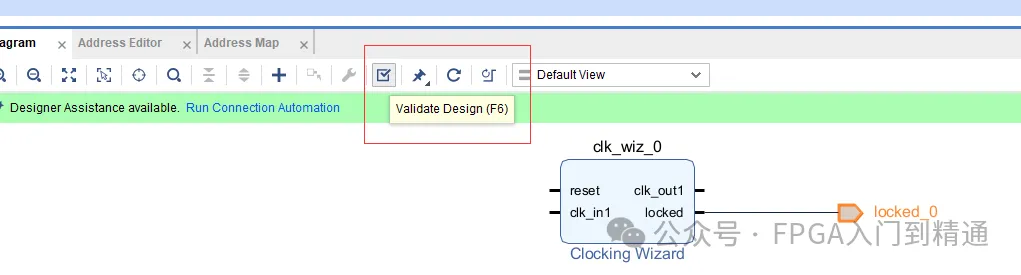

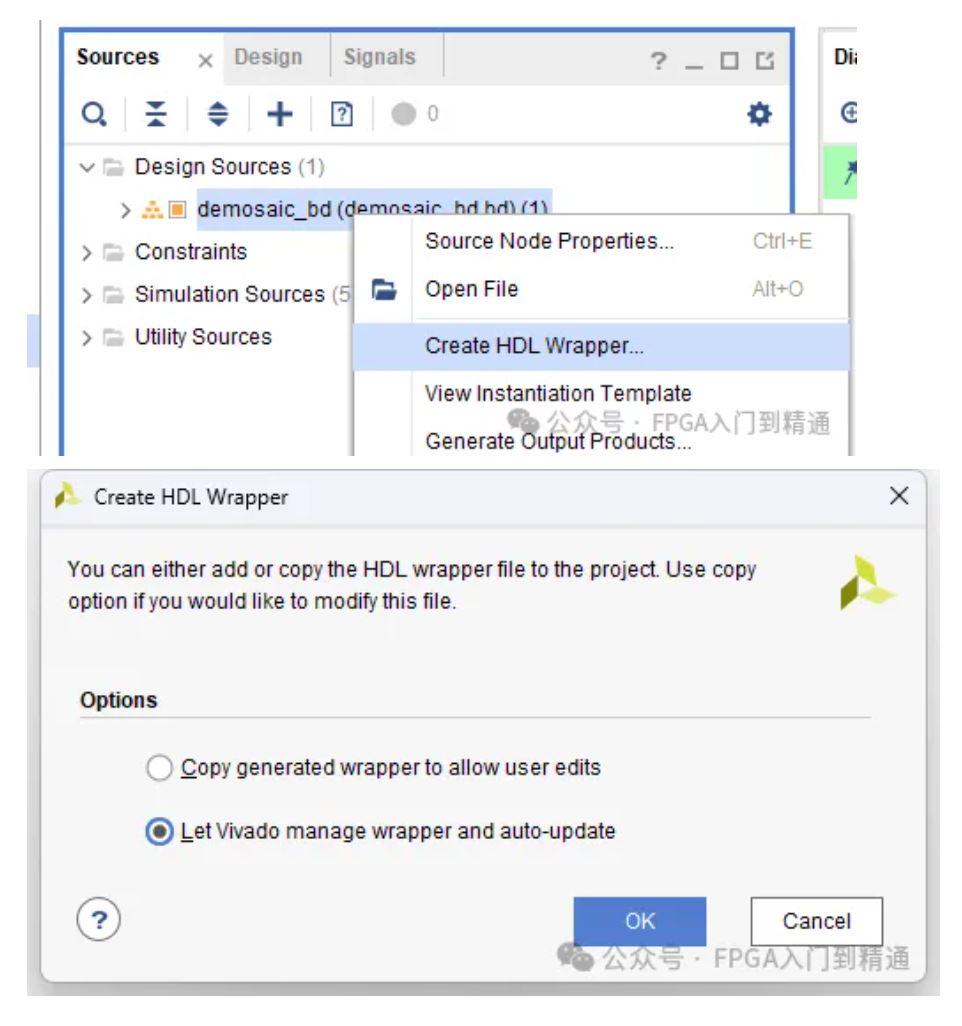

完成Block Design后,通过"Create HDL Wrapper"生成FPGA的顶层文件,这将封装Block Design并生成相应的HDL代码 。

八、编译下载

生成设计文件后,进行综合和实现,将设计映射到目标设备的资源,并进行布局和布线 。

在综合和实现完成后,进行时序分析以验证设计的时序性能是否满足要求,确保设计可以在规定的时钟频率下稳定工作 。

使用Vivado的仿真工具对设计进行验证,确保其功能和性能与预期一致 。

对于FPGA设计,生成比特流文件并下载到目标FPGA设备上进行验证和测试,以确保设计在实际硬件上能够正常工作 。