文章来源:FPGA开源工作室

1. 概述

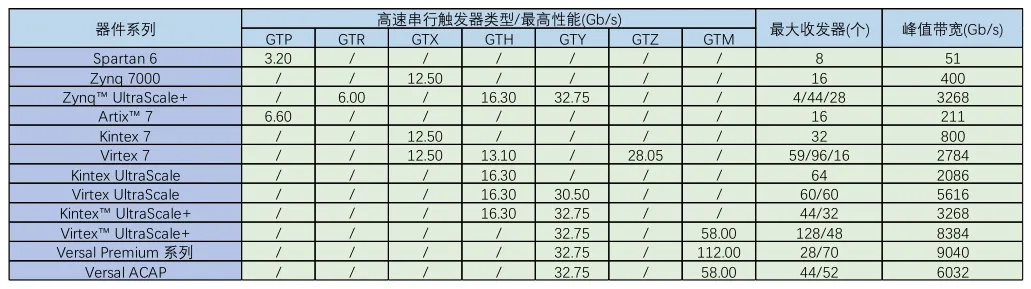

Xilinx 7系列FPGA全系所支持的GT,GT资源是Xilinx系列FPGA的重要卖点,也是做高速接口的基础,GT的意思是Gigabyte Transceiver,G比特收发器。不管是PCIE、SATA、MAC等,都需要用到GT资源来做数据高速串化和解串处理,Xilinx不同的FPGA系列拥有不同的GT资源类型,低端的A7由GTP,K7有GTX,V7有GTH,GTZ被用于少数V7系列,更高端的U+系列还有GTY等,他们的速度越来越高,应用场景也越来越高端。。。

7系列FPGA GTX和GTH收发器是功率高效的收发器,GTX收发器支持500 Mb/s至12.5 Gb/s的线路速率,GTH收发器支持13.1 Gb/s的线路速度。GTX/GTH收发器具有高度可配置性,并与FPGA的可编程逻辑资源紧密集成。

高速收发器性能对比

2. GTX/GTH收发器支持以下使用模式

关于GTX介绍最详细的肯定是Xilinx官方的《ug476_7Series_Transceivers》 以此来解读GTX:

GTX/GTH收发器支持以下使用模式:

• PCI Express, Revision 1.1/2.0/3.0

• 10GBASE-R

• Interlaken

• 10 Gb Attachment Unit Interface (XAUI), Reduced Pin eXtended Attachment Unit

Interface (RXAUI), 100 Gb Attachment Unit Interface (CAUI), 40 Gb Attachment Unit

Interface (XLAUI)

• Common Packet Radio Interface (CPRI™)/Open Base Station Architecture Initiative

(OBSAI)

• OC-48/192

• OTU-1, OTU-2, OTU-3, OTU-4

• Serial RapidIO (SRIO)

• Serial Advanced Technology Attachment (SATA)/Serial Attached SCSI (SAS)

• Serial Digital Interface (SDI)

• SFF-8431 (SFP+)

3. GTX内部基本结构

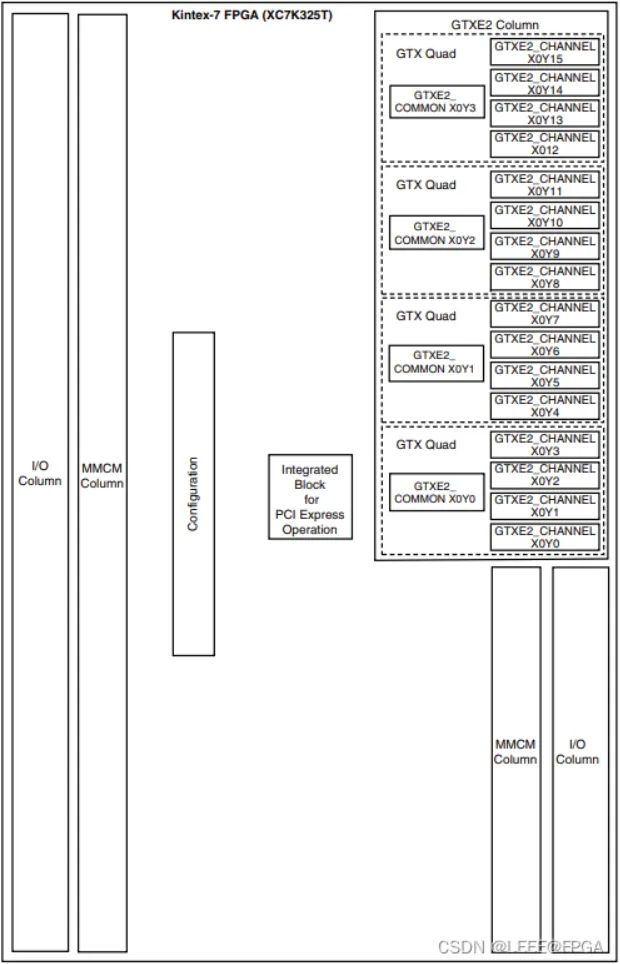

如下图所示,Xilinx以Quad来对串行高速收发器进行分组,四个串行高速收发器(GTXE2_CHANNEL)和一个 GTXE2_COMMOM组成一个 Quad,每一个串行高速收发器称为一个 Channel(通道)。

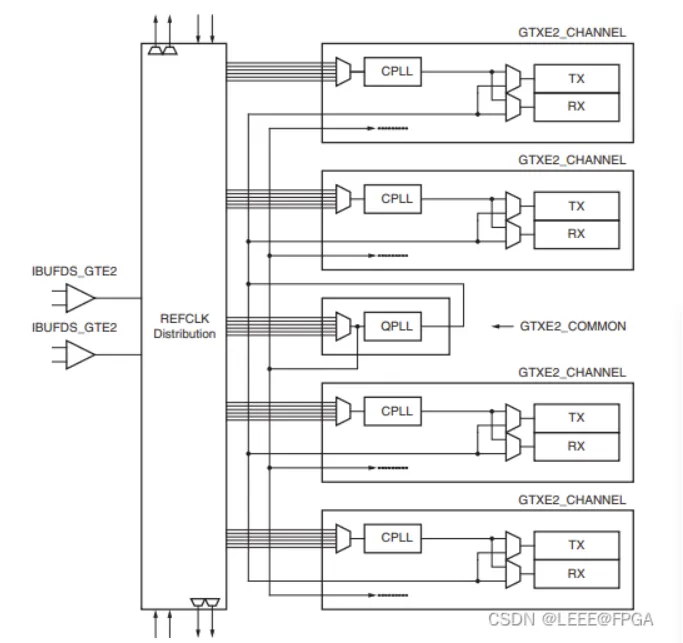

一个QUAD的内部结构如下图所示,由四个GTXE2_CHANNEL 原语和一个GTXE2_COMMON原语组成。

GTXE2_COMMON原语包含一个LC-tank PLL(QPLL)。

每一个GTXE2_CHANNEL 原语包含一个TX,一个RX和一个CPLL。

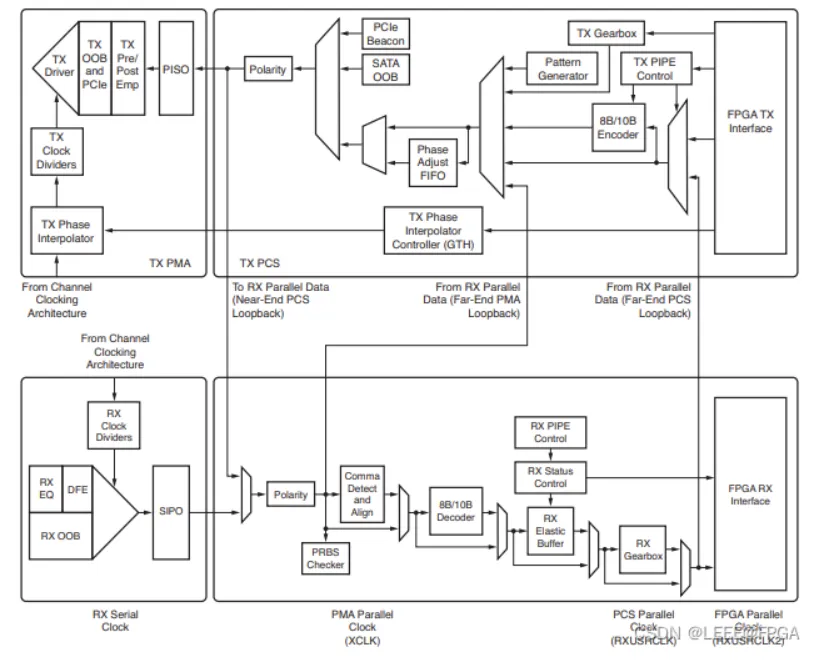

下图为GTXE2_CHANNEL原语内部结构。

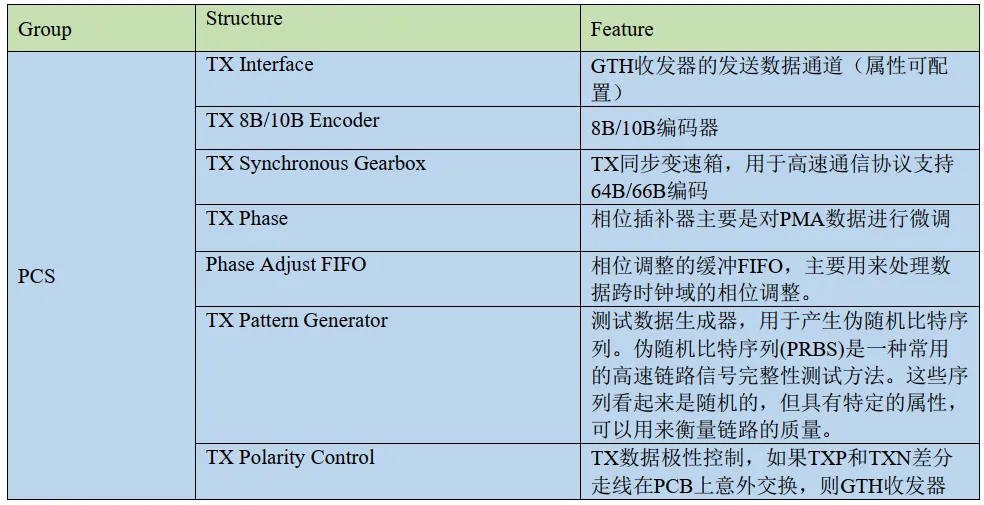

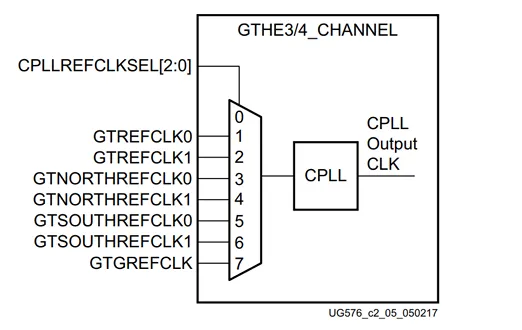

GTXE2_CHANNEL 的发送端和接收端功能是独立的,均由 PMA(Physical Media Attachment,物理媒介适配层)和 PCS(Physical Coding Sublayer,物理编码子层)两个子层组成。其中 PMA 子层包含高速串并转换(Serdes)、预/后加重、接收均衡、时钟发生器及时钟恢复等电路。PCS 子层包含8B/10B 编解码、缓冲区、通道绑定和时钟修正等电路。

从上图中可以看到单个 Channel 由发送接口和接收接口组成,每个接口又分为两部分结构,这两部分结构分别是 PMA 和 PCS。PMA 和 PCS 内部又由许多功能模块构成。

3.1 8b10b编解码

通常说8b10b是一个编码方式。在这里还指GTX PCS中的一个模块。

作为编码,8b10b有平衡电平,防止连续1/0的功能。编码分为正负码和特殊K码。最常用的K码应该是k28.5。8b10b最大的优势在于自带错误检测。当出现8b10b错误的时候,大概率是链路质量有问题。8b10b最大的劣势是效率比较低,有20%的额外开销,所以常用于低于8G的场景,最常见的、使用8b10b、同时又高于8G线速率的似乎是CPRI Rate7,线速率9.8G左右。除了8b10b之外,还有其他很多编码方式,比如64b66b。

3.2 PRBS

PRBS是伪随机序列码,GTX自带了PRBS的生成器(在TX内部)和PRBS接收/检查模块(在RX内部)。ibert中的误码率检查就是基于内置的PRBS模块。

从结构图可以看到,PRBS和8b10b没有项目连接的直接关系,所以ibert的测试中没有使用8b10b编码(也没有使用其他编码)。同时内部的PRBS也不支持使用其他编码。所以如果想在GTX外部使用PRBS信号源,可以另外单独做PRBS的生成器和校验模块。Xilinx似乎是有相关参考设计的。

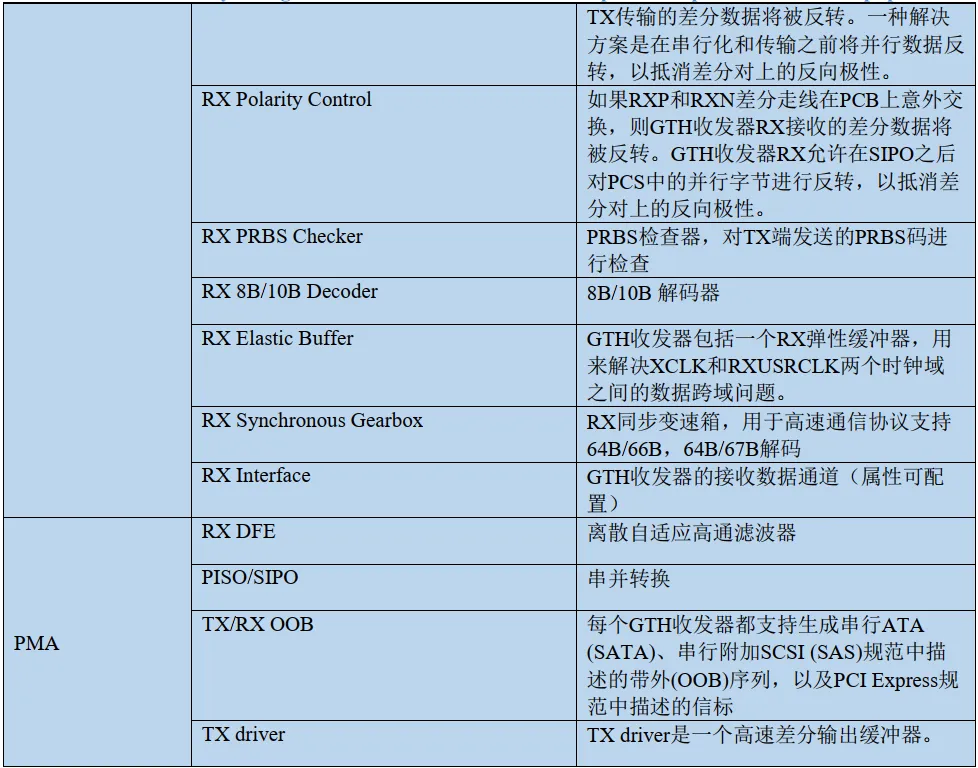

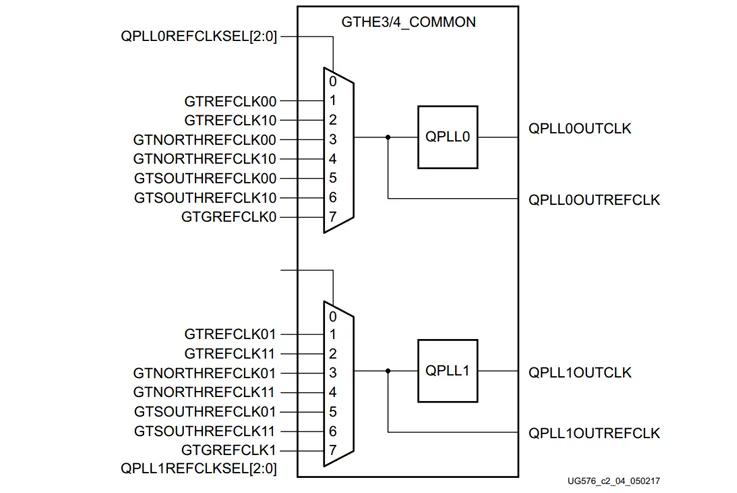

3.3 QPLL和CPLL

已经知道四个GTX为一组,称呼为Quad,每个GTX称呼为Channel,就很容易理解QPLL和CPLL了。QPLL是一个Quad共用的PLL,GTX一个Quad只有一个QPLL。CPLL是每个Channel独有的PLL。

QPLL时钟源结构图

CPLL源时钟结构图

从底层角度看,由于CPLL是每个Channel独有的,所以CPLL的所有接口都在Channel这个底层模块中。而QPLL是另外使用了一个叫common的底层模块。

GTX中QPLL和CPLL,除了数目(一个Quad一个QPLL四个CPLL)和归属(QPLL属于common,CPLL属于Channel)不同之外,最大的不同在于支持的最高线速率频率不同。CPLL最高只有6.xG,而QPLL可以超过10G(具体数值要根据器件的速度等级来查询DataSheet)。

即使QPLL工作在很高的线速率下,Channel也可以工作在较低的线速率下。具体的实现方案就是

使用Channel自带的CPLL而不用QPLL;

2.Channel可以将QPLL的速率按2的倍数进行降低;这样同一个参考时钟下,一个Quad的不同GTX有机会跑在不同的线速率下。当然这一需求需要更多的操作,IP本身无法实现。