文章来源:FPGA入门到精通

FIR滤波器是数字信号处理中常用的滤波器,除了通过Verilog代码自己实现外,Vivado提供了一个FIR滤波器 IP,可以直接调用。

一、什么是 Vivado FIR IP 核

FIR(Finite Impulse Response)滤波器即有限长单位冲激响应滤波器,是数字信号处理中非常重要的一种滤波器类型。

它具有线性相位、稳定性高等优点,在通信、音频处理、图像处理等众多领域都有着广泛的应用。

Vivado 是 Xilinx 公司推出的一款功能强大的 FPGA 开发工具,其中的 FIR IP 核是一个预先设计好的、可配置的模块,用于在 FPGA 上实现 FIR 滤波器功能。

通过使用这个 IP 核,我们可以避免从头开始编写复杂的 FIR 滤波器代码,大大提高开发效率,同时也能保证滤波器的性能和可靠性。

二、FIR IP核的调用与配置

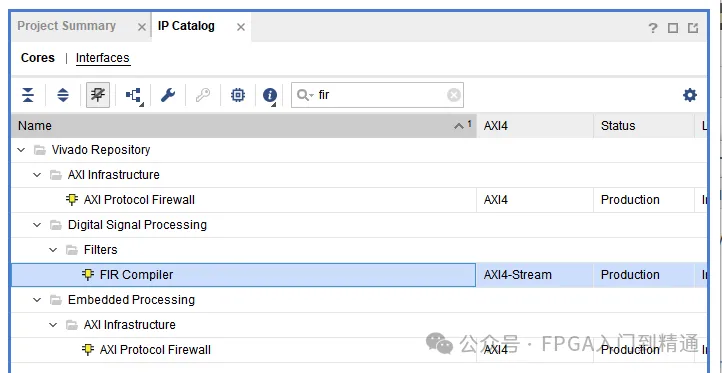

Vivado创建工程后,在IP Catalog中打开FIR Compiler配置界面。

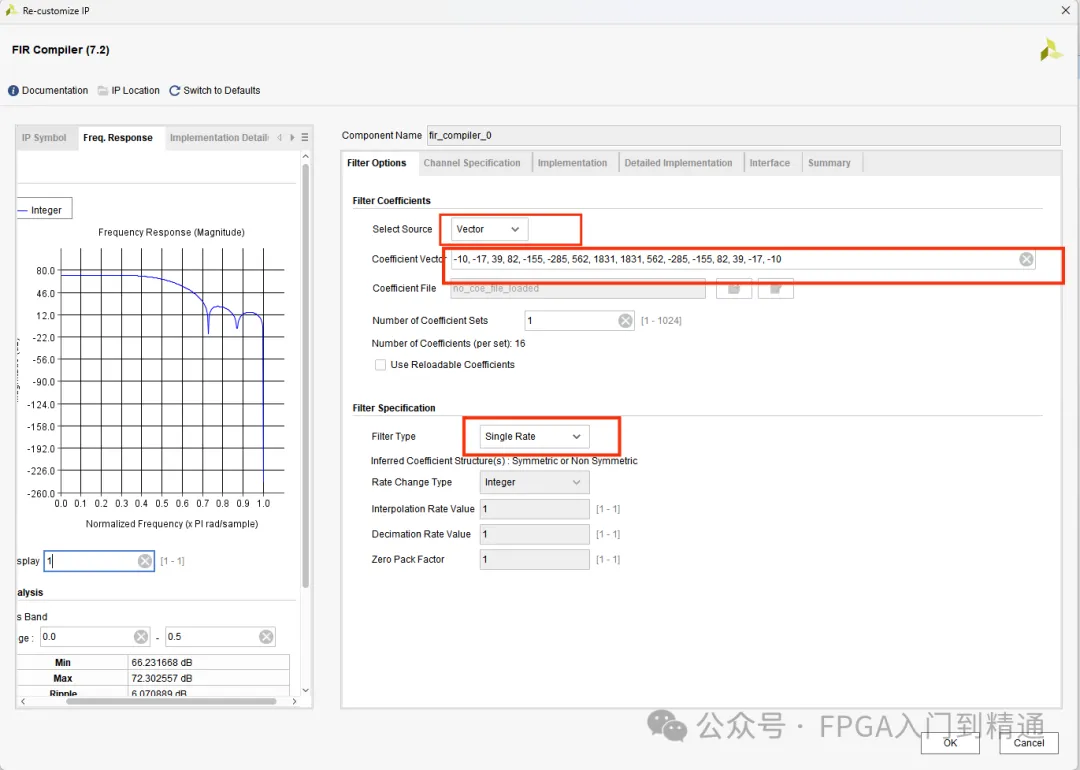

1、Filter Options页面

这是滤波器选项配置,配置滤波器参数,左侧的“Freq Response”可查看对应的频率响应图。

(1)Filter Coefficients

Vivado FIR IP核没有设计滤波器和生成滤波器系数的功能,所以需要使用matlab等工具设计滤波器,并计算出滤波系数导入到IP中。

Select Source:滤波器系数来源设置,可选“COE Vector”或“COE File”。

选择“COE Vector”时,直接在“Coefficients Vector”中,输入滤波器系数向量。

选择“COE File”时,在“Coefficients File”中点击【文件夹】按钮,找到需要的coe文件,也可以点击【修改文件】按钮。

Number of Coefficients set:滤波通道数设置

Number of Coefficients(per set):自动识别出每一个通道滤波器系数的个数。

Use Reloadable Coefficients:使用可重载系数

(2)Filter Specifcation

Filter Type:滤波器结构设置,可选:

“Single Rate”(单速率,即数据输出与输入速率相同)。

其它多速率模式,Decimation(抽取)和 Interpolation(插值)、Hilbert(希尔伯特变换)模式等应用于多速率信号处理系统。

其它选项:不可设置

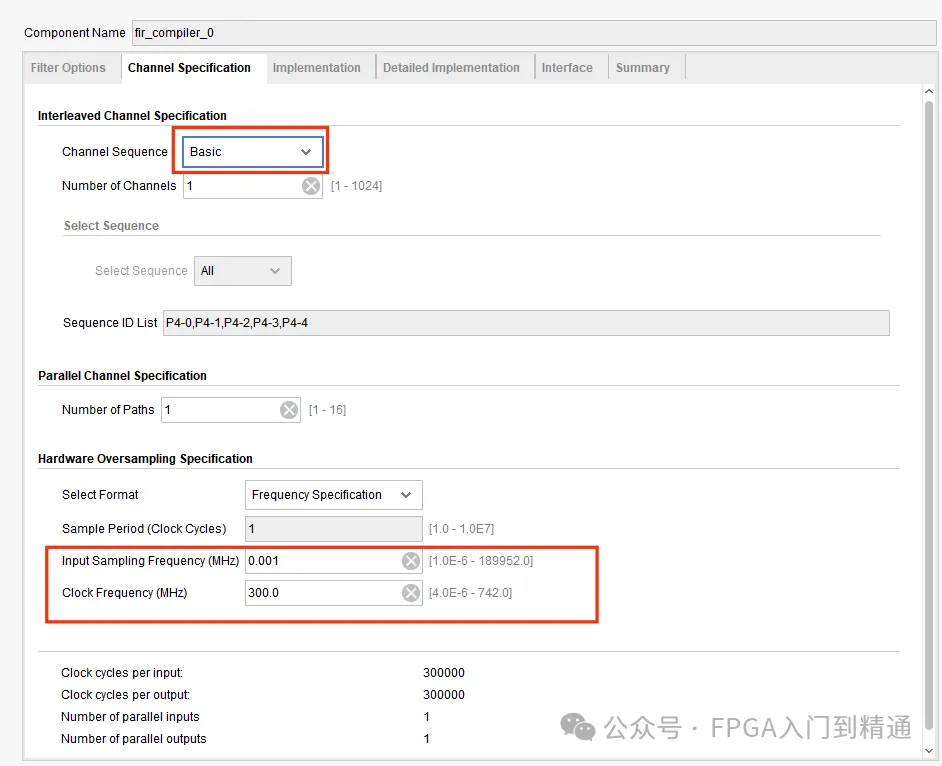

2、Channel specification页面

这是配置通道参数页面,设置滤波器运行时钟频率和采样频率。

Channel Sequence:通道顺序选择,可选basic。

Number of Channels:数据通道数量。

Number of Paths:

Select Format:选择格式,选择用于指定硬件过采样率、内核可用于处理输入样本并生成输出的时钟周期数的格式。

Sample Period:输入或输出样本之间的时钟周期数。

Input Sampling Frequence:输入数据采样时钟速率,也就是采样频率。

Clock Frequence:滤波器运行时钟频率

注意:

如果需要处理多路数据合并后的串行数据时,可设置多个通道,每个通道间都以tlast信号隔开,表示一个通道信号数据结束。

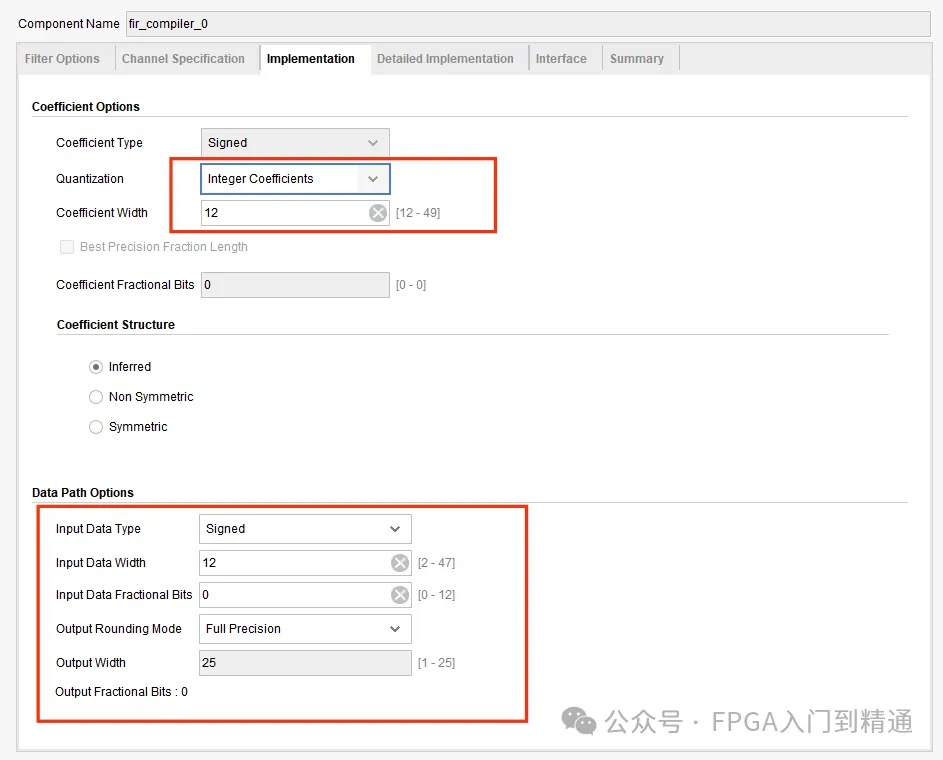

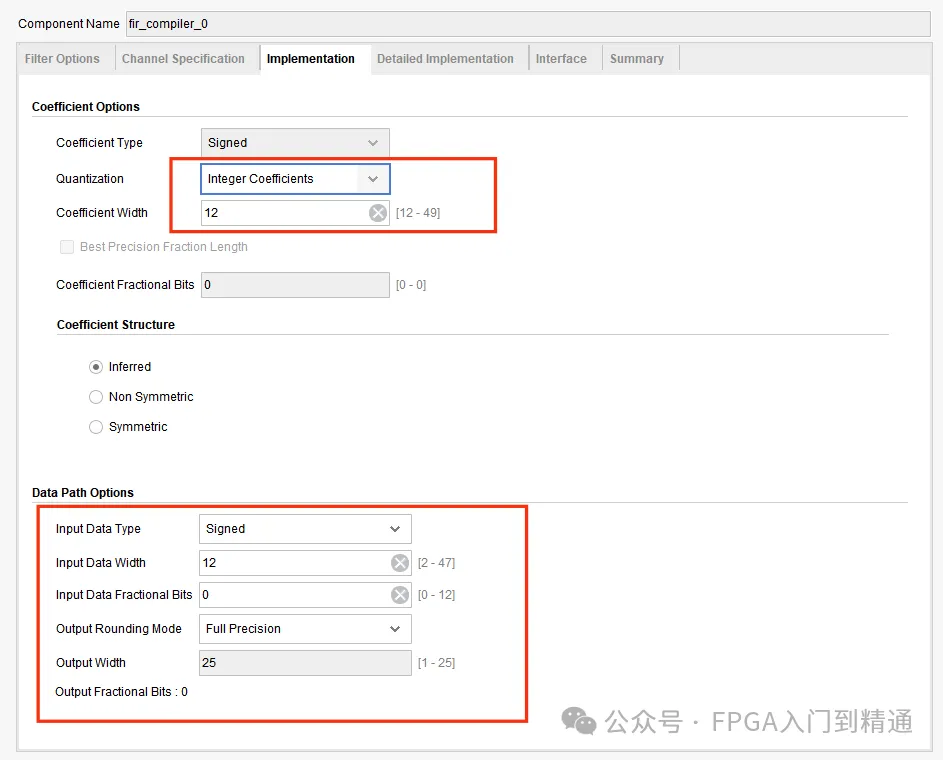

3、Implementation页面

根据滤波器设计,例如设置FIR滤波器系数为12bit有符号整数,输入数据设置为12bit有符号整数,其他保持默认设置。

(1)Coeffcient Options

Coeffcient Type:系数类型,有符号数、无符号数

Quantization:量化方式,

Coeffcient Width:系数位宽

Coeffcient Fractional Bits:小数位数

Coeffcient Structure:近似方式

(2)Data Path Option

Input Data Type:输入数据类型

Input Data Width:输入数据位宽

Input Data Fractional Bits:输入数据小数位数

Output Rounding Mode:近似方式

Output Width:输出位宽

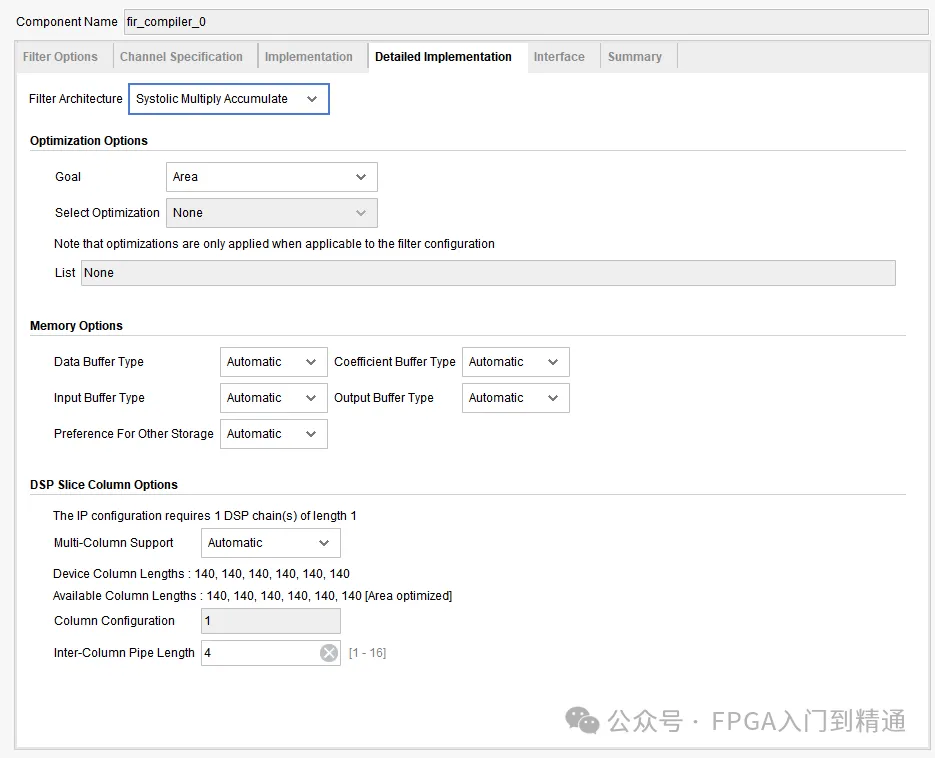

4、Detailed Implementation页面

这里是配置IP核布线优化策略,以及关键逻辑和功能的资源消耗类型设定,一般默认即可。

5、Interface页面

这是接口配置页面,可配置输入输出数据接口以及控制接口。

(1)Data Channel Options

TLAST信号配置:

不需要:不添加该端口。

矢量成帧:表示每个数据信道最后一个数据。

包成帧:同步输出数据通道tlast。

TUSER信号配置:

表示数据通道的起始信号,设置输入输出接口是否添加该信号。

Control Signals:

ARESETn:添加复位信号。

ACLKen:添加使能时钟信号。

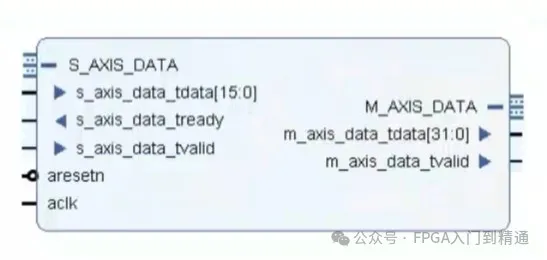

三、FIR IP核的主要接口

aclk:时钟信号;

s_axis_data_tdata:输入采样数据;

s_axis_data_tready:输出信号,1 表示IP核已准备好接收采样数据;

s_axis_data_tvalid:表示当前输入的采样数据是否有效;

m_axis_data_tdata:表示滤波后的输出数据;

m_axis_data_tvalid:表示当前输出数据是否有效。

更多功能和配置,请阅读官方手册: