文章来源:FPGA入门到精通

在数字信号处理的奇妙世界里,DDS(直接数字式频率合成器)信号发生器是一个极其重要的工具。它能够生成各种精确的波形,如正弦波、方波、三角波和锯齿波等,广泛应用于通信、雷达、电子测量等众多领域。

今天,我们就来一起探索如何基于 FPGA 实现一个简易的 DDS 信号发生器,即使你是 FPGA 小白,也能轻松上手!

一、DDS的工作原理

DDS(直接数字合成器,Direct Digital Synthesizer)是一种全新的数字信号频率合成方法,具有低成本、低功耗、高分辨率和快速转换时间等优点。

1、DDS结构

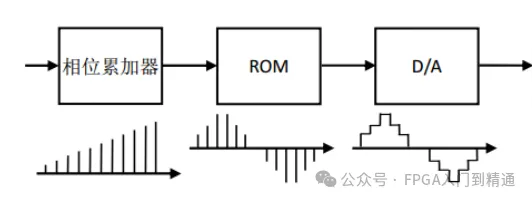

DDS常见结构示意图如下:

从上图中可以看到,DDS组成主要有相位累加器、相位调制器、波形数据表 ROM、D/A 转换器等。

结构说明:

(1)系统时钟CLK,周期表示为Tclk,频率表示为fclk。

(2)频率字输入F_WORD

一般为整数,控制输出信号的频率大小,数值越大,输出频率越高,常用K表示。

输入后接入了一个寄存器,主要作用是避免影响到后续的相位累加器。

(3)相位字输入P_WORD

一般为整数,控制输出信号的相位偏移,常用P表示。

输入后也接入了一个寄存器,主要作用是避免影响到后续的相位调制器。

(4)输出信号为CLK_OUT,频率为fout。

(5)相位累加器

输入为频率字输入K,表示相位增量,位宽用N表示。

(6)相位调制器

接收相位累加器输出的相位码, 再加上一个相位偏移值P,主要用于信号的相位调制,位宽用M表示,与ROM地址线位数相同。

(7)波形数据表ROM

存储了一个完整周期的波形信号数据(正弦波等等)。

例如假设ROM的地址位宽为13bit,数据位宽为16bit,即有8192个存储空间,每个存储存储2字节数据。

相位调制器传入的相位码为ROM读地址,查表获取对应的波形数据。

(8)D/A转换器

将查表获取的波形数据,转换成模拟信号输出。

说明:其中N一般大于M,所以一般传入相位调制器的是高M位,低N-M位用于K值计数。

2、DDS数字信号示意图

= 2^(M-2)

二、DDS实现

根据前面的分析,使用FPGA可以快速实现简易的DDS信号发生器。