作者:数字站

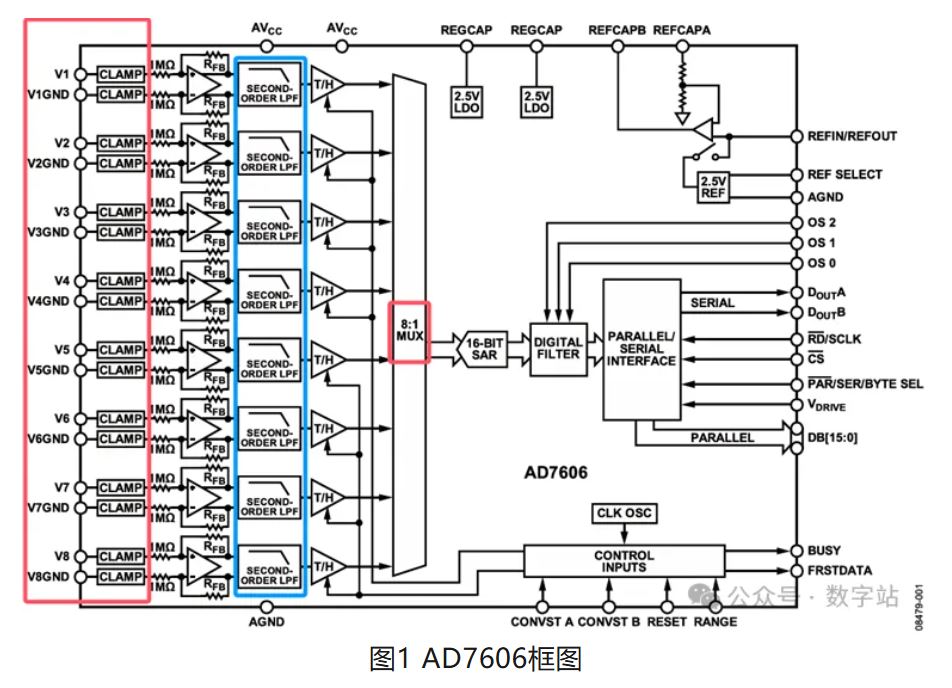

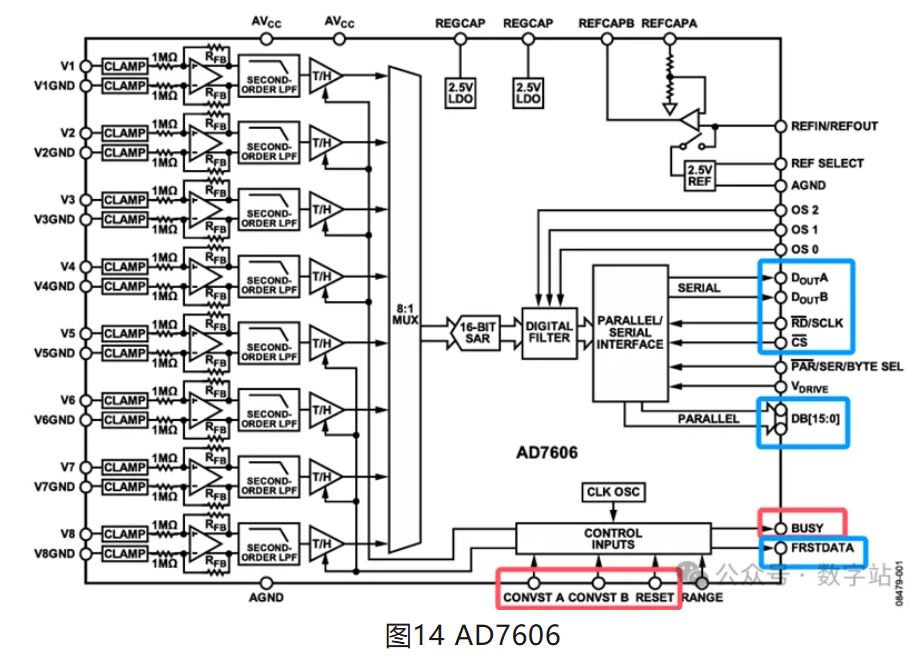

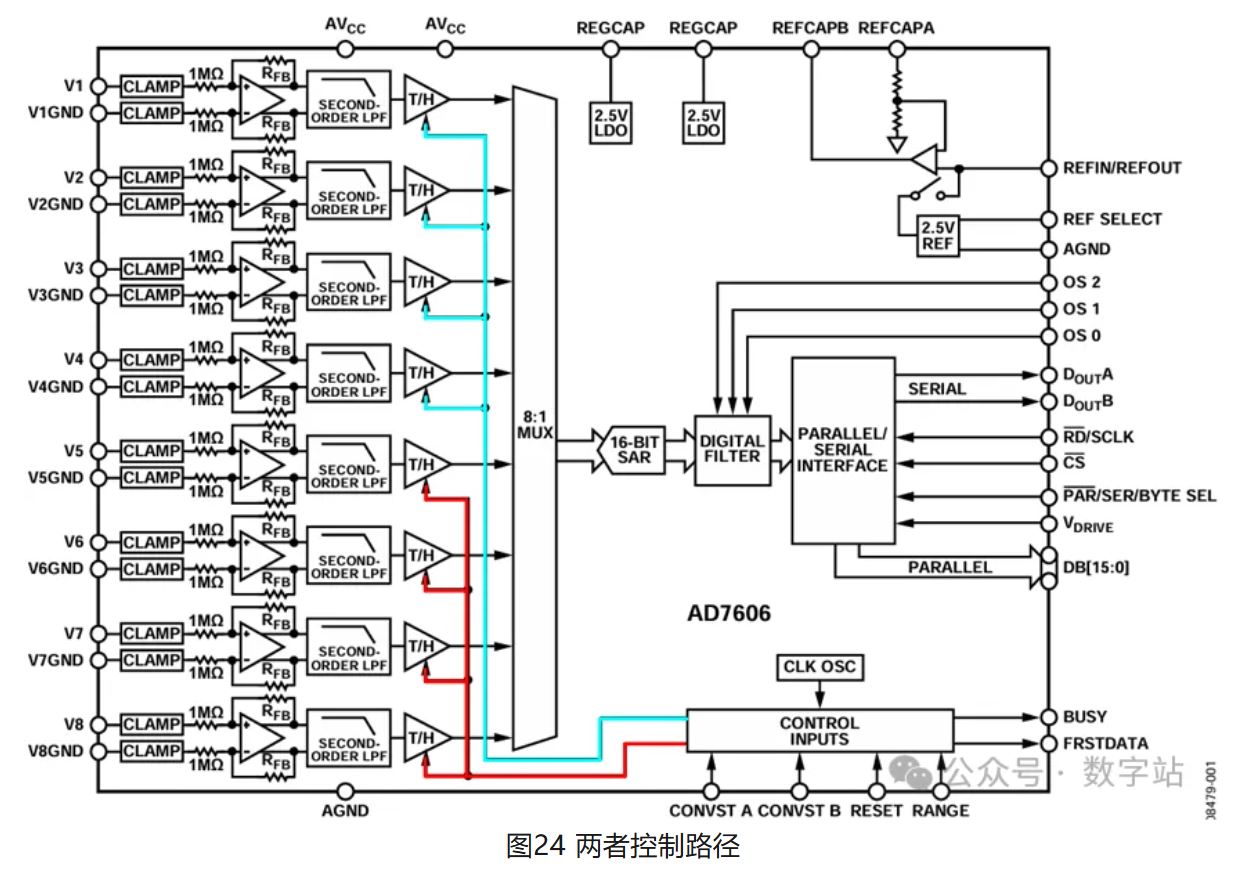

AD7606是ADI的一款8通道16位同步采样的ADC芯片,最大采样率可以得到200KSPS,模拟输入电压范围最大可以选择±5V或者±10V,采用5V单电源供电,通信接口有并口和SPI串口两种可选。这是一款特别好用的芯片,同步采样表示8个通道可以同时工作,且采样率都为200KSPS,相当于8个独立的单通道ADC。同时只需要5V单电源供电,也能采集负电压,简化PCB设计。如下图所示,左边是8路ADC通道,输入钳位保护电路为±16.5V,后面接1MΩ的电阻,即ADC模拟输入阻抗为1MΩ。之后经过一个抗混叠滤波器,截止频率为22KHz。ADC最大采样率为200KSPS,如果采集的信号想要在时域不失真,也就只能采集20KHz以下的信号(时域采集不失真,采样率至少是被采样信号的十倍),没有影响。

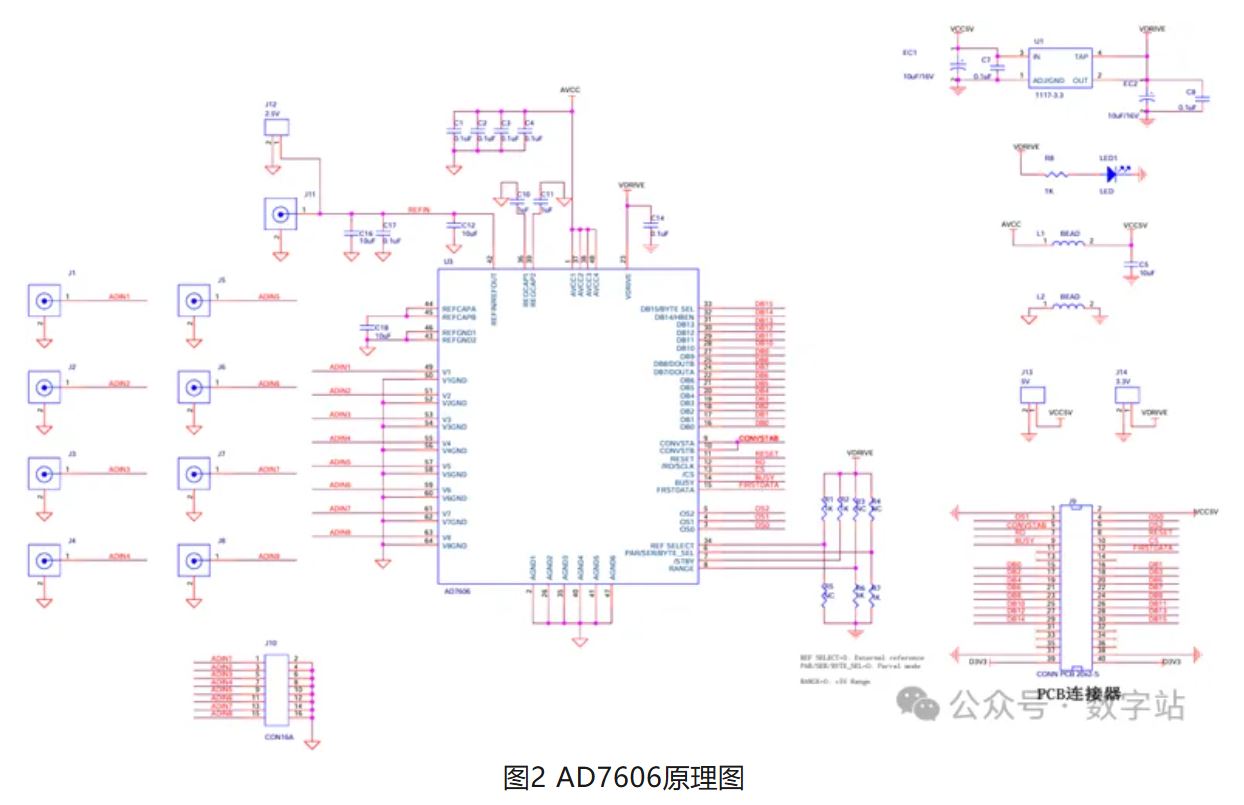

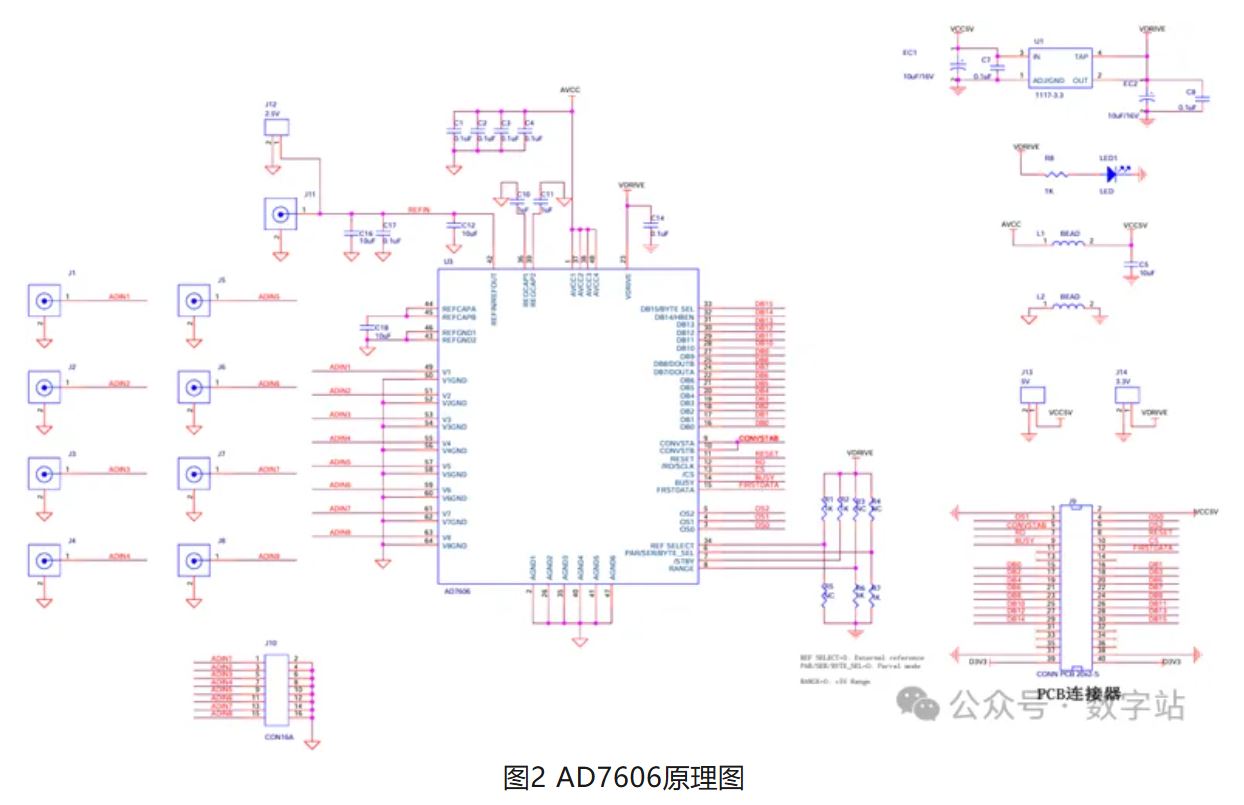

8路ADC转换之后,通过数据选择器选择其中一个ADC的数据给通信接口进行传输,以下结合原理图讲解该芯片。AD7606模块的原理图如下所示,该芯片内部并没有可以配置的寄存器,因此根据引脚进行分析最好。根据引脚功能不同,大致分为供电、模式配置、通信接口、采集接口几种。

电源引脚

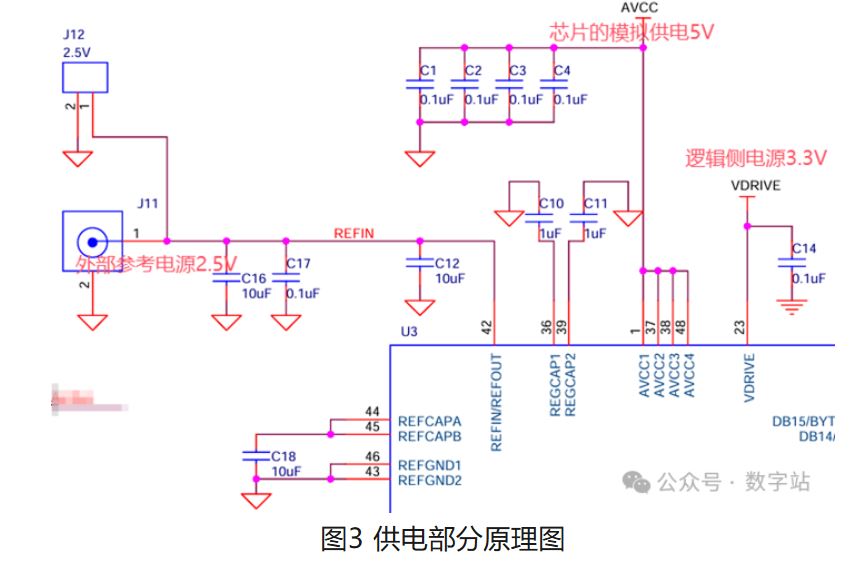

原理图如下所述,AVCC引脚是模拟侧供电引脚,电压范围4.75V ~ 5.25V。

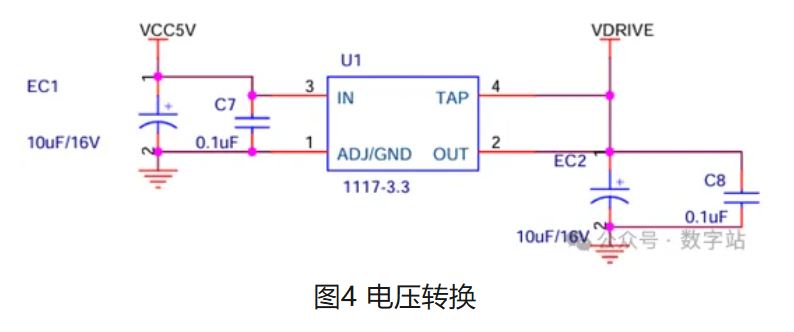

VDRVE为逻辑通信接口提供电源电压,电压范围2.3V~5.25V,一般使用3.3V,如下所示,模块使用1117芯片将5V转换为3.3V。

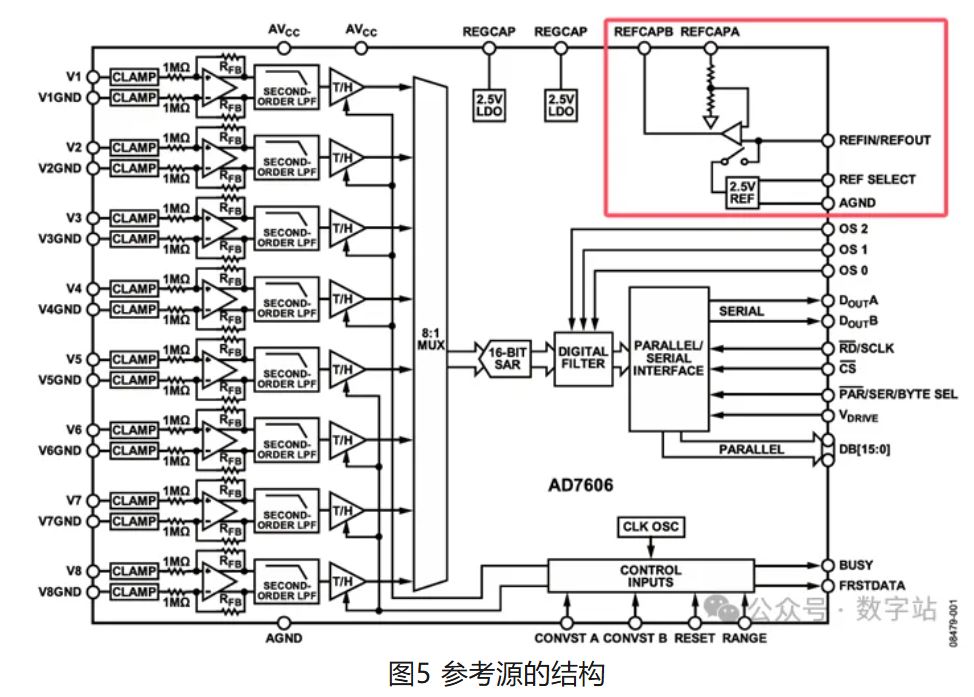

如下所示,AD7606内部有2.5V的内部参考源,通过REF SELECT引脚选择使用内部参考源还是外部参考源。当使用内部参考源时,REFIN/REFOUT会输出2.5V参考电压,使用外部参考源时,REFIN/REFOUT引脚需要输入一个2.5V电压作为外部参考源。

一般使用内部参考源即可,不管使用内部参考源还是外部参考源,REFIN/REFOUT都需要用10uf电容去耦,REFCAPA和REFCAPB引脚必须短路连接到一起,并通过10uf电容连接到REFGND,如图3所示。

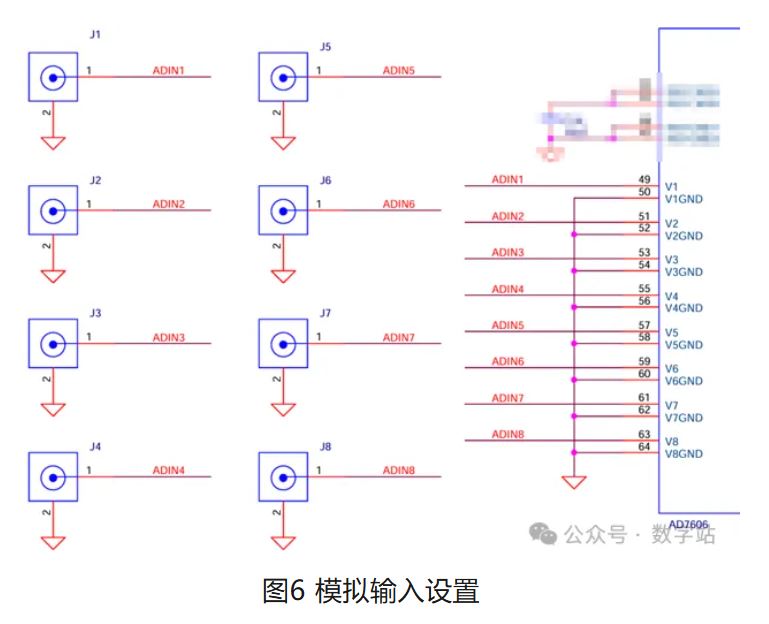

模拟输入接口

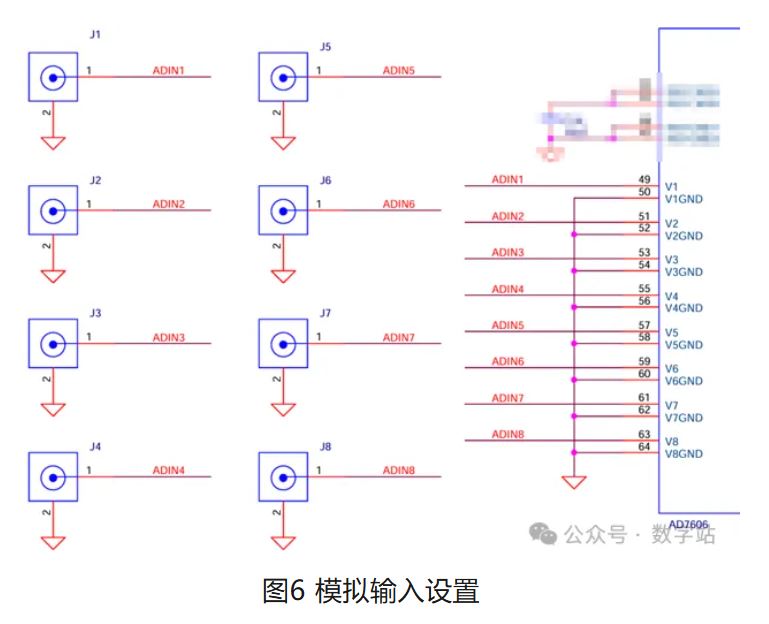

如下图所示,Vx表示第x个模拟通道输入,VxGND为第x个模拟通道的GND。输入电压钳位保护范围位±16.5V,不能超过此范围,否则会损坏芯片。输入电压范围根据RANGE的状态确定为±5V还是±10V,后文讲解。

配置接口

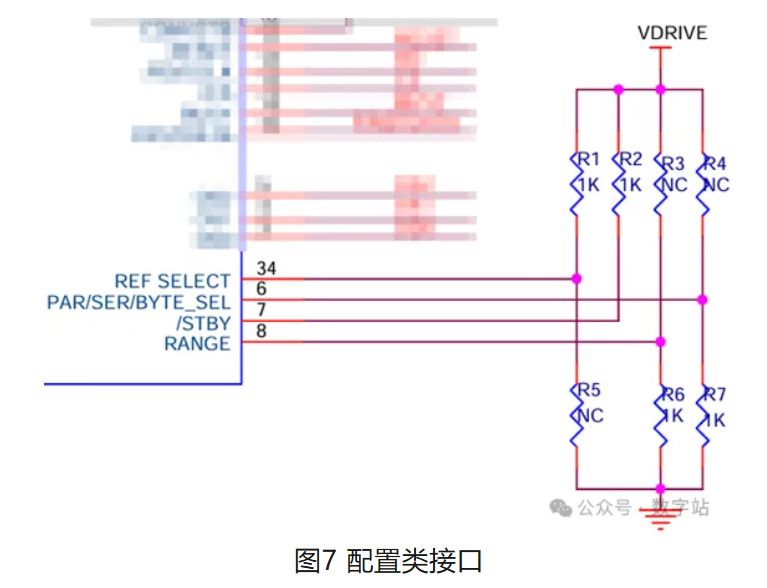

AD7606内部没有可以配置的寄存器,只能根据几个引脚的状态选择模拟输入电压的范围、参考源的来源、通信接口的类型、输出数据的类型,对应原理图如下所示。

首先REF SELECT用于选择图5中2.5V参考源的来源,REF SELECT为高电平时,AD7606使用内部参考源,否则使用外部参考源。上图R5默认不焊接(NC),因此该模块默认使用内部参考源。PAR/SER/BYTE_SEL为低电平时,AD7606使用16位并行接口通信,如果PAR/SER/BUTE_SEL为高电平,则使用SPI串行接口传输数据,如果PAR/SER/BUTE_SEL为高电平且DB15/BYTE_SEL为高电平,则使用字节并行接口模式。STBY引脚为高电平时,AD7606工作在正常模式下,STBY为低电平时,AD7606工作在省电模式下。RANGE用于确定模拟通道的电压输入范围,RANGE引脚为高电平时,模拟通道输入电压范围为±10V,否则模拟通道输入电压范围为±5V。上图RANGE默认接地,模拟输入电压范围选择±5V。

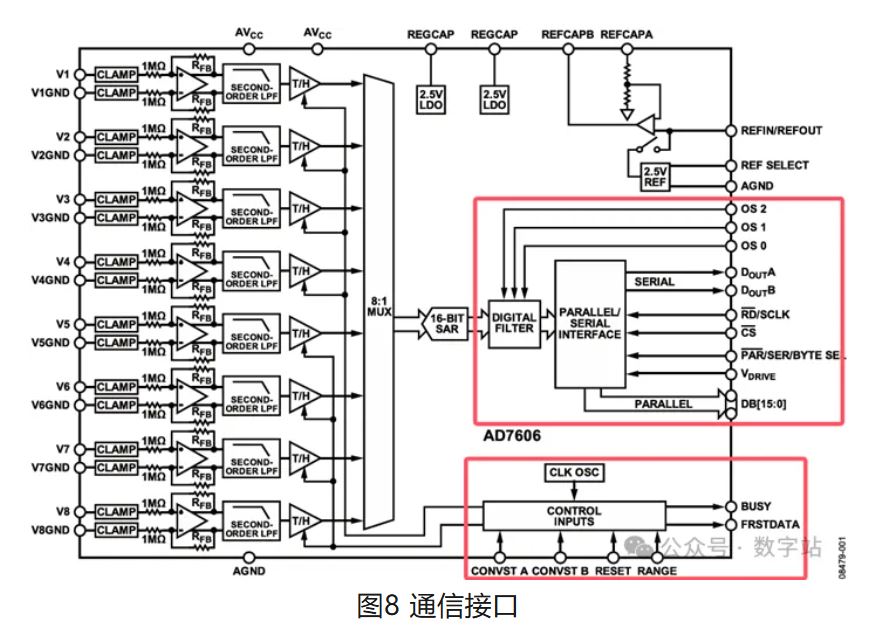

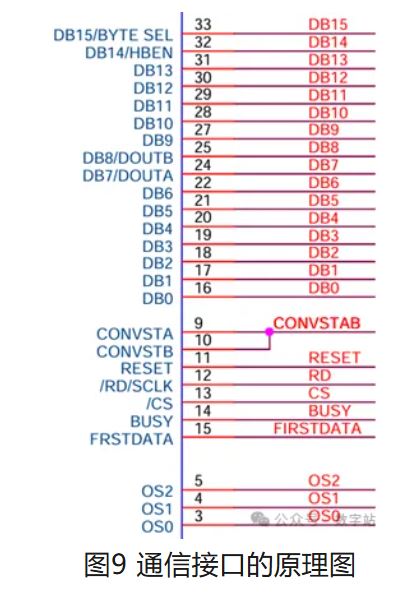

通信接口

最后剩下ADC转换部分控制及通信接口部分,如下图所示,上边的框为AD7606的通信接口,下边的框为控制和反映ADC模拟转换的状态。

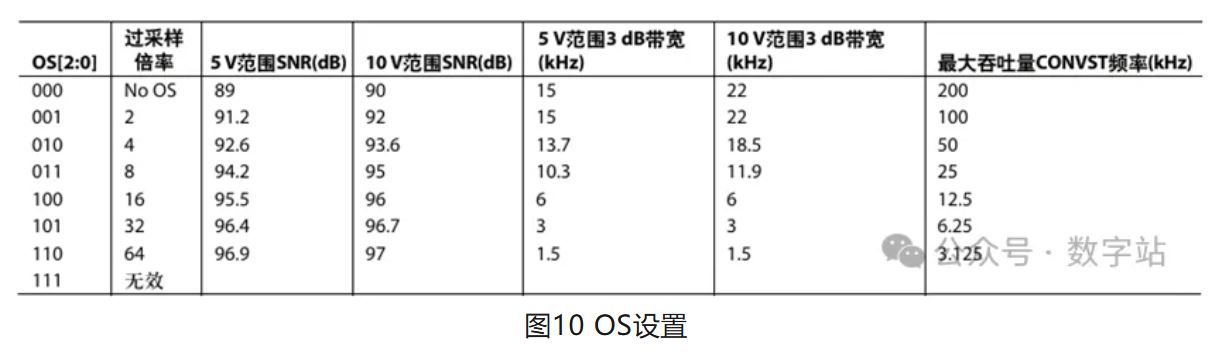

OS用于设置过采样倍率,如下图所示。手册对过采样的解释为多次采样然后取平均值输出。比如过采样倍率设置为16,则每个ADC通道在CONVSTx上升沿后采集16次输入数据,采集的16个数据取平均值后输出。

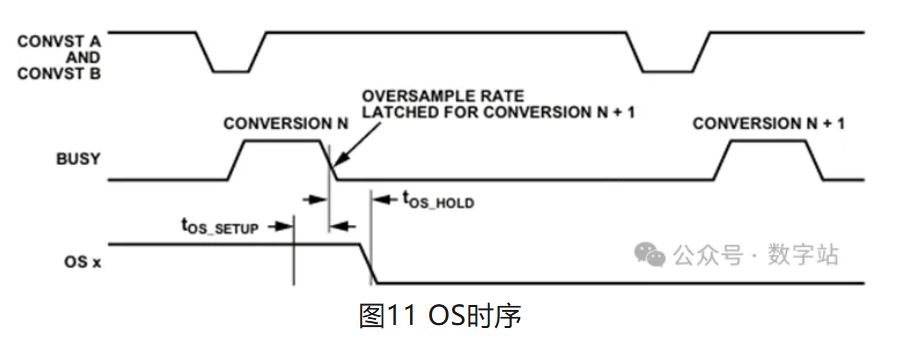

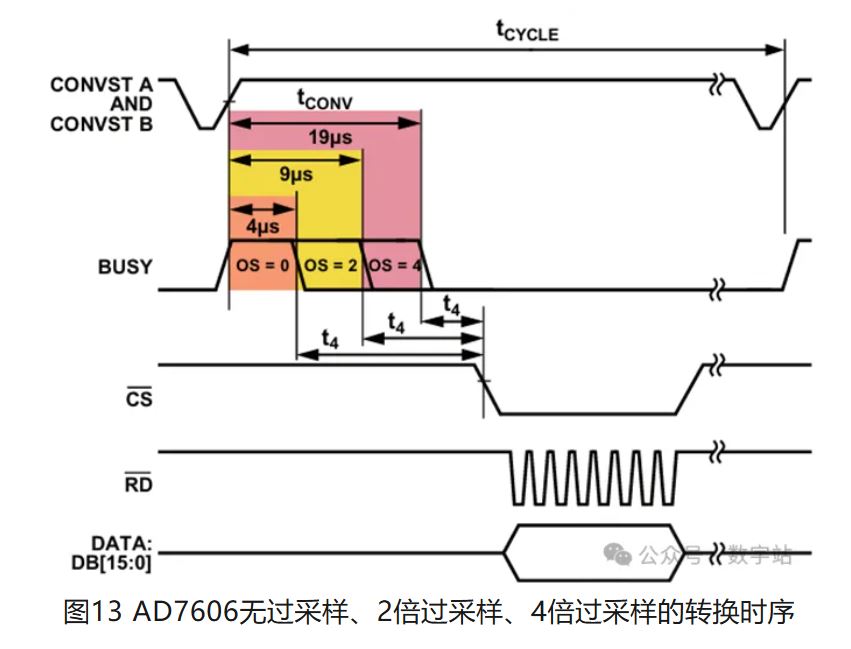

AD7606在BUSY的下降沿采集OS的状态,作为下次ADC转换的过采样倍率,对应时序如下所示。

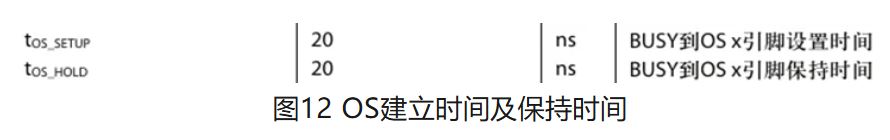

注意上图中OS的建立时间和保持时间,如下所示。最小值均为20ns,即OS必须在BUSY下降沿的前后20ns内保持稳定,否则可能会出现亚稳态。

使用过采样时,CONVSTA和CONVSTB必须连接在一起(后文讲解这两个引脚的作用),BUSY保持高电平的时间会延长,过采样倍率越高,BUSY持续高电平的时间越长,BUSY的下降沿表示ADC转换完成,对应时序如下所示。

一般使用不会使用过采样模式,如果使用可以参考这部分原理。其余的采样转换信号和通信相关信号放入后面接口时序部分讲解,配合时序进行分析会更加具体。

通信接口时序

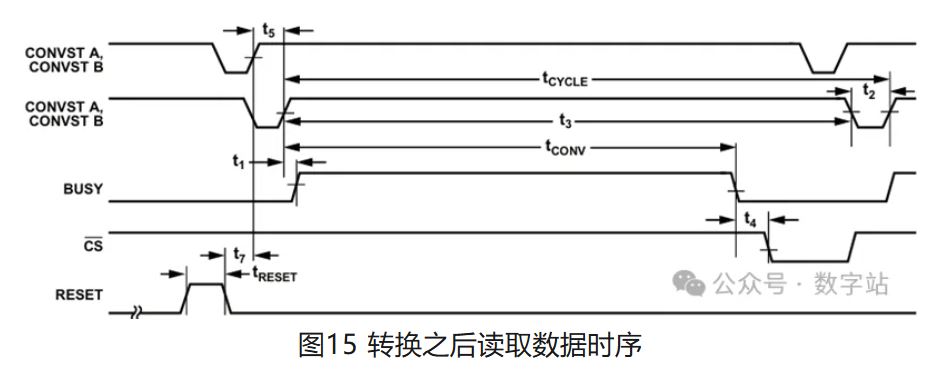

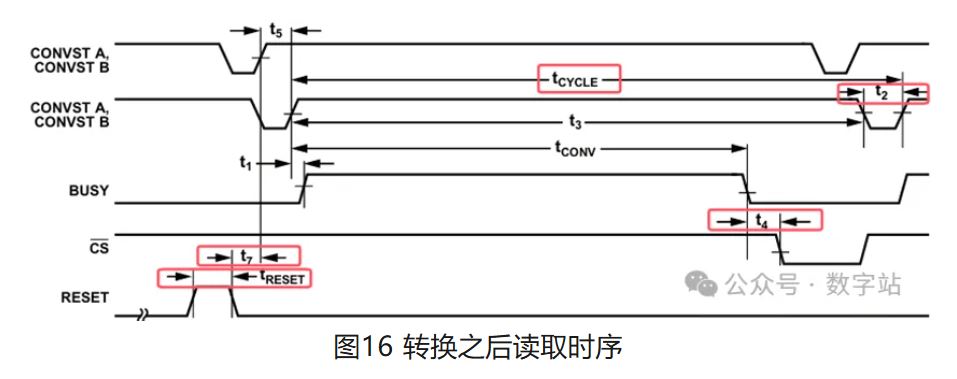

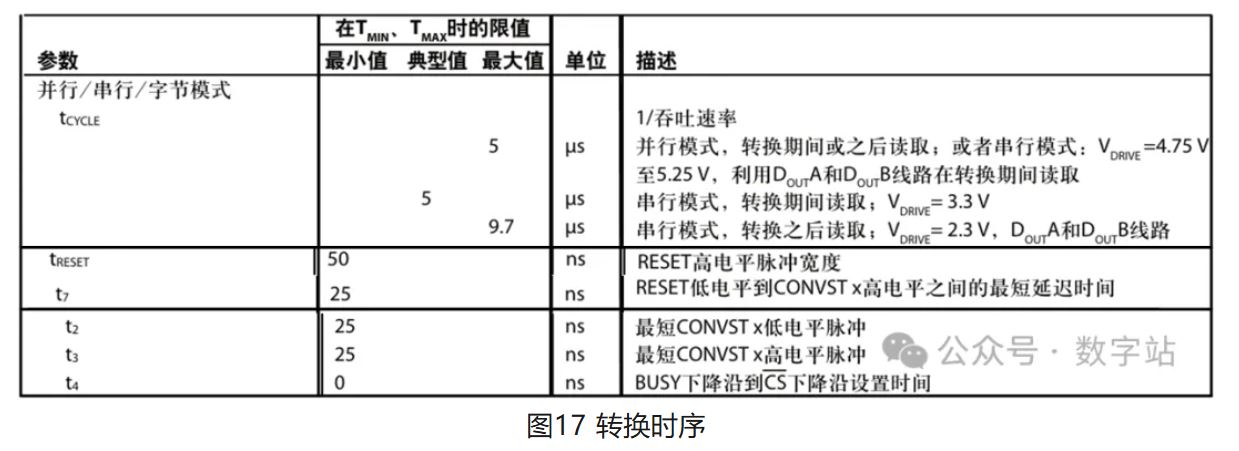

如下所示,CONVSTA和CONVSTB的上升沿用于分别控制4个通道的采样转换开始,BUSY的下降沿用于指示采样转换完成。用户检测到BUSY的下降沿后产生读数据时序。注意AD7606的采样率是指每个通道数模转换速率最大为200KSPS,并不是通信接口的最大速率为200KSPS。转换时序如下所示,建议在转换完成(BUSY下降沿)后,在拉低片选CS读取转换后的数据。虽然AD7606支持在转换期间读取数据,但是没有意义,不建议使用。

首先 RESET信号至少拉高50ns完成复位,AD7606检测到CONVSTA/CONVSTB上升沿后每个通道开始进行数模转换,同时BUSY拉高指示AD7606正在转换数据。BUSY拉低表示数模转换结束,用户通过拉低片选CS开始读取数据。

该时序需要特别注意以上几个时间,后续写驱动会使用到。如下所示,必须在复位信号RESET拉低至少25ns(t7)后才能拉高CONVSTA/CONVSTB开始采集数据转换。CONVSTA/CONVSTB的低电平最少持续25ns(t2),当转换完成(BUSY拉低)时,用户可以立即读取数据(t4最小值为0)。

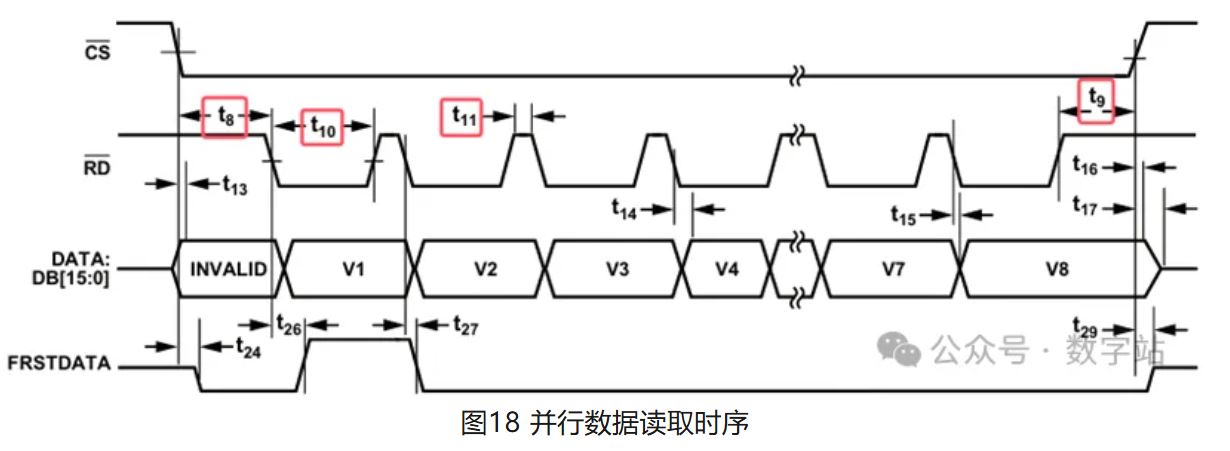

BUSY的相关时间可以不用太关注,因为这是AD7606芯片的输出信号。用户读取数据的并行接口时序如下所示,由图16可知,检测BUSY下降沿后拉低片选CS,之后AD7607在RD的下降沿输出16位并行数据DB[15:0],用户在RD的上升沿读取DB[15:0],FRSTDATA高电平指示第一通道转换完成的并行数据V1,当八个通道全部读取完成后,片选拉高,完成一次数据读取。

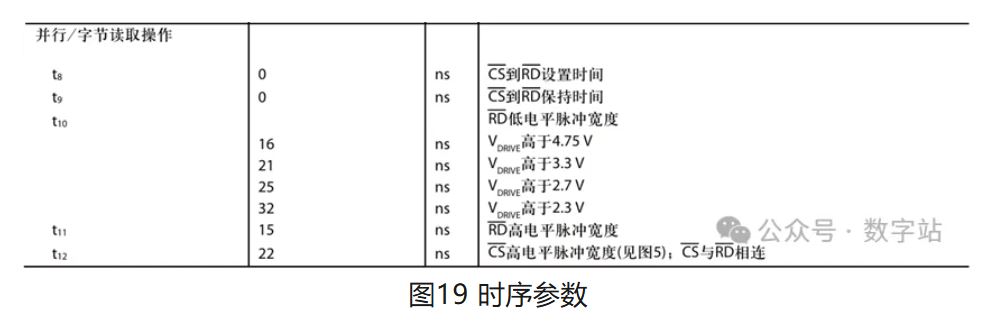

上图中需要注意几个时序参数,如下所示,t8和t9最小值可以为0,表示CS和RD可以同时变化。特别注意t10和t11,t10表示RD低电平的持续时间,根据逻辑侧供电电源有关,一般VDRIVE为3.3V,因此RD低电平最小时间为21ns,t11表示RD高电平的持续时间,最小值为15ns。因此当逻辑接口供电为3.3V时,RD信号最小周期为21ns + 15ns = 37ns,对应最大频率为27MHz,因此接口读取数据速率与采样速率没有关系。

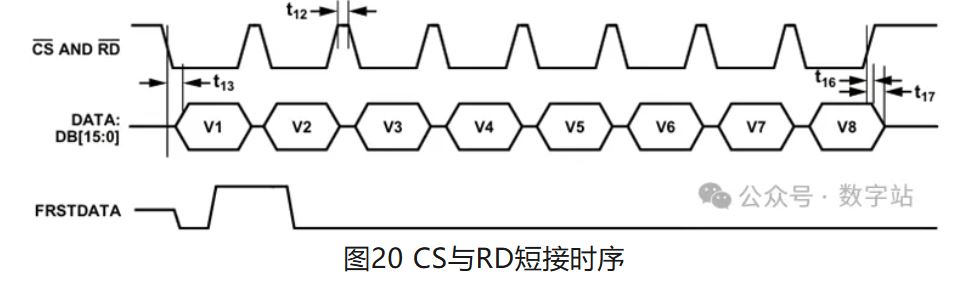

同时并行接口支持如下时序,将片选CS和读使能RD短接,比较常用。此时序RD的最小时间为22ns(t12)。

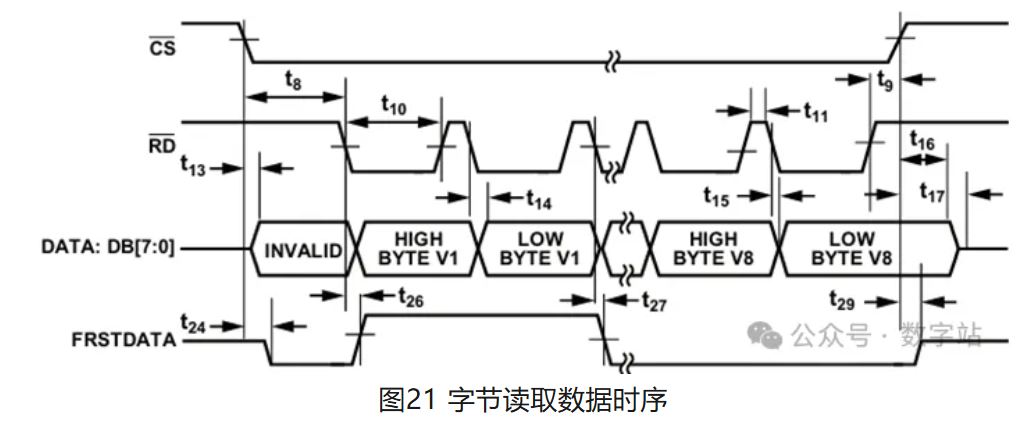

AD7606还指示字节模式,对应时序如下所示,数据通过DB[7:0]传输,每个RD周期传输一个字节数据。首先传输第一个通道的高字节数据,经过两个RD周期传输完第一个通道转换完成的数据。

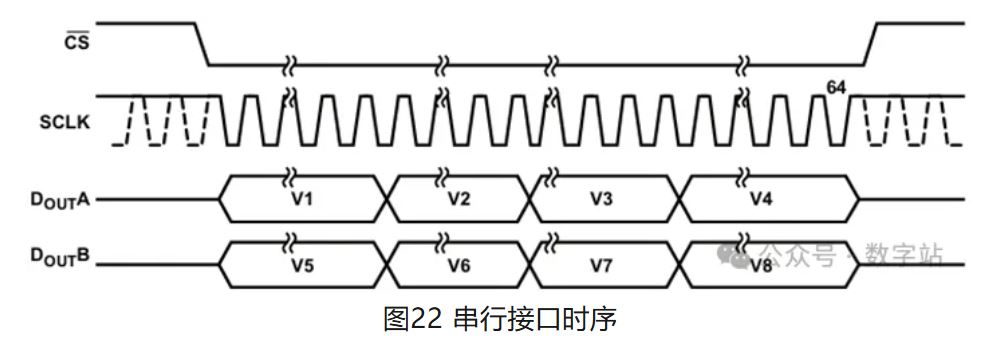

当PAR/SER/BYTE SEL为高电平时,通信接口将使用串行模式,可以使用双通道(DOUTA和DOUTB)传输数据,也可以使用单通道(DOUTA或DOUTB)传输数据。下图是双通道传输数据的串行时序,DOUTA先后传输通道一(V1)、通道二(V2)、通道三(V3)、通道四(V4)的数据,DOUTB先后传输V5、V6、V7、V8通道的数据,需要64个时钟才能传输完所有通道的数据。

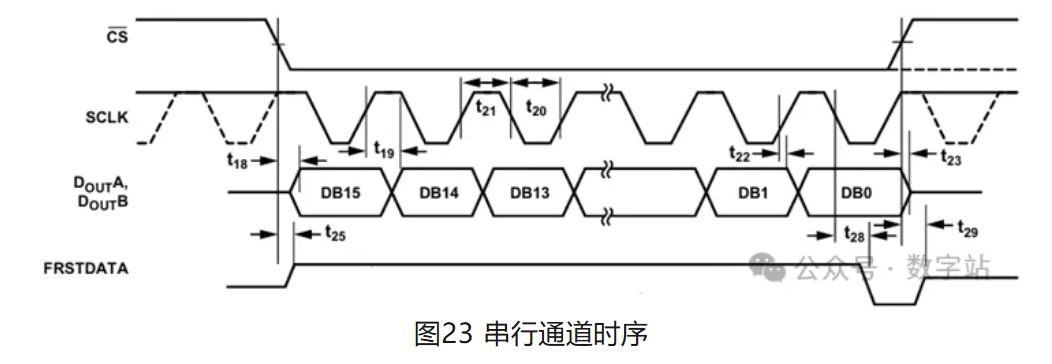

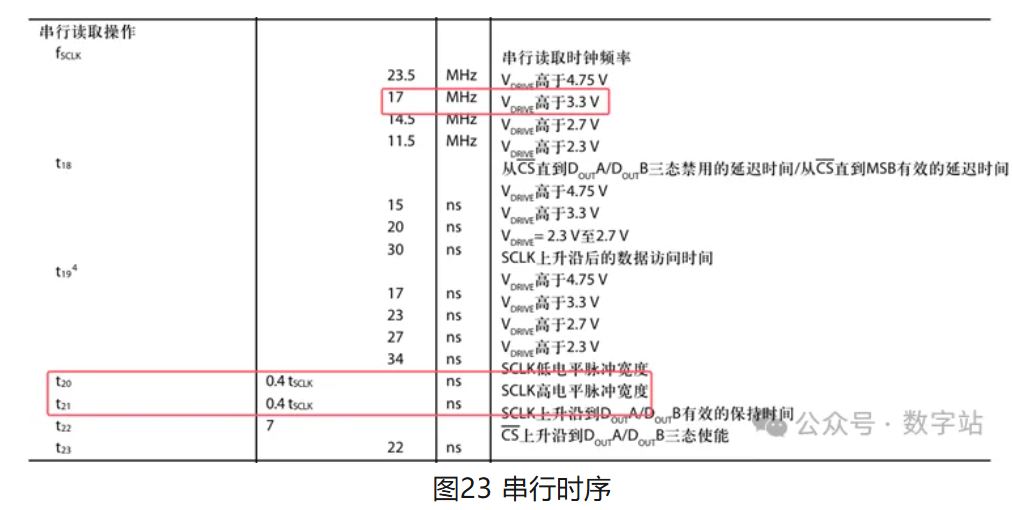

如下所示,串行接口时钟SCLK最大为17MHz,高低电平持续最短时间为0.4倍,因为有变化时间,因此最小值不是0.5。

同时串行模式还支持单通道传输数据,FRSTDATA的高电平用于指示传输的第一个16位数据(高电平在串行模式下持续16个SCLK时钟)。如果只使用DOUTA传输数据,则需要128个SCLK时钟依次传输通道V1、V2、V3、V4、V5、V6、V7、V8的数据,均先传输高位数据。如果只使用DOUTB传输数据,128个SCLK时钟先后传输V5、V6、V7、V8、V1、V2、V3、V4。一般不推荐使用串行单通道传输数据,因为需要的周期比较长,如果转换结束后才开始读取数据,那么就会大幅度降低采样率。前面都是将CONVSTA和CONVSTB连接在一起使用,其实两者可以分开使用。如下图所示,控制部分其实分为两路去控制4个通道的数据采集和转换,CONVSTA通过蓝色路径控制通道一到通道四,CONVSTB通过红色路径控制通道五到通道八,可以通过控制CONVSTA和CONVSTB用来控制两组通道采集数据的相位差。

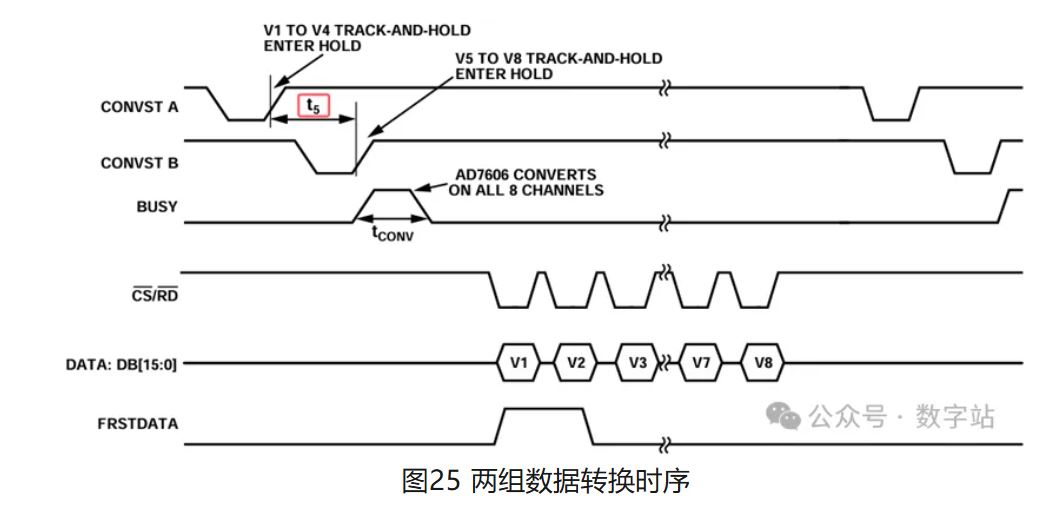

如下所示,AD7606在CONVSTA的上升沿锁存通道一、通道二、通道三、通道四输入数据的状态,在CONVSTB上升沿锁存通道五、通道六、通道七、通道八输入数据的状态。通过调整CONVSTA和CONVSTB的上升沿,就可以控制两组通道的采样相位,两个上升沿间隔最大值为0.5ms(t5最大时间为0.5ms),这种模式OS必须设置为零,不能使用过采样。当AD7606检测到CONVSTA和CONVSTB上升沿后,BUSY拉高开始对八个通道采集的数据进行转换。

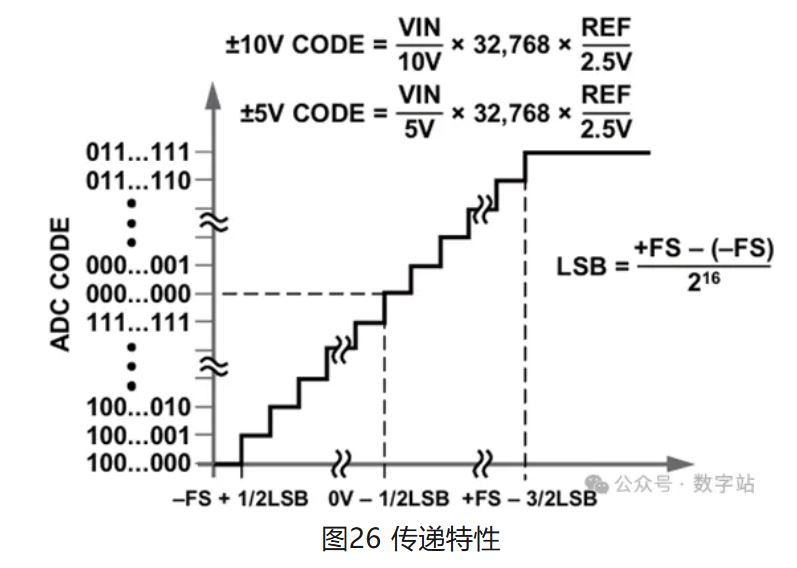

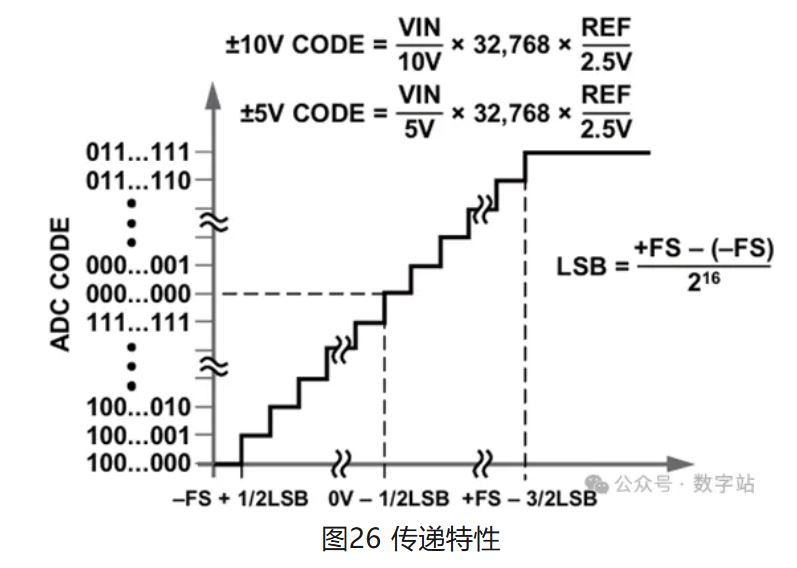

AD7606输出16位补码数据,转换关系如下所示,VIN为输入模拟电压,CODE为通信接口输出的转换后的16位并行补码数据,REF为参考时钟源的电压。

总结

CONVSTA和CONVSTB的上升沿分别控制四个通道的采样保持,BUSY下降沿用于指示八个通道完成模数转换。然后用户可以通过并行或者串行接口时序读取数据,并行接口允许片选CS和读使能RD短接,数据在RD下降沿输出,用户在RD上升沿采集每个通道的补码数据。串行接口在传输数据时,片选CS必须保持低电平,数据在SCLK的下降沿输出,用户在SCLK采集DOUTA和DOUTB的数据,首先传输最高位数据。DOUTA依次传输V1、V2、V3、V4数据,DOUTB依次传输V5、V6、V7、V8数据,总共需要64个SCLK才能传输完8个通道数据。串行单通道模式下,需要128个SCLK时钟才能传输数据,如果使用DOUTA则依次传输V1、V2、V3、V4、V5、V6、V7、V8,如果只使用DOUTB,则依次传输V5、V6、V7、V8、V1、V2、V3、V4数据。FPGA一般使用16位并行模式传输数据,且CONVSTA和CONVSTB连接在一起,两组通道同时采样,没有相位差,片选CS和读使能RD短接,这就是最简单的采样方式。当然我这个模块把CONVSTA和CONVSTB短接,因此不能通过程序实现两组通道相位差采集数据了,只能八通道同步采样数据。

本文内容来自对AD7606手册及原理图的分析,需要的可以在公众号后台回复“AD7606手册“(不包括引号)获取手册及模块原理图。

文章来源:数字站