作者:FPGA技术实战

1. 配置访问时间

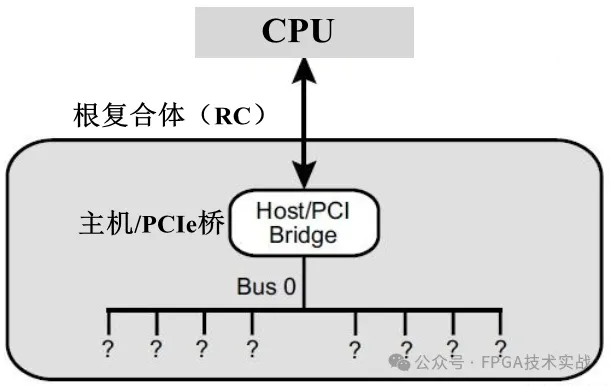

在PCIe的标准系统中,当系统通电时,处理器上运行的配置软件开始扫描PCIe总线以发现机器拓扑。扫描PCIe层次结构以确定其拓扑结构的过程称为枚举过程,根复合体(RC)通过向设备发起配置事务来实现枚举过程。

图1:系统启动时的PCIe拓扑图

所有PCIe设备都应已与其链路伙伴建立链路,并在枚举过程中准备好接受配置请求。因此,对设备在通电后何时需要准备好接受配置请求有要求,如果不符合要求,则会发生以下情况:

•如果设备未就绪且未响应配置请求,则根复合体不会发现它并将其视为不存在;

•操作系统不报告设备的存在,用户应用程序无法与设备通信。

1.1 配置访问规范要求

PCIe规范项与配置访问相关包括:

(1)PCIe基础规范V1.1版第6.6节规定:“系统必须保证所有在启动时可见的软件组件在根复合体基本重置结束后100ms内准备好接收配置请求。”

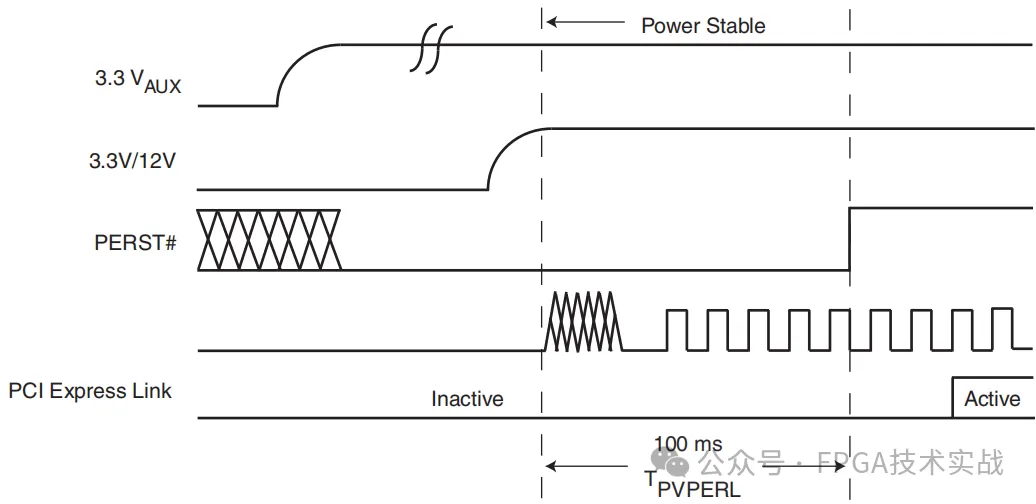

(2)PCIe基础规范V1.1第6.6节定义了“在提供电源和PERST#的情况下”所需的三个参数。参数TPVPERL适用于FPGA配置时序,定义为:

TPVPERL-PERST#必须在电源有效后至少保持活动状态这么长时间。

PCIe基本规范没有给出TPVPERL的具体值,只定义了它的含义。图2显示了电源稳定和PERST#之间的关系。

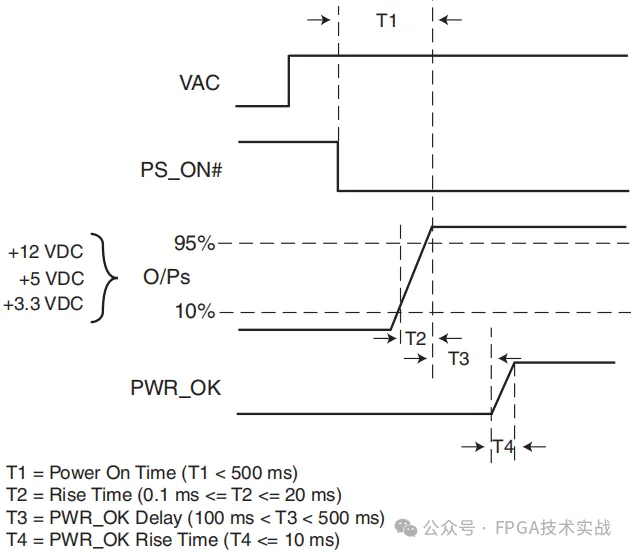

表1:TPVPERL规格

注:尽管TPWRVLD包含在方程式2中,但在本次讨论中尚未定义,因为它取决于使用的系统类型。真实系统中的电路板电源部分为基于ATX和非基于ATX的系统定义了TPWRVLD。

FPGA配置时间仅在冷启动时相关,后续的热重置或热复位不会导致FPGA的重新配置。如果设计因FPGA配置而出现问题,您应该发出一个热复位作为简单的测试,复位系统,包括PCI Express链路,但保持电路板通电。如果问题没有出现,则问题可能与FPGA配置时间有关。

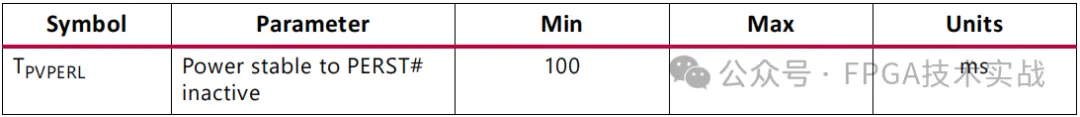

2. 实际系统中板卡电源

在PCIe系统中可能会使用多个板卡,英特尔认可的ATX电源设计规范被用作指导方针,因此大多数主板都遵循该规范,如果是基于英特尔的主板,则100%遵循该规范。ATX 12V电源设计指南中描述了电源轨和电源有效信号之间的关系,如图3所示。

同样,FPGA配置时间方程为:

FPGA配置时间≤TPWRVLD+100ms

100 ms≤TPWRVLD≤500 ms

因此,FPGA配置时间需满足以下要求:

FPGA配置时间≤200ms(适用于基于ATX的主板)

FPGA配置时间≤100ms(适用于非ATX主板)

注意:(1)非基于ATX的主板的第二个方程假设TPWRVLD值为0ms,因为在此上下文中没有定义。使用非ATX主板的设计人员应评估自己的电源设计,以获得TPWRVLD的值。

(2)本节假设FPGA功率(VCCINT)在PWR_OK被断言之前或同时是稳定的。如果不是这样,则必须从FPGA配置的可用时间中减去额外的时间。

2.1 热插拔系统

热插拔系统通常使用位于系统主板上的热插拔电源控制器。许多分立的热插拔电源控制器将TPVPERL扩展到最小值100ms以上。插件卡设计人员应参考热插拔电源控制数据表以确定TPVPERL的值。如果热插拔功率控制器未知,则应假设TPVPERR值为100ms。

2.2 FPGA配置建议

为了缩短FPGA配置时间,Xilinx建议使用并行NOR闪存的BPI配置模式,该模式支持高速同步读取操作。

3. 7系列器件的FPGA配置时间

在加电期间,FPGA配置顺序分三个步骤执行:

(1)等待FPGA中所有电压(VCCINT、VCCAUX和VCCO_0)的上电复位(POR)跳闸,称为POR跳闸时间。

(2)在接受比特流传输之前,等待INIT_B完成(取消确认)以允许FPGA初始化。

注:一般来说,步骤1和2要求≤50 ms

(3)等待DONE的断言,比特流传输所需的实际时间取决于:

○比特流大小

○时钟(CCLK)频率

○闪存设备的传输模式(和数据总线宽度)

-SPI=串行外围接口(x1、x2或x4)

-BPI=字节外围接口(x8或x16)

比特流传输时间可以使以下方程进行估计:

比特流传输时间=(比特流大小,单位为比特)/(CCLK频率)/(数据总线宽度,单位为位)

文章来源:FPGA技术实战