文章来源:Open FPGA

在 FPGA 设计领域,资源利用率和性能优化始终是工程师关注的焦点。CoreScore 是一个开源项目,旨在通过部署尽可能多的 SERV 核心(世界上最小的 RISC-V 处理器)在 FPGA 上,评估 FPGA 的资源承载能力和综合布线工具的效率。

什么是 CoreScore?

CoreScore 是由 Olof Kindgren 发起的开源基准测试项目,利用 SERV 核心在不同 FPGA 上进行部署,测试其最大承载能力。该项目不仅评估 FPGA 的资源利用率,还考察综合(Synthesis)和布局布线(Place & Route)工具的性能。

SERV 核心简介

SERV(SErial RISC-V)是目前已知最小的 RISC-V 处理器核心,由 Olof Kindgren 开发。其设计目标是极致精简,适用于资源受限的应用场景。SERV 的体积小巧,使其成为在 FPGA 上进行大规模部署的理想选择。

CoreScore 的工作原理与流程

CoreScore 的主要流程包括:

环境准备:安装 FuseSoC 工具,设置工作目录,并添加必要的库。

目标选择:选择支持的 FPGA 开发板作为目标,例如 CYC1000。

构建与部署:使用 FuseSoC 构建项目,并将生成的比特流文件部署到 FPGA 上。

结果评估:运行 corecount 工具,通过串口通信获取实际部署的 SERV 核心数量。

该流程不仅测试了 FPGA 的资源承载能力,还评估了综合和布局布线工具的效率。

一、安装FuseSoC

pip install fusesoc

设置工作区目录并获取 FuseSoC 基础库

mkdir workspace cd workspace fusesoc library add fusesoc-cores https://github.com/fusesoc/fusesoc-cores

将 CoreScore 添加为工作区中的库

fusesoc library add corescore https://github.com/olofk/corescore

检查可用的 corescore 目标

fusesoc core show corescore

构建一个受支持的目标(cyc1000 是当前支持的核心之一)

fusesoc run --target=cyc1000 corescore

如果电路板已连接,则会自动编程。否则,请连接并运行fusesoc run --run --target=cyc1000 corescore编程,无需重建

运行 corecount 实用程序(可能需要调整正确的 UART 端口)

python3 fusesoc_libraries/corescore/sw/corecount.py /dev/ttyUSB0

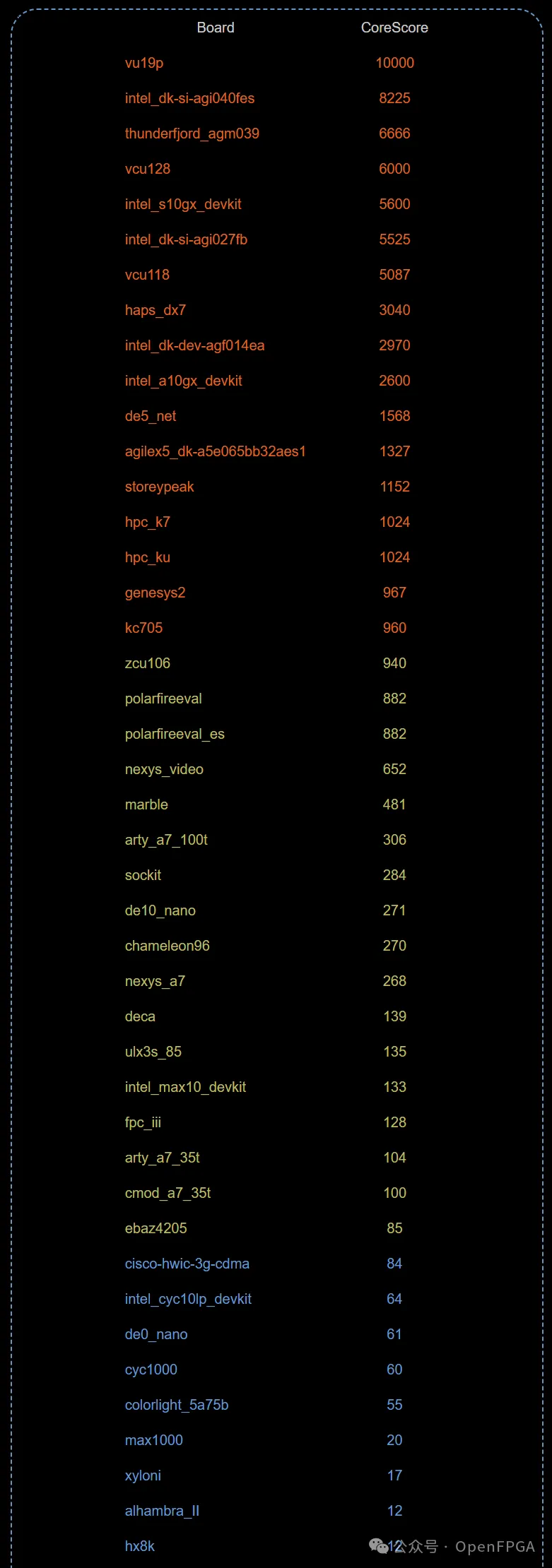

CoreScore 世界排名

CoreScore 项目维护了一个世界排名榜,记录了在不同 FPGA 上成功部署的 SERV 核心数量。这一排名激励了全球的开发者不断挑战 FPGA 的极限,推动了硬件设计的创新。

如何参与 CoreScore 项目

CoreScore 项目托管在 GitHub 上,任何人都可以访问其源代码、文档和示例设计。项目采用 Apache-2.0 许可证,允许自由使用、修改和分发。开发者可以通过提交问题、贡献代码或改进文档的方式参与其中。

GitHub:https://github.com/olofk/corescore

总结

随着 FPGA 技术的不断发展,CoreScore 项目也在持续进化。未来,CoreScore 将继续致力于推动开源 FPGA 设计工具的发展,降低硬件设计的门槛,促进创新和研究。