代码下载

spi_to_i2c_bridge.vhd (8.6 KB)

spi_slave.vhd (8.1 KB)

spi_to_i2c.vhd (7.0 KB)

i2c_master.vhd (12.9 KB)

SPI转I2C桥接器的VHDL源代码

用户可自定义系统时钟

用户可自定义SPI模式

用户可自定义I2C串行时钟频率

专为读写8位I2C从设备寄存器设计

向SPI主设备报告I2C从设备应答错误

符合NXP UM10204单主I2C总线规范

采用7位地址的I2C从设备寻址

兼容I2C从设备的时钟拉伸功能

不推荐用于多主I2C总线(无仲裁或同步机制)

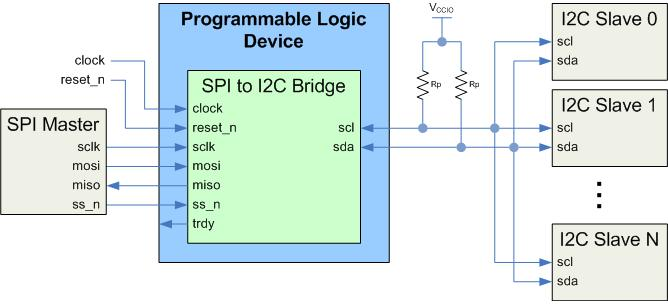

本文详述了用于单主I2C总线的SPI转I2C桥接组件,采用VHDL编写,适用于CPLD和FPGA。该桥接器旨在使SPI主设备能够读写8位I2C从设备寄存器。设计基于Quartus II 11.1版本开发。资源需求取决于具体实现方案。图1展示了集成SPI转I2C桥接器的典型系统示例。

图 1. SPI转I2C桥接实现示例

SPI和I2C都是流行的串行通信协议。

SPI通信方案采用四线制全双工数据链路。主机通过拉低从机选择(SS)线来启动传输。由主机驱动的串行时钟(SCLK)线提供同步时钟源。主机通过主出从入(MOSI)线发送数据,通过主入从出(MISO)线接收数据。

主机可通过多种技术与多个从机通信。最常见配置中,每个从机有独立的SS线,但与其他从机共享SCLK、MISO和MOSI线。当从机的SS线未被拉低时,该从机会忽略共享线路。

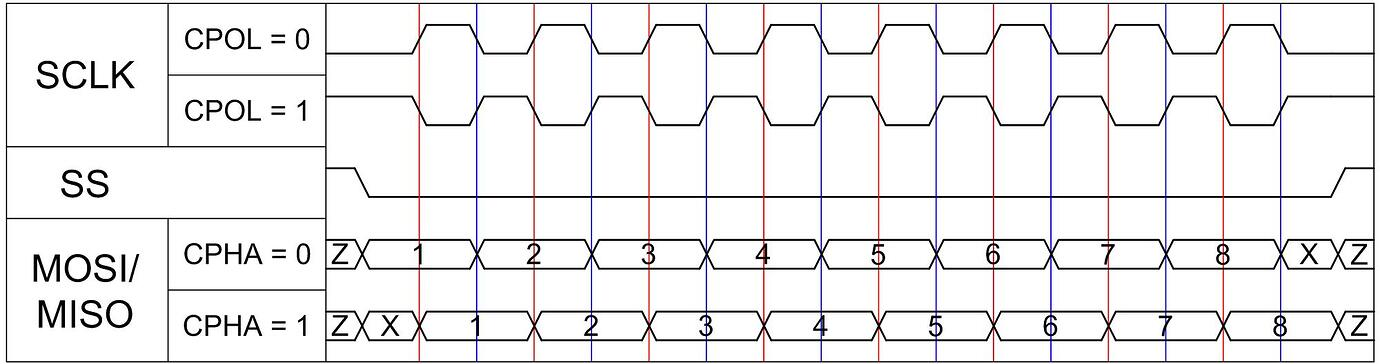

SPI有四种工作模式,基于两个参数:时钟极性(CPOL)和时钟相位(CPHA)。主从设备必须使用相同模式才能清晰通信。若CPOL为0,则SCLK通常为低电平,首个时钟边沿为上升沿。若CPOL为1,则SCLK通常为高电平,首个时钟边沿为下降沿。CPHA定义数据对齐方式。若CPHA为0,则首个数据位在SS下降沿写入,在首个SCLK边沿读取。若CPHA为1,数据在首个SCLK边沿写入,在第二个SCLK边沿读取。图2的时序图展示了四种SPI模式。

图 2. SPI时序图

I2C

I2C总线是由飞利浦(现恩智浦)发明并规范的双线半双工数据链路。I2C总线的两条线SDA和SCL均为双向开漏结构,通过电阻上拉。SCL是串行时钟线,SDA是串行数据线。总线上的设备通过将线路拉至低电平发送逻辑0,释放线路(保持悬空)发送逻辑1。

更多信息请参阅附加资料章节中的I2C规范文档。该文档详细说明了协议规范、电气参数、上拉电阻阻值计算等内容。

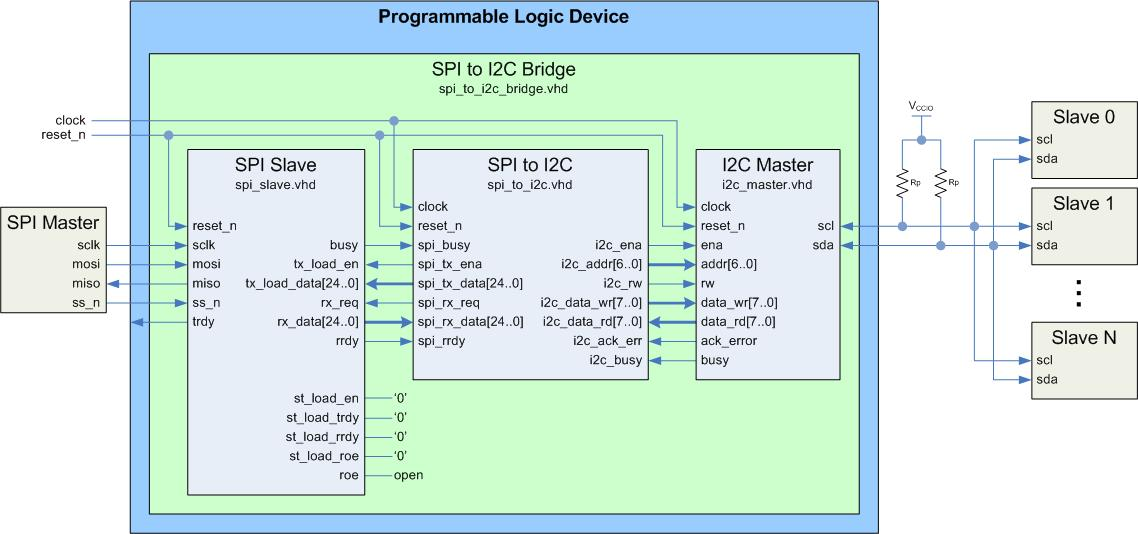

SPI转I2C桥接器的源代码包含以下四个VHDL文件:

spi_to_i2c_bridge.vhd

spi_slave.vhd

spi_to_i2c.vhd

i2c_master.vhd

图3展示了这些文件之间的关系。

图 3. SPI转I2C桥接架构

spi_to_i2c_bridge.vhd是顶层封装文件,负责实例化并连接其他三个模块。

spi_slave.vhd定义了直接与外部SPI主机交互的SPI从机组件。该SPI从机组件(v1.2)的详细文档可在此处获取。

同理,i2c_master.vhd定义了直接与I2C从机通信的I2C主机组件。该I2C主机组件(v2.2)的详细文档可在此处获取。

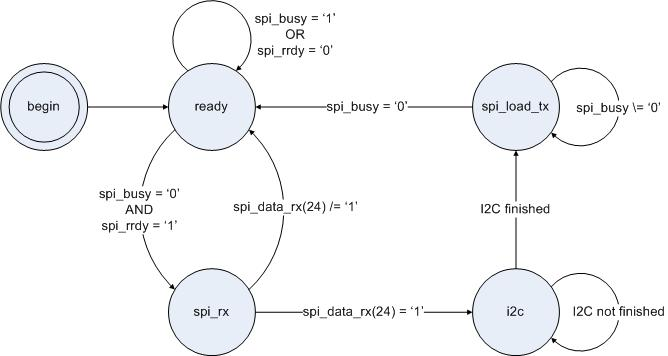

spi_to_i2c.vhd文件控制桥接操作,实现SPI从机与I2C主机间的协议转换。图4的状态图描述了其工作流程。桥接器在就绪(ready ) 状态等待,持续监测SPI从机的忙( busy ) 信号和接收就绪(rrdy)状态寄存器。当SPI从机接收到主机发送的新数据时,rrdy 端口会置位。忙( busy ) 信号用于指示SPI从机的工作状态。当两个条件同时满足时,桥接器向从机请求新SPI数据并进入spi_rx 状态。新的SPI数据随后被锁存。若数据包含执行I2C传输的指令(第25位为‘1’),则进入i2c 状态。若指令未请求I2C传输(第25位为‘0’),桥接器返回就绪( ready )状态。进入i2c 状态后,桥接逻辑通过I2C主控组件在I2C总线上执行传输。该传输需要若干时钟周期。其持续时间取决于I2C串行总线速率、系统时钟及从设备是否启用时钟拉伸。完成后,桥接器转入spi_load_tx 状态。桥接器等待SPI从设备空闲,随后将I2C传输结果写入从设备的发送寄存器,并返回就绪( ready )状态。当桥接器加载发送寄存器时,SPI从设备的传输就绪(trdy )状态寄存器会置位,表明I2C结果可供SPI主控读取且桥接器已准备好处理下一事务。SPI主控可通过trdy 端口引脚中断,或通过SPI总线轮询从设备状态寄存器来接收trdy 信号。

图 4. SPI转I2C状态机

为简化起见,状态图中未显示复位功能。若reset_n 端口被拉低,桥接器将重新初始化,状态机返回就绪( ready ) 状态。

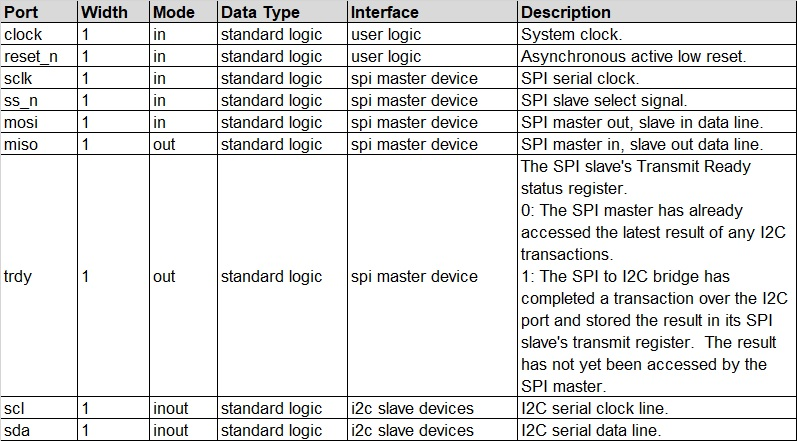

表1描述了SPI转I2C桥接器的端口。

表 1. 端口描述

用户可定义参数

spi_to_i2c_bridge.vhd文件是桥接组件的顶层VHDL封装文件。其实体中定义了四个GENERIC参数,构成组件的用户可定义部分。

sys_clk_frq 参数必须设置为输入系统时钟频率(Hz)。示例代码默认设置为50 MHz(组件仿真与测试频率)。

i2c_scl_frq 参数需设置为I2C串行时钟scl 的目标频率。示例代码中的默认设置为400 kHz,对应I2C规范中的快速模式比特率。

SPI接口的工作模式由参数cpol 和cpha 定义。SPI主设备和SPI至I2C桥接器必须工作在相同模式下才能通信。两个参数的默认值均为‘0’。

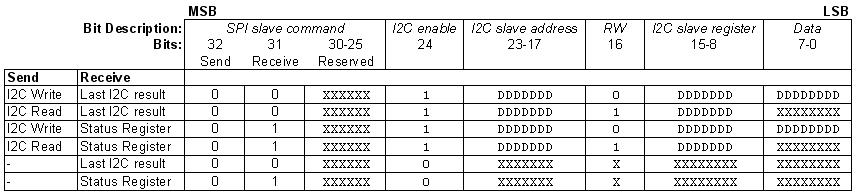

该桥接实现允许SPI主设备读写8位I2C从设备寄存器。桥接器SPI从设备组件与SPI主设备之间的每个事务必须包含一个8位命令,后跟25位数据传输。因此,要执行事务,SPI主设备需向从设备发送如表2所述的33位命令。命令包含8位SPI从设备命令、I2C使能位、7位I2C从设备地址、读/写位、要访问的I2C从设备内部8位寄存器地址,以及要写入I2C从设备的8位数据。命令传输采用最高有效位优先。在8位SPI从设备命令期间,SPI从设备的MISO线保持高阻抗状态,随后在剩余25位期间返回数据。完整时序细节请参阅SPI从设备文档。

表 2. 命令格式

表2同时列出了执行各类操作所需的命令。SPI从设备命令的首位指定了桥接器SPI从设备内部要写入的寄存器。‘0’表示SPI从设备的接收寄存器,桥接器在此接收命令并判断执行操作。若I2C使能位为‘1’,桥接器将执行I2C事务。若为‘0’,桥接器将忽略其余位且不执行总线操作。此选项允许SPI主设备在不发起新I2C事务的情况下读取I2C结果或桥接器状态寄存器。

第二位指定了桥接器SPI从设备内部要返回给SPI主设备的寄存器。‘0’表示SPI从设备的发送寄存器,该寄存器始终保存最后一次I2C事务的结果。‘1’表示SPI从设备的状态寄存器。SPI主设备可读取状态寄存器以轮询trdy的值,该值是返回的首位。

最后的24位指定了请求的I2C事务。如果事务是读取操作,末尾的8位数据将被忽略。

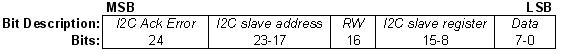

每次I2C事务后,桥接器会将25位结果加载到SPI从设备的发送寄存器中,供SPI主设备读取,如上所述。表3展示了I2C结果的格式。I2C应答错误位指示事务期间是否发生任何I2C从设备应答错误。('1’表示至少发生一次错误,'0’表示无错误。)桥接器在应答错误发生时不会重试事务,因此SPI主设备若需重试通信,必须重新发送命令。7位I2C从设备地址、读/写位及8位I2C从设备寄存器指示了所发送的命令内容。8位数据位在读取命令时返回读取的数据,在写入命令时返回写入的数据。

表 3. I2C结果格式

时钟拉伸

I2C规范第3.1.9节定义了一个可选特性:从设备可通过保持 SCL 低电平来暂停事务。某些从设备设计为在需要更多时间存储接收数据时启用此功能。该I2C主组件兼容支持此特性的从设备。控制I2C主设备的用户无需采取任何操作。

reset_n 输入端口必须保持逻辑高电平,SPI至I2C桥接组件才能工作。该端口的低逻辑电平会异步复位组件。复位期间,miso 、scl 和sda 端口进入高阻态,且trdy 寄存器被清零。

该SPI至I2C桥接器是可编程逻辑组件,允许SPI主设备读写8位I2C从设备寄存器。它支持用户自定义SPI模式、I2C总线频率和系统时钟频率。其遵循NXP I2C规范中单主总线的要求,并整合了时钟拉伸可选特性。

UM10204, I2C-bus specification and user manual, NXP Semiconductors N.V. (1.3 MB)

相关主题

本文转载自:Digikey