随着超高清视频与高帧率显示需求的提升,大带宽视频接口被广泛应用,其中HDMI是使用最广泛的音视频传输接口。AMD FPGA凭借其高性能的逻辑资源和稳定的高速串行接口,可以帮助用户轻松实现HDMI2.1接口的产品部署。本文将以ZCU106开发板为基础,介绍HDMI2.1的硬件和软件实现,并针对常见调试问题给出解决思路。

HDMI2.1接口概述

High-Definition Multimedia Interface(HDMI)是一种传输音视频数据的专用接口。目前最新的版本为HDMI 2.1,最大带宽48Gbps,最大可支持8K30Hz RGB无压缩的数据传输。

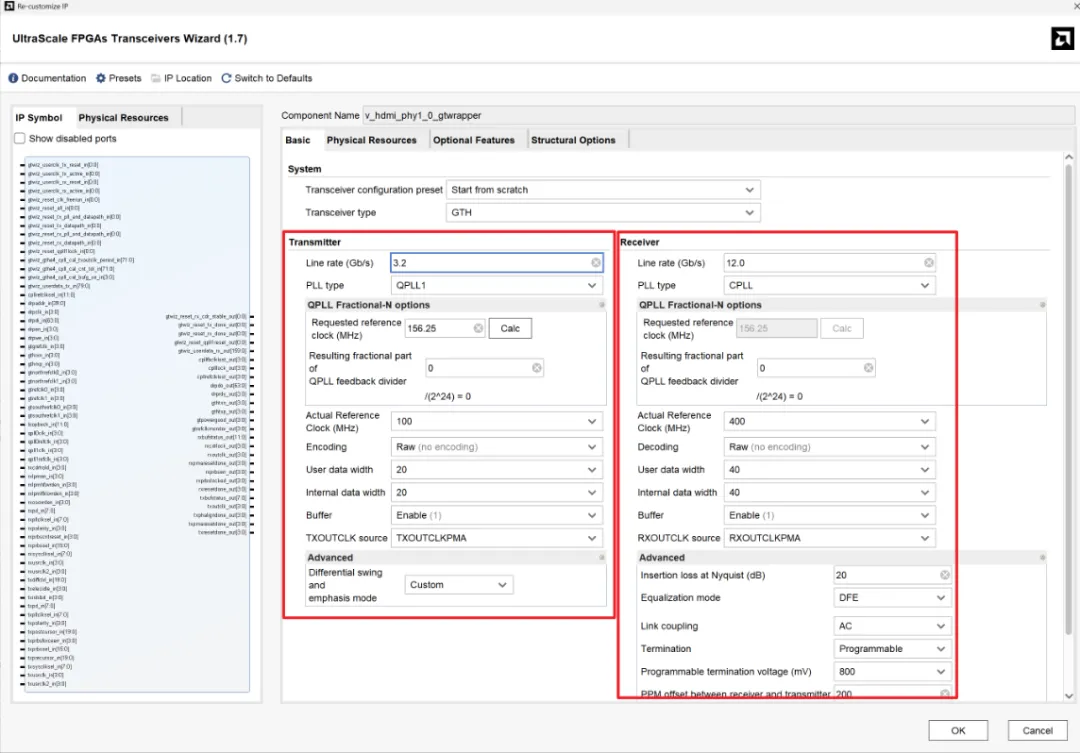

HDMI2.1在兼容HDMI2.0 TMDS传输模式的前提下,新增了FRL模式传输,并且可在TMDS和FRL模式之间任意切换,全方位兼容用户使用需求。

AMD HDMI2.1 IP介绍

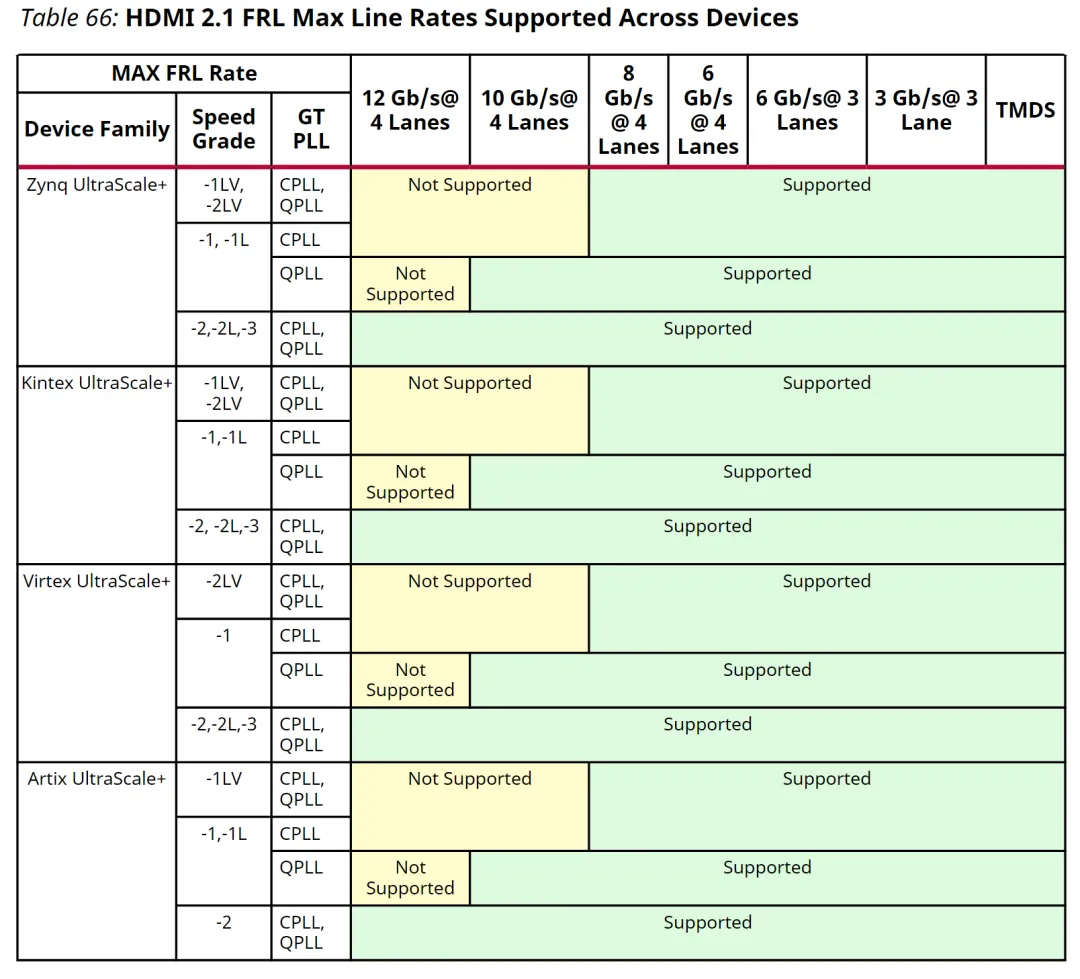

AMD HDMI2.1子系统支持最高12Gb/s@4lanes线速率并向下兼容HDMI2.0协议。子系统还支持可选的HDCP1.4和HDCP2.3加解密功能,并且已经通过CTS认证测试。

AMD HDMI2.1子系统支持16nm和7nm器件,最小器件为AU20P,并且在-1、-1LV、-2LV有速率限制,在选型时需要注意。

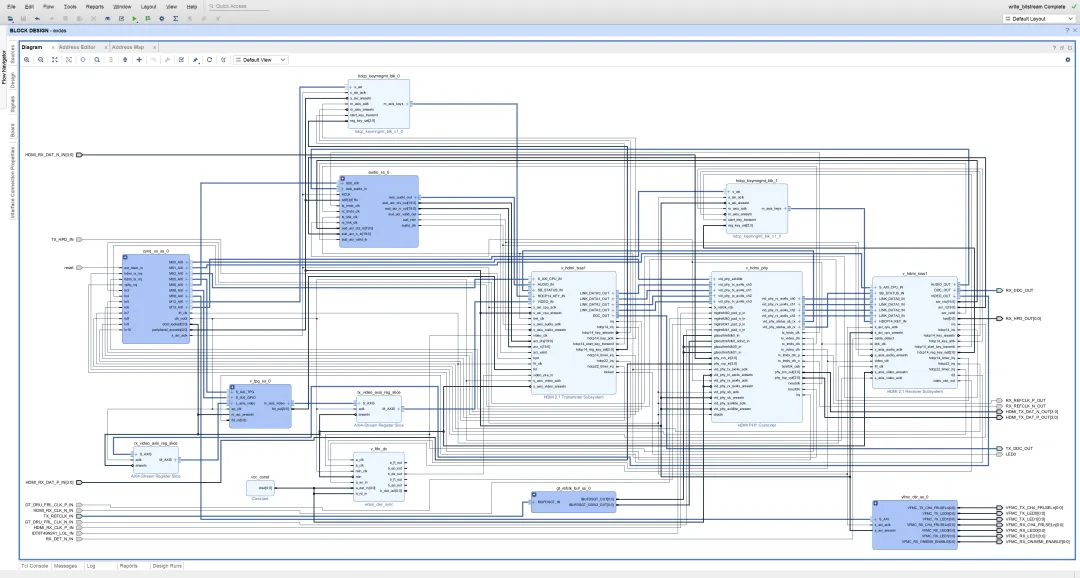

基于AMD FPGA实现的HDMI2.1方案需要两个IP配合使用,分别是HDMI Phy Controller和HDMI2.1 subsystem。下面分别进行介绍。

HDMI Phy Controller:

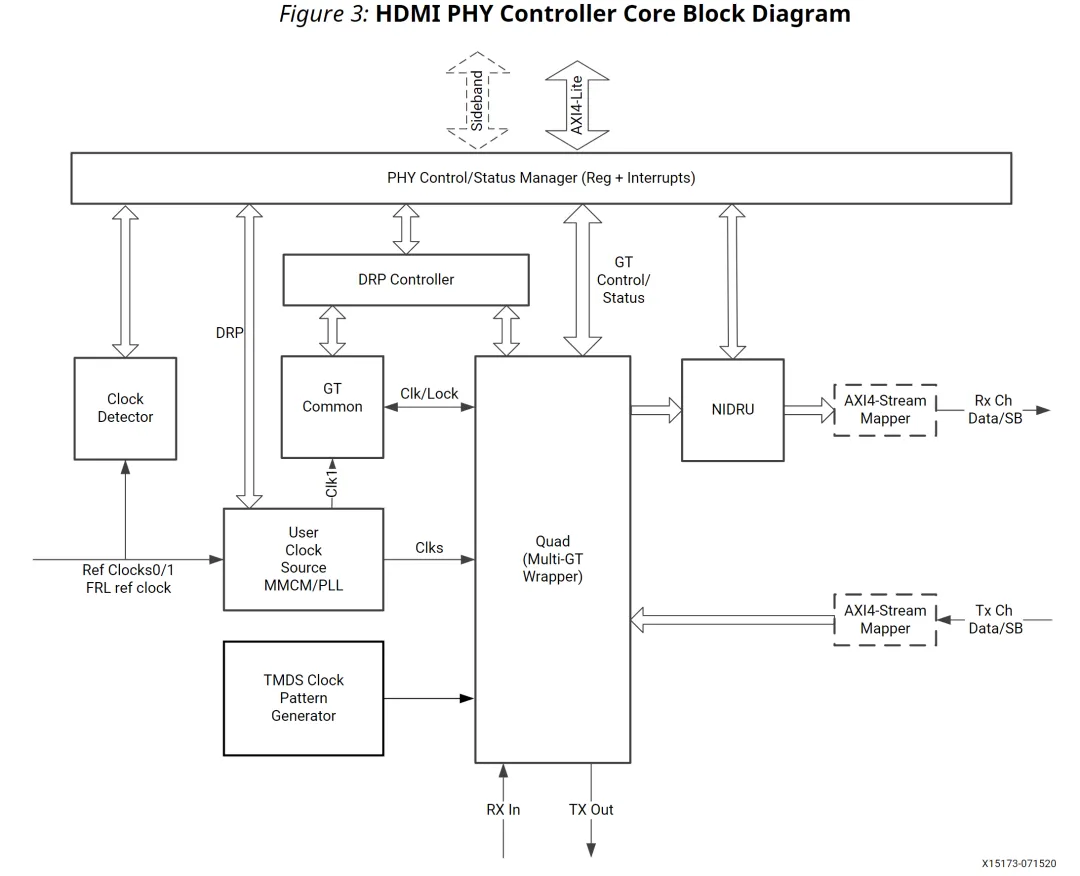

HDMI Phy Controller主要负责高速串行数据的物理层收发,包括TMDS或FRL模式下的数据编解码、时钟恢复、电气均衡等,简化串行收发器的使用。

接口介绍:

HDMI PHY Controller由多个子模块组成,如下图所示。

PHY Control/Status Manager模块实现软核对IP的寄存器和中断控制,所有模块的状态和控制信号均由该模块通过axi-lite总线与CPU或软核通信。

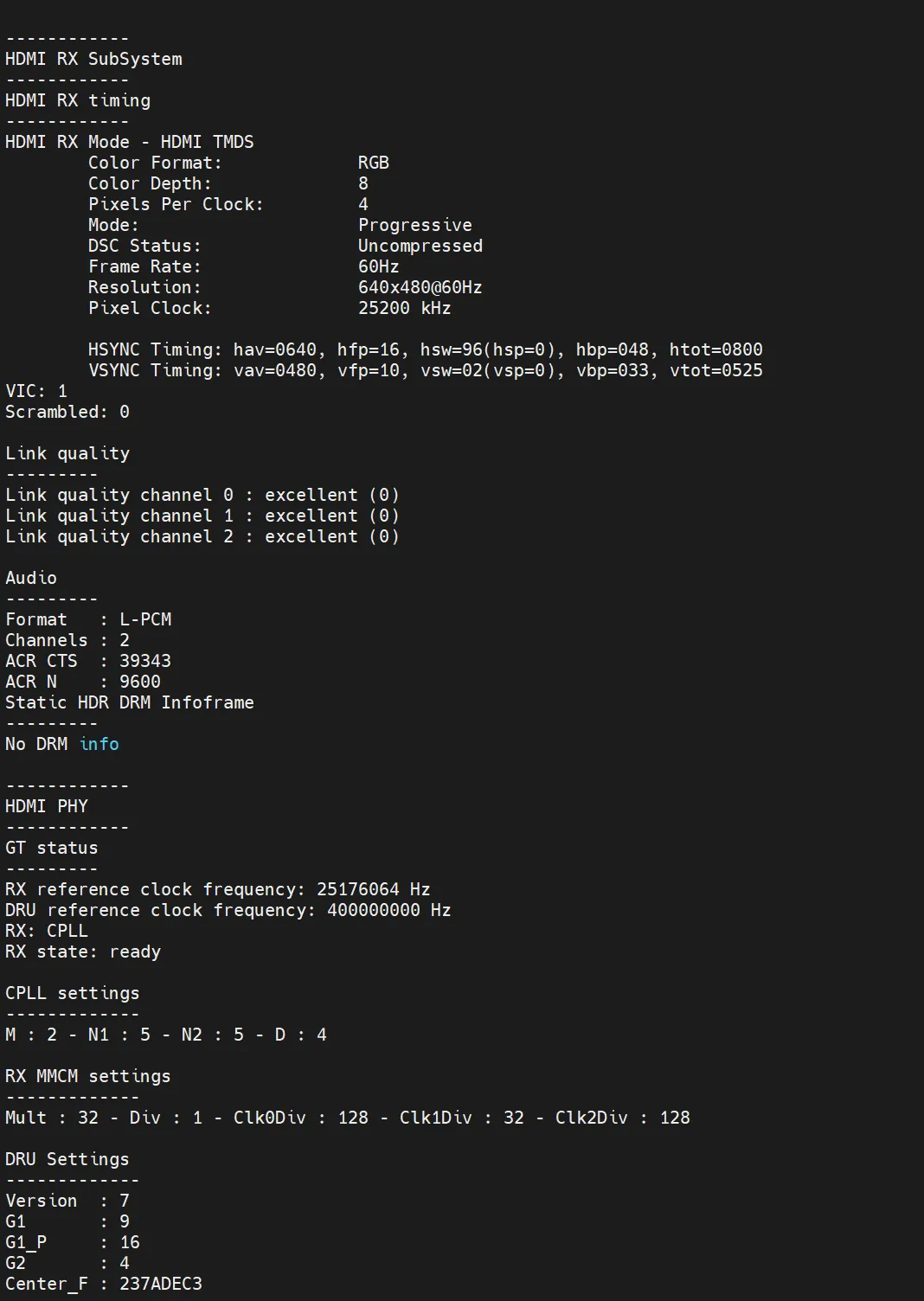

NI-DRU用于支持较低线速率的应用,如TMDS模式下的640x480@60Hz分辨率,线速率时钟为25MHz,该时钟通过GTREFCLK管脚接入QPLL或CPLL,但时钟频率小于QPLL(61.25MHz)和CPLL(50MHz)的最小工作频率,此时通过NI-DRU功能仍然可以正常恢复出视频数据。

User Clock Source模块负责管理HDMI子系统的时钟资源,例如HDMI2.1 RX子系统需要三个时钟输入到FPGA内部,分别是TMDS模式下的随路时钟、FRL模式下的参考时钟以及NI-DRU时钟。

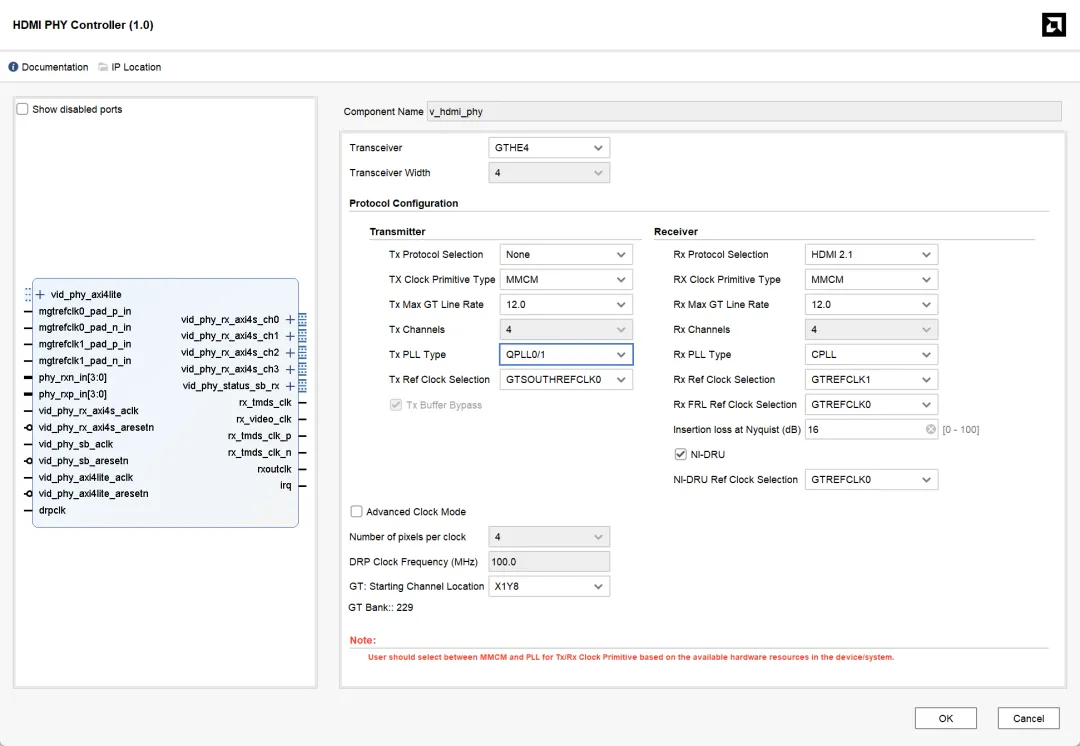

IP配置:

以HDMI2.1-RX为例,协议选择HDMI2.1,最大线速率为12Gbps,时钟模块建议选择MMCM,这样可以很好的支持小数时钟频率。RX子系统需要三个外部输入的时钟:

Rx Ref clock selection:TMDS模式下的随路时钟,时钟频率跟随分辨率变化;

FRL Ref clock selection:FRL模式下参考时钟,-2器件频率为400MHz,-1器件频率为200MHz;

NI-DRU Ref clock Selection:提供给DRU模块的时钟,以恢复低线速率视频数据,可以与FRL参考时钟共用一个;

所有提供给GT的参考时钟的抖动要求不超过±100PPM,ni-dru参考时钟频率误差不能超过±10 kHz。

HDMI2.1 Subsystem

HDMI2.1 Subsystem主要负责从PHY层捕获HDMI流,从HDMI流中解析数据并转换为视频和音频流。

接口介绍:

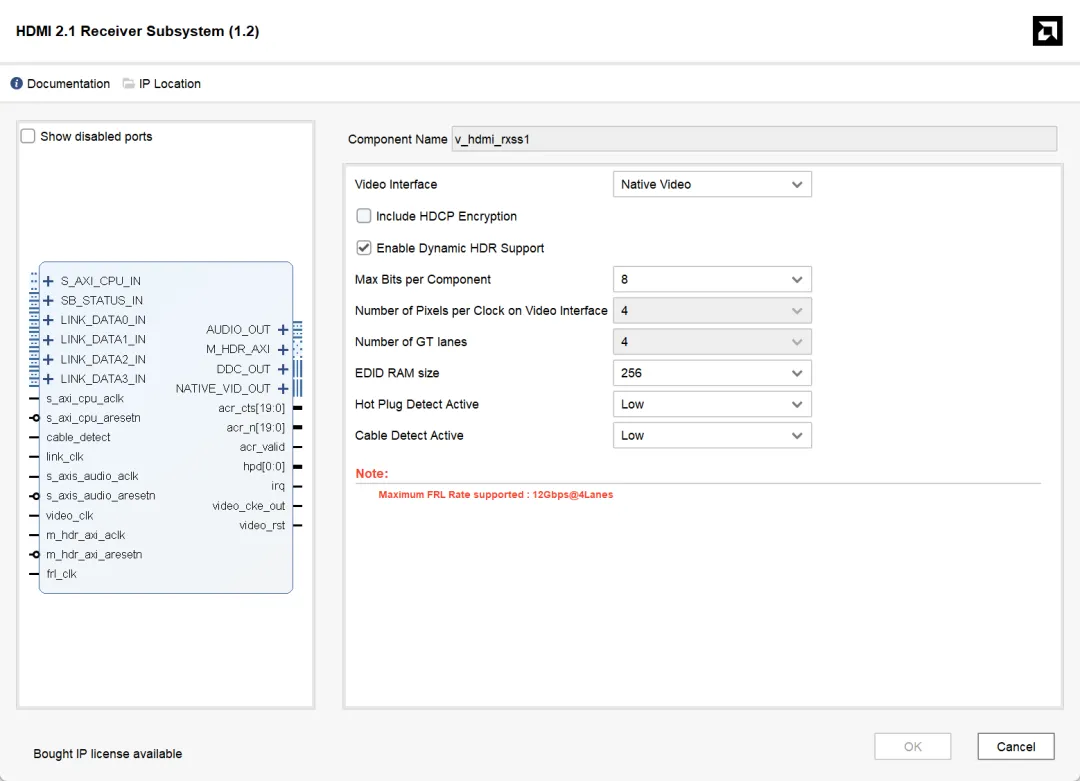

HDMI子系统主要为三部分组成,如下图所示。HDMI Receiver Core主要功能为负责HPD握手、解析音频、视频流和HDR数据,AXI-lite接口负责与软核进行寄存器和中断通信,HDCP为可选功能,实现HDCP1.4和HDCP2.3加解密功能。

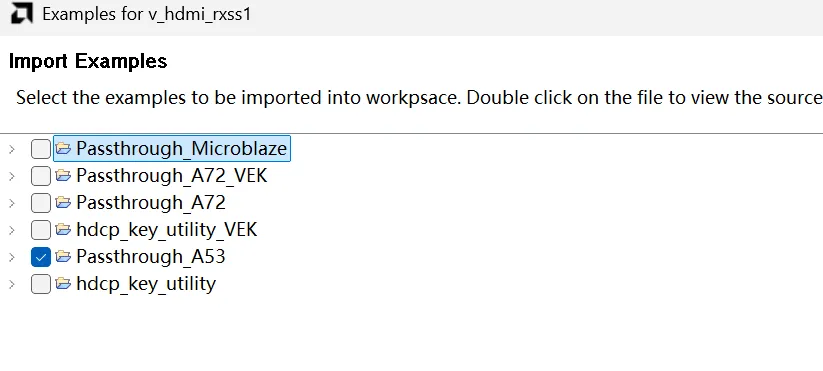

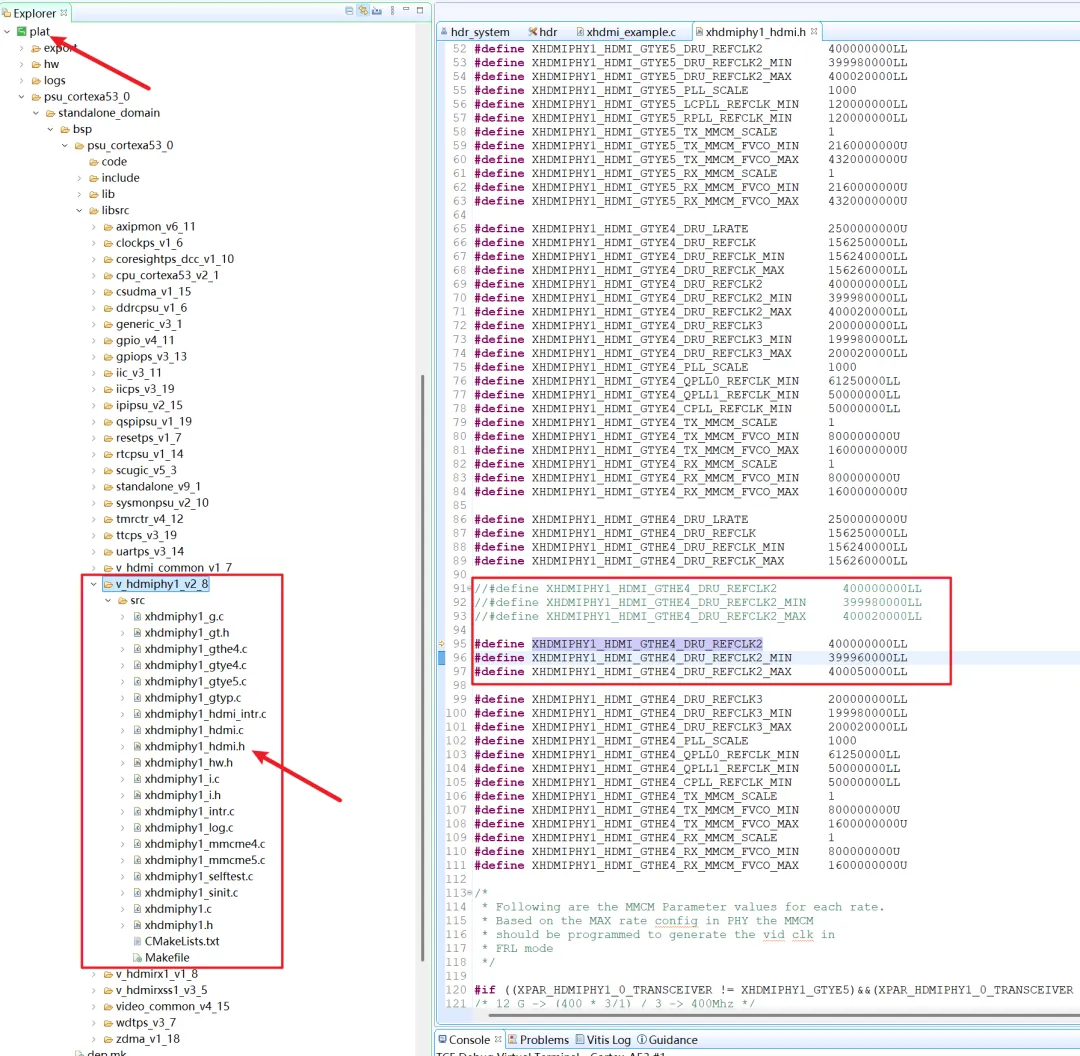

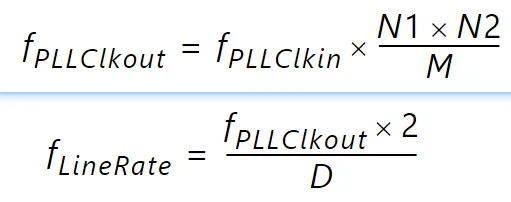

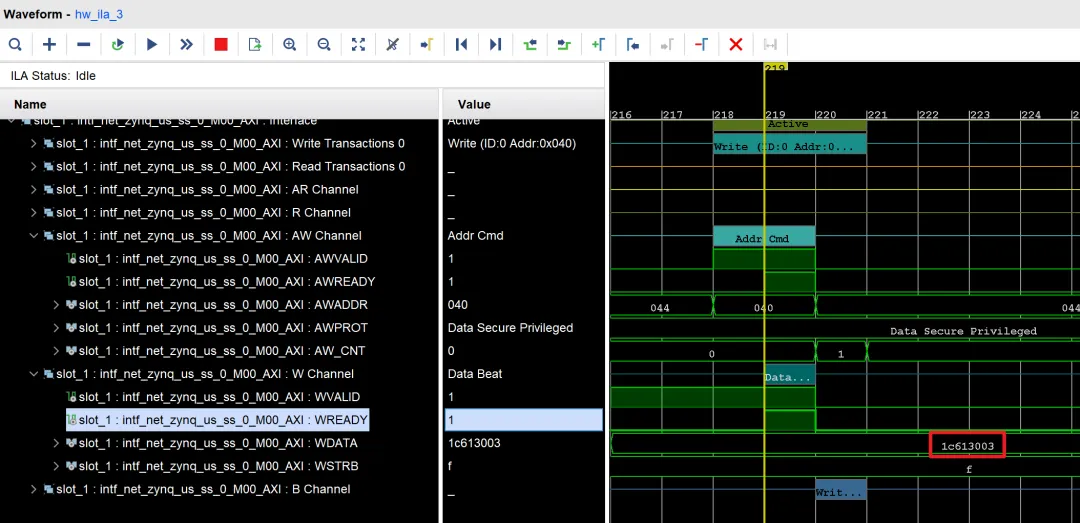

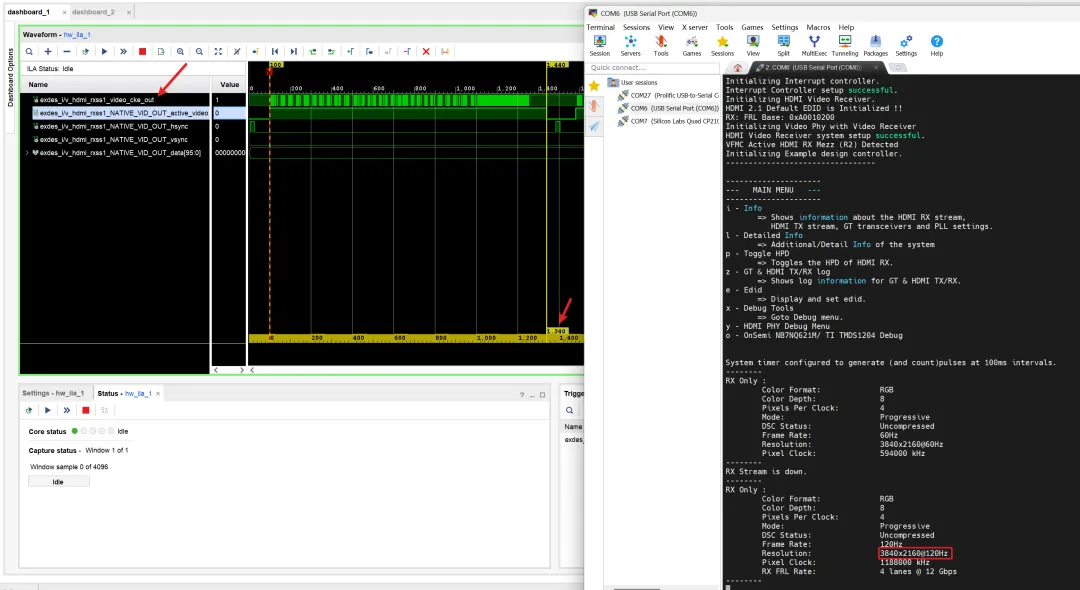

IP配置: IP提供了axi-stream和native video接口供用户内部逻辑使用。 当使用axis-stream接口时,用户需要外部提供s_axis_video_clk,时钟频率要求s_axis_video_clk >= HActive*Vactive*Frame Rate/PPC。 当使用native video接口时,PPC固定为4,视频数据时钟域为video_clk,该时钟来自hdmi phy controller。Tmds模式下,该时钟为像素时钟,频率与分辨率成比例,如3840x2160@60Hz时,该时钟为4400*2250*60/4=148.5MHz;在FRL模式下,该时钟为固定的400MHz。 Frl_clk为固定的450MHz,可以使用内部mmcm或pll产生,供给IP使用。 参考设计 硬件设计: 实现HDMI2.1接口需要GT外部添加适当的EQ或retimer以满足HDMI电气特性。AMD官方推荐使用安森美NB7NQ621M或TI TMDS1204。 对于HDMI-RX接口,第四条lane在tmds模式下传输的是随路时钟,在frl模式下传输数据,因此需要将第四lane同时接入GT Refclk管脚和GT RX管脚。推荐器件:FUSB340TMX实现1分2功能。 软件设计: 以ZCU106开发板为例,AMD提供了带有HDCP功能的HDMI-RX和HDMI-TX passthrough例程: Vivado工程: Vitis工程: 常见问题及调试方法 1. 使能NI-DRU功能后,显卡推小分辨率无法lock,dru时钟显示为1Hz: 出现此问题是因为提供给dru模块的参考时钟误差超过了±10kHz,可以考虑更换精度更高的晶振,也可以修改软件中的时钟检测参数暂时解决,方法如下: 将原来的最大最小值范围扩到可以覆盖板上晶振的输出频率,此时dru模块会恢复正常。 如下图所示为NI-DRU功能正常运行时的打印信息: 当检测到输入当前分辨率随路时钟小于CPLL最低限制(50MHz)时,DRU功能自动使能,并开始计算CPLL、MMCM的分频系数: CPLL: fPLLClkin=400MHz,此时计算出线速率时钟为2500MHz,即在2.5Gbps的线速率下对低速数据进行过采样。使用ila抓取GTH配置寄存器0x0003,配置数据为0x1C61,其中bit8-5为RX_DATA_WIDTH,这里对应值为3,即RX_DATA_WIDTH=20bit,此时rxoutclk=2500/20=125MHz。 2. 选择native video接口时,ppc固定为4,tmds模式下video_de的宽度为Hactive/4,如下图: 当分辨率为FRL速率时,video_de信号并不是Hactive/4,此时需要配合video_cke_out使用,当video_de和video_cke_out同时为高电平时,此时对应的video_data为有效像素点: 3. HDMI PHY Controller可以放在Block Design外面例化,此时可以通过修改GT_wizard以实现同一个GT Quad的RX运行HDMI2.1,TX实现其它协议的功能或TX运行HDMI2.1,RX运行其它协议: 参考资料 文章来源:安富利