Alchitry Au FPGA 是一款性能出色的开发板,搭载 赛灵思 Artix 7 XC7A35T-1C FPGA,拥有超 33000 个逻辑单元与 256MB 的 DDR3 随机存取存储器,且该款 FPGA 可提供不同速度等级、温度范围和工作电压的选型。

Alchitry Au FPGA 开发板配备复位按键、Done 指示灯,核心参数及外设配置如下:总计 102 个输入 / 输出引脚,默认采用 3.3V 逻辑电平,其中 20 个引脚可切换为 1.8V 逻辑电平;9 路差分模拟输入通道;8 个通用发光二极管(LED);板载 100MHz 时钟,可通过 FPGA 内部逻辑进行灵活配置;一个 USB-C 接口,兼具开发板配置与供电功能;还有一套 USB 转串行接口,用于数据传输。所有 Alchitry 系列开发板均全面支持 Lucid 硬件描述语言(HDL)。

通过搭载名为 “元件扩展板(Elements)” 的可堆叠扩展板(类 Arduino 扩展板或树莓派 HAT 扩展板),Alchitry Au FPGA 可拓展自身的输入 / 输出硬件能力,还能增加原型开发区域、按键、发光二极管等外设。

本次演示所使用的 Lucid 硬件描述语言代码如下:

module blinker (

input clk, // clock

input rst, // reset

output blink // output to LED

) {

dff counter[26](.clk(clk), .rst(rst))

always {

blink = counter.q[25]

counter.d = counter.q + 1

}

}

上述代码被集成在 alchitry_top 顶层模块中,顶层模块代码如下:

module alchitry_top (

input clk, // 100MHz clock

input rst_n, // reset button (active low)

output led[8], // 8 user controllable LEDs

input usb_rx, // USB->Serial input

output usb_tx // USB->Serial output

) {

sig rst // reset signal

.clk(clk) {

// The reset conditioner is used to synchronize the reset signal to the FPGA

// clock. This ensures the entire FPGA comes out of reset at the same time.

reset_conditioner reset_cond

.rst(rst) {

blinker my_blinker

}

}

always {

reset_cond.in = ~rst_n // input raw inverted reset signal

rst = reset_cond.out // conditioned reset

led = 8x{my_blinker.blink} // blink LEDs

usb_tx = usb_rx // echo the serial data

}

}

同时搭配对应的 alchitry.acf 配置文件,代码如下:

STANDARD(LVCMOS33), SIDE(TOP) {

pin clk CLOCK FREQUENCY(100MHz)

pin rst_n RESET

pin led[0] LED0

pin led[1] LED1

pin led[2] LED2

pin led[3] LED3

pin led[4] LED4

pin led[5] LED5

pin led[6] LED6

pin led[7] LED7

pin usb_rx USB_RX

pin usb_tx USB_TX

}

上述 Lucid 硬件描述语言代码可实现 Alchitry Au FPGA 主开发板上所有 LED 的闪烁功能,本次演示的开发与程序烧录均通过 Alchitry 集成开发环境(IDE)完成,相关演示效果可参考配套视频。

本演示还实现了 USB 串行终端的数据回显功能,核心代码为:

usb_tx = usb_rx // echo the serial data

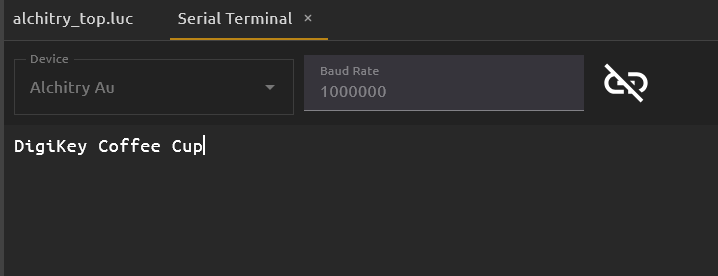

在串行终端的实际测试中,主机发送的字符会实时回显给用户,测试界面显示设备为 Alchitry Au,波特率为 1000000,输入字符后终端会即时反馈。

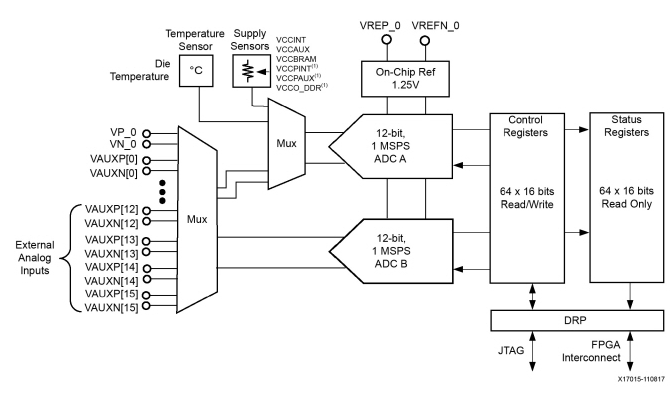

Alchitry Au 搭载的 FPGA 内置 12 位、1 兆采样率(MSPS)的模数转换器(ADC),并引出 9 路差分输入通道,其中 8 路与数字输入 / 输出引脚复用,1 路为专用差分输入通道。下图为赛灵思 Artix 7 XC7A35T-1C FPGA 的片内 ADC 结构框图,包含片上温度传感器、各类电源供电接口(VCCBRAM、VCCPINT 等)、1.25V 片内参考源、多路模拟输入通道(VAUXP/VAUXN)、两路 12 位 1MSPS 的 ADC 模块、读写寄存器及 JTAG 互联接口等核心单元。

Alchitry Au 的 FPGA 本身已配备充足的片内存储器,同时该 FPGA 集成了存储器控制器,外接 256MB 的 DDR3 随机存取存储器,可提供额外的存储拓展能力。Alchitry Au FPGA 是一款小尺寸、高性能的开发板,适用于多种应用场景,其搭载的赛灵思 Artix 7 XC7A35T-1C FPGA 可在 DigiKey 平台采购。

文章来源:DigiKey