揭秘AI推理硬件的五大系统性问题与FPGA解决方案

系列回顾:上篇文章我们介绍了 Llama 3.1 8B 在 Achronix FPGA 上的低延迟方案。最近,一篇《初创公司硬刚英伟达,FPGA要掀翻GPU!成本爆砍50倍、功耗大降80%!》的文章在朋友圈刷屏。今天我们用技术视角深度解读:为什么FPGA能做到这些?GPU在LLM推理上遇到了哪些系统性问题?

“当我们用3年前设计的硬件运行今天的AI模型,困局就已经注定。”

当下的AI硬件行业依然受困于“暴力堆料”的思维定势。面对大模型(LLM)复杂度的指数级增长,大多数厂商的回应仅仅是:更大的HBM带宽、更大的硅片面积。然而,每Token成本依然居高不下,甚至成为AI普惠的最大障碍。

这是一个系统性的错配:LLM算法正在以周为单位快速迭代,而支撑它们的GPU和ASIC芯片却被锁定在3到5年的硬件开发周期中。这种滞后导致了所谓的“硬件彩票”——无数优秀的算法优化方案被束之高阁,仅仅因为几年前设计的硬件没有为其预留通路。

问题不在于芯片不够大,而在于不够灵活。

为什么 FPGA 是 LLM 推理的破局者?

以下五大理由,揭示了为什么可编程逻辑(FPGA)正在成为AI推理的“甜蜜点”:

GPU的通用化陷阱

现代GPU虽然强大,但它们的“通用性”在LLM推理场景下变成了累赘。GPU设计之初是为了兼顾科学计算、视频渲染和AI训练等海量任务。

然而,推理(Inference)与训练(Training)有着本质区别:推理是一个序列化、内存受限的过程,而非大规模并行计算任务。这就导致了“暗硅(Dark Silicon)”问题:

算力浪费:GPU芯片上大量用于训练梯度计算的逻辑单元在推理时处于闲置状态。

极低利用率:数据中心实测显示,H100在运行LLM推理任务时,计算利用率往往低于10%。

高昂代价:企业支付了100%的硅片成本和功耗,却只利用了不到10%的价值。

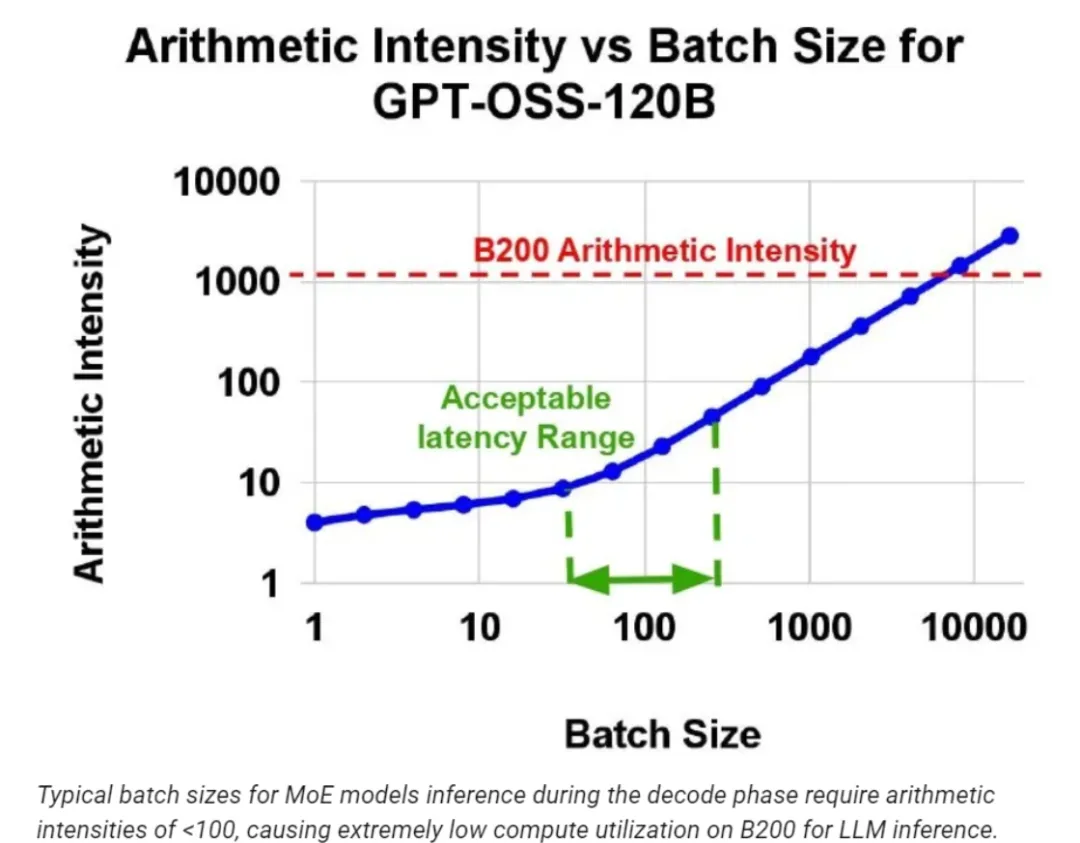

图1:GPT-OSS-120B的算术强度与批量大小关系

典型的MoE模型推理在decode阶段需要的算术强度远低于100,导致B200在LLM推理时计算利用率极低

FPGA方案打破了这一僵局。通过软件定义硬件,FPGA可以为特定模型生成1:1镜像的处理器设计,仅实例化实际需要的逻辑,彻底消除“暗硅”浪费。

内存带宽与成本墙

LLM推理本质上是一个内存受限(Memory-bound)问题。在Decode阶段,每生成1个Token,处理器就需要从内存中加载整个模型的权重。无论计算核心的标称算力有多高,如果数据喂得不够快,核心只能空转。

为了应对这一挑战,GPU厂商不得不堆叠极其昂贵的HBM(高带宽内存)和SRAM。HBM的成本约是DRAM的10倍,而SRAM更是高达10,000倍。随着长上下文窗口的需求增加,这一成本矛盾愈发尖锐。

FPGA的突破在于:高端FPGA能够提供与NVIDIA B200相当的有效内存带宽,但资本支出(CapEx)仅约为其1/3。通过更高效的内存控制器设计,FPGA能以更低的成本榨干标准内存资源的性能。

原生支持新优化技术

算法的进步远快于硬件。Apple、Microsoft和Google的研究团队都曾呼吁:新的模型压缩技术(如低比特量化、1-bit LLM)在现有GPU上缺乏硬件支持,无法发挥潜力。

以NVIDIA从Hopper(H200)到Blackwell(B200)的跨越为例,其性能提升的关键之一是加入了对FP4(4-bit浮点)的原生支持。这是一个数年前就已经出现的优化技术,却要等到数年后的新一代芯片才能硬件化。

根据 InferenceX by SemiAnalysis 的数据(截至2026年2月24日),以 DeepSeek-R1 模型为例,在交互率为 41.6 tokens/s/user 的场景下,硬件原生支持量化的影响如下:

这个阶跃式的成本效率提升,仅仅来自于将一个数年前就存在的ML优化技术原生集成到硬件中。从 $3.75 降至 $0.167,总降幅高达 95.5%!

FPGA优势:你不需要等待下一代芯片。当新的优化算法(如BitNet b1.58)出现时,FPGA只需一次软件更新,就能在数日内实现硬件级的原生支持,而非数年。这意味着你可以立即享受类似从 H200 到 B200 4-bit 的成本跃升,而无需等待硬件更新周期。

FPGA不再只是原型工具

如果你对FPGA的印象还停留在“需要数月VHDL编程的逻辑门阵列”,那你可能这就out了。

现代服务器级FPGA(如Achronix Speedster7t)已经发生了质变:

硬核计算单元:内置类Tensor-core的点积运算块,采用5nm/7nm先进制程。

高速内存子系统:原生支持HBM2E、GDDR6,提供极高带宽。

高速互连:原生集成PCIe Gen5和800GbE以太网。

弹性架构:支持分钟级动态重构,适应不同负载。

这已经不是原型验证工具,而是生产级的计算引擎。

开发复杂性已被解决

过去,使用FPGA意味着需要一支专业的硬件工程师团队和数月的开发周期。现在,这一壁垒已被打破。

新一代的自动化ML/HW/SW协同设计栈充当了“编译器”的角色。它可以将标准的PyTorch/TensorFlow模型直接编译为优化的FPGA比特流。对于ML研究人员来说,硬件细节完全透明,开发体验与使用GPU无异。

真实案例:ElastixAI + Achronix 联合方案

ElastixAI 是一家由前Apple和Meta的机器学习研究人员创立的AI芯片公司,于2026年2月正式从隐身模式中现身,并获得1800万美元种子轮融资。他们坚定选择了 Achronix Speedster7t FPGA 作为其硬件平台。

ElastixAI 官方发布的数据令人瞩目(2026年2月):

相比 NVIDIA B200 GPU,TCO(总体拥有成本)最高降低 50 倍

功耗降低 80%

提供 NVIDIA 插件的无缝替代后端,开发团队无需修改一行底层硬件代码

这一惊人的效率提升,正是通过“消除暗硅”实现的:在FPGA上仅激活推理所需的电路,并通过硬件-软件协同设计将算力利用率推向极致。ElastixAI 的自动化 ML/HW/SW 协同设计栈充当了“编译器”的角色,将标准模型直接转换为优化的 FPGA 比特流。

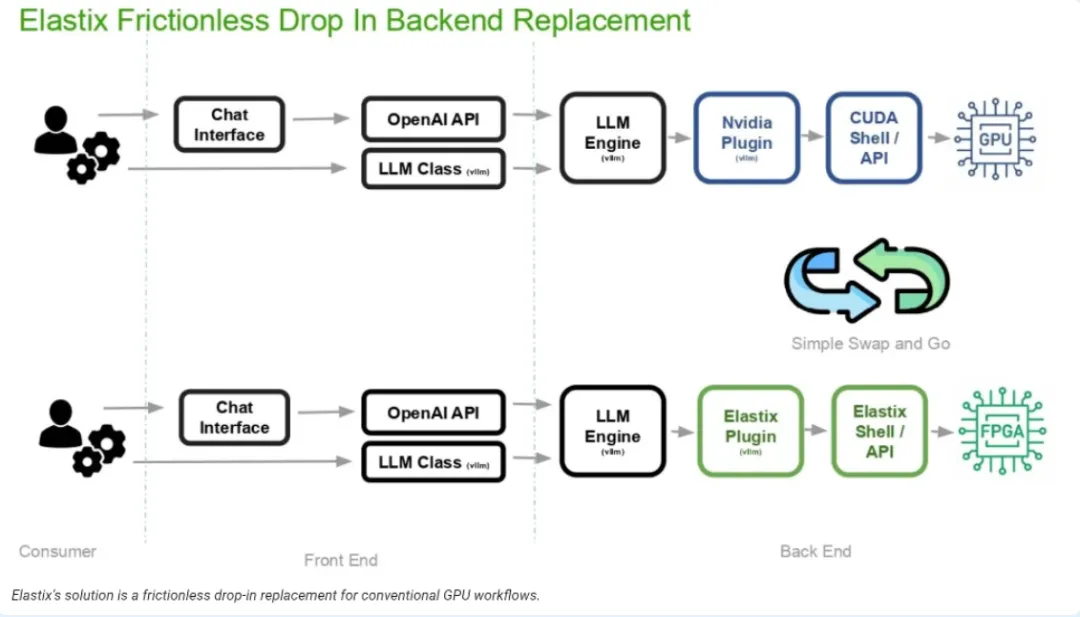

图2:ElastixAI 无缝替换 NVIDIA 后端架构

上半部分为传统 NVIDIA GPU 工作流,下半部分为 ElastixAI FPGA 方案。

仅需简单替换插件(绿色框),即可从 GPU 切换到 FPGA,前端工作流保持不变

这种“即插即用”的方式彻底消除了 FPGA 的使用门槛——对于应用开发者来说,从 GPU 迁移到 FPGA,就像更换一个软件插件一样简单。这是 FPGA 在 AI 推理领域实现规模化应用的关键突破。

行业趋势:弹性未来

推理芯片不应该在算法稳定之前就被固化——而算法的稳定可能还需要数年时间。

如果你两年前购买了大量的H100,你现在可能正苦恼于它无法高效运行最新的量化模型。但如果那些卡是FPGA,你就不需要购买Blackwell来升级硬件。你只需要下载一个软件更新,你的硬件就会摇身一变,成为针对最新模型优化的专用加速器。

这就是FPGA带给AI时代的价值:告别“硬件彩票”,让开发者自由创新。

文章来源:Achronix