作者:Warren Huang,文章来源:FPGA FAE技术分享选集

做FPGA开发的朋友,想必都踩过仿真环境的坑:要么软件版本不兼容,要么仿真库编译报错,要么Vivado调用第三方仿真器直接卡死,明明是很基础的环境搭建,却能耗掉大半天的开发时间。

今天这篇文章,就给大家把Vivado+ModelSim/QuestaSim仿真环境的全流程讲透,从软件下载、版本选择,到库编译、环境配置,再到 Windows系统卡死的专属解决方案,一站式解决你的仿真环境搭建难题,新手照着做也能一次成功。

一、前期准备:软件安装包下载与版本选择

工欲善其事,必先利其器。仿真环境搭建的第一步,就是选对软件版本、拿到靠谱的安装包,避免后续出现兼容性问题。

1. Vivado 设计套件

Vivado 是 AMD Xilinx FPGA 开发的核心工具,我们先给大家整理了官方渠道和稳定的网盘下载渠道,大家可根据需求选择对应版本。

官方版本介绍:

https://www.amd.com/en/products/software/adaptive-socs-and-fpgas/vivado/vivado-whats-new.html

官方下载地址:

安装步骤参考:官方权威安装指南《Vivado Design Suite 用户指南:版本说明、安装和许可 (UG973)》,跟着官方步骤走,能规避 90% 的安装报错。

2. ModelSim/QuestaSim 仿真器

很多新手会分不清ModelSim 各个版本的区别,也搞不懂 QuestaSim 和 ModelSim 的关系,这里先给大家讲透,再给下载和选型建议。

首先,QuestaSim是Siemens EDA(原 Mentor Graphics)的企业级高级验证平台,属于ModelSim-SE 的全功能增强版,完全兼容 ModelSim-SE 的所有功能和项目文件,ModelSim 仿真可以无缝迁移到 QuestaSim 中,也是目前行业内主流使用的版本。而 ModelSim 本身分为 SE(标准版)、DE(开发者版)、PE(个人版)三个核心版本,功能差异巨大,核心对比如下:

功能维度 | ModelSim SE | ModelSim DE | ModelSim PE |

浮动许可支持 | 是 | 是 | 可选 |

ASIC 签核支持 | 是 | 是 | 不支持 |

32/64 位跨平台兼容 | 是 | 不支持 | 不支持 |

Verilog/VHDL 混合仿真 | 可选 | 可选 | 可选 |

代码覆盖率分析 | 是 | 不支持 | 不支持 |

波形编辑与对比 | 是 | 不支持 | 不支持 |

64 位系统支持 | X86-64 Linux、Itanium-2 Linux | 不支持 | 不支持 |

简单总结:SE 版本是 ModelSim 原生版本里功能最完善、性能最强的版本,而集成在 Altera、Xilinx、Lattice 等FPGA厂商工具里的,均为OEM版(比如给Xilinx 的 XE 版、给 Altera 的 AE 版)。

OEM 版本虽然自带对应厂商的库文件,无需手动编译,但仿真速度、功能支持都远不如SE 版本,且不支持checkpoint功能,无法收集覆盖率等限制。比如 ModelSim XE 就不支持 SystemVerilog,且从 13.1 版本开始就不再更新维护,长期开发优先选择 ModelSim SE 或 QuestaSim。

Feature | ModelSim SE | ModelSim DE | ModelSim PE |

Licensing-Floating License | yes | yes | option |

Language Neutral License | option | option | option |

ASIC Sign-Off | yes | yes | — |

32/64-Bit Cross-Compatibility | yes | — | — |

VHDL | option | option | option |

Mixed Language | option | option | option |

Analog/Mixed Signal (Advance MS Product) | option | — | — |

VHDL FLI | yes | — | — |

Waveform Editor | yes | — | — |

Dataflow Window | yes | — | — |

Source Annotation | yes | — | — |

C Debugger | yes | yes | — |

Multiple Waveform Windows | yes | yes | — |

Waveform Compare | yes | — | — |

JobSpy | yes | yes | — |

User-Customizable GUI (via Tk) | yes | — | — |

Code Coverage (with Toggle Coverage) | yes | — | — |

Coverage Viewer | yes | — | — |

Verilog RTL & Gate | yes | — | — |

Performance Optimizations | yes | — | — |

VHDL RTL & VITAL | yes | — | — |

Performance Optimizations | yes | — | — |

Performance and Memory Profiler | yes | yes | option |

Separate Elaboration | yes | — | — |

Integrated Sim Farm Support (via JobSpy) | yes | — | — |

Checkpoint & Restore | yes | — | — |

SWIFT Interface / SmartModels | yes | — | — |

Synopsys Hardware Modeler Support | yes | — | — |

32-Bit OS Support | HP-UX, Linux, Solaris, Windows platform | Linux | Windows platform |

64-Bit OS Support | X86-64 and Itanium-2 Linux | — | — |

注:“yes” 表示该版本支持此功能;“option” 表示该功能为可选组件;“—” 表示该版本不支持此功能。

二、核心配置:Vivado中 ModelSim-SE/QuestaSim 仿真环境搭建

使用 Vivado 开发的工程,会大量调用软件自带的 IP 核,如果想要用 ModelSim/QuestaSim 正常仿真,核心就是提前编译好 Xilinx 的仿真库,完成软件之间的配置联动,下面分4步,给大家讲清每一个操作细节。

步骤 1:Vivado 预编译仿真库

这是整个配置流程的基础,只有编译好对应仿真器的库文件,后续仿真才能正常识别 Vivado 的 IP 核。

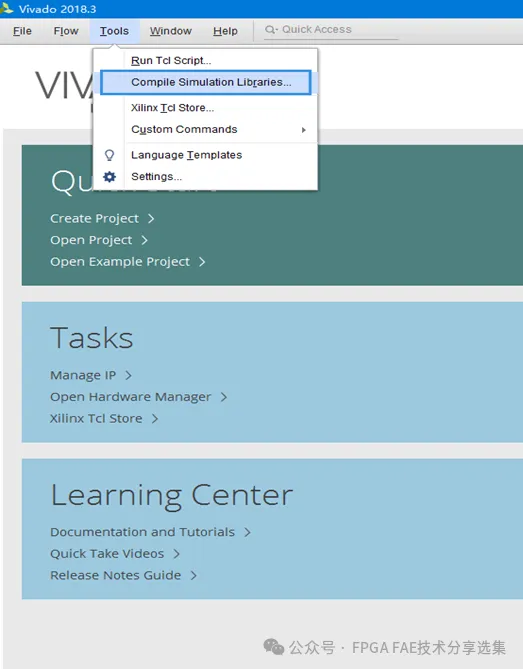

1.双击打开Vivado 软件,无需新建 / 打开工程,直接点击顶部菜单栏Tools → Compile Simulation Libraries,打开库编译配置窗口。

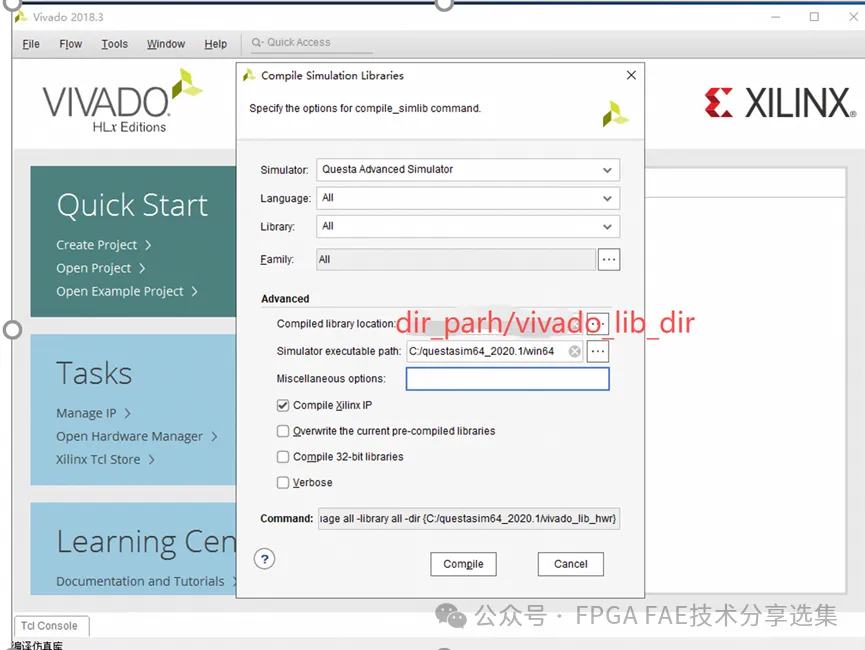

2.在配置窗口中,按以下规则填写参数,也可以直接使用下方的 Tcl 命令执行:

Simulator:选择你安装的仿真器(Questa/ModelSim)

Language:选择 all,覆盖Verilog 和 VHDL 双语言

Library:选择 all,包含unsim(功能仿真)、simprim(时序仿真)全库

Family:勾选 all,兼容全系列FPGA 器件

编译库存放位置:自定义一个无中文、无空格的路径,比如dir_path/vivado_lib_dir

Simulator executable path:选择仿真器安装路径下的win64 文件夹,比如C:/questasim64_2020.1/win64

完整 Tcl 命令参考:

compile_simlib -simulator questa -simulator_exec_path {C:/questasim64_2020.1/win64} -family all -language all -library all -dir {dir_path/vivado_lib_dir}

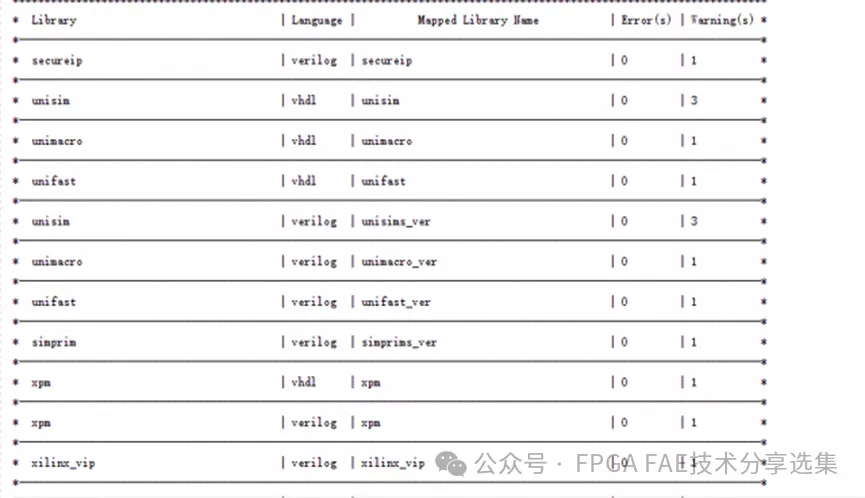

3.配置完成后点击 Compile,等待编译完成。最终结果 0个Error即为编译成功,Warning不影响后续使用,同时可以去自定义的库路径下,查看是否生成了对应的库文件夹,确认编译生效。

步骤 2:配置 modelsim.ini 文件

modelsim.ini 是仿真器的核心配置文件,作用是定义仿真过程中调用的库文件路径,是联动Vivado 和仿真器的关键。

1.打开步骤 1 中编译好的库文件夹,找到“dir_path/vivado_lib_dir”/modelsim.ini,用记事本 / 代码编辑器打开。

secureip = dir_path/vivado_lib_dir/secureip unisim = dir_path/vivado_lib_dir/unisim unimacro = dir_path/vivado_lib_dir/unimacro unifast = dir_path/vivado_lib_dir/unifast unisms_ver = dir_path/vivado_lib_dir/unisms_ver unimacro_ver = dir_path/vivado_lib_dir/unimacro_ver unifast_ver = dir_path/vivado_lib_dir/unifast_ver simprims_ver = dir_path/vivado_lib_dir/simprims_ver xpm = dir_path/vivado_lib_dir/xpm xilinx_vip = dir_path/vivado_lib_dir/xilinx_vip ahblite_axi_bridge_v3_0_13 = dir_path/vivado_lib_dir/ahblite_axi_bridge_v3_0_13 audio_clock_recovery_v1_0 = dir_path/vivado_lib_dir/audio_clock_recovery_v1_0 audio_tpg_v1_0_0 = dir_path/vivado_lib_dir/audio_tpg_v1_0_0 av_pat_gen_v1_0_0 = dir_path/vivado_lib_dir/av_pat_gen_v1_0_0 axis_infrastructure_v1_1_0 = dir_path/vivado_lib_dir/axis_infrastructure_v1_1_0 axis_protocol_checker_v2_0_2 = dir_path/vivado_lib_dir/axis_protocol_checker_v2_0_2 axi_ahblite_bridge_v3_0_15 = dir_path/vivado_lib_dir/axi_ahblite_bridge_v3_0_15 axi_amm_bridge_v1_0_8 = dir_path/vivado_lib_dir/axi_amm_bridge_v1_0_8 axi_chip2chip_v5_0_4 = dir_path/vivado_lib_dir/axi_chip2chip_v5_0_4 axi_infrastructure_v1_1_0 = dir_path/vivado_lib_dir/axi_infrastructure_v1_1_0 axi_jtag_v1_0_0 = dir_path/vivado_lib_dir/axi_jtag_v1_0_0 axi_lite_ipif_v3_0_4 = dir_path/vivado_lib_dir/axi_lite_ipif_v3_0_4 axi_pcie3_v3_0_8 = dir_path/vivado_lib_dir/axi_pcie3_v3_0_8 axi_perf_mon_v5_0_20 = dir_path/vivado_lib_dir/axi_perf_mon_v5_0_20 blk_mem_gen_v8_3_6 = dir_path/vivado_lib_dir/blk_mem_gen_v8_3_6 blk_mem_gen_v8_4_2 = dir_path/vivado_lib_dir/blk_mem_gen_v8_4_2 bsip_v1_1_0 = dir_path/vivado_lib_dir/bsip_v1_1_0 bs_mux_v1_0_0 = dir_path/vivado_lib_dir/bs_mux_v1_0_0 clk_piv_v1_0_2 = dir_path/vivado_lib_dir/clk_piv_v1_0_2 cmac_usplus_v2_4_4 = dir_path/vivado_lib_dir/cmac_usplus_v2_4_4 cmac_usplus_v2_5_0 = dir_path/vivado_lib_dir/cmac_usplus_v2_5_0 cmac_v2_3_4 = dir_path/vivado_lib_dir/cmac_v2_3_4 cmac_v2_4_0 = dir_path/vivado_lib_dir/cmac_v2_4_0 compact_gt_v1_0_4 = dir_path/vivado_lib_dir/compact_gt_v1_0_4 dist_mem_gen_v8_0_12 = dir_path/vivado_lib_dir/dist_mem_gen_v8_0_12 ecc_v2_0_12 = dir_path/vivado_lib_dir/ecc_v2_0_12 emc_common_v3_0_5 = dir_path/vivado_lib_dir/emc_common_v3_0_5 ethernet_10g_25g_v2_0_2 = dir_path/vivado_lib_dir/ethernet_10g_25g_v2_0_2

2.复制文件中所有库路径的映射内容(比如 secureip、unisim、unimacro等全系列库的路径配置)。

3.打开QuestaSim/ModelSim 安装根目录下的modelsim.ini文件,将复制的内容粘贴进去,保存并退出。核心库路径参考格式:

ini secureip = dir_path /vivado_lib_dir/secureip unisim = dir_path /vivado_lib_dir/unisim unimacro = dir_path /vivado_lib_dir/unimacro unifast = dir_path /vivado_lib_dir/unifast simprims_ver = dir_path /vivado_lib_dir/simprims_ver xpm = dir_path /vivado_lib_dir/xpm xilinx_vip = dir_path /vivado_lib_dir/xilinx_vip

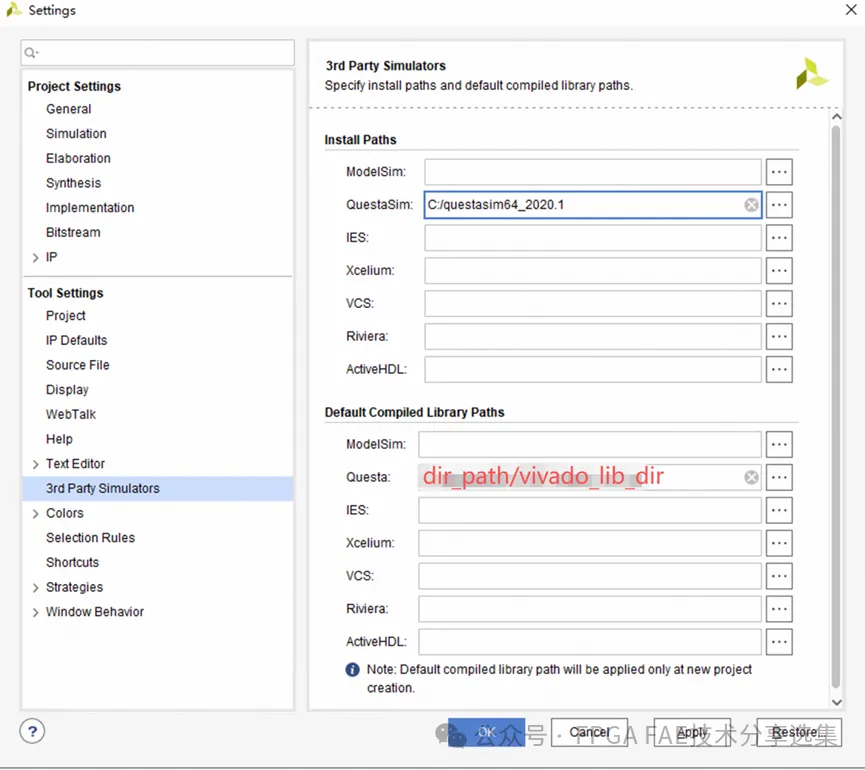

步骤 3:Vivado 中配置仿真器路径

完成库文件配置后,需要在Vivado 中指定第三方仿真器的安装路径,让两个软件实现联动。

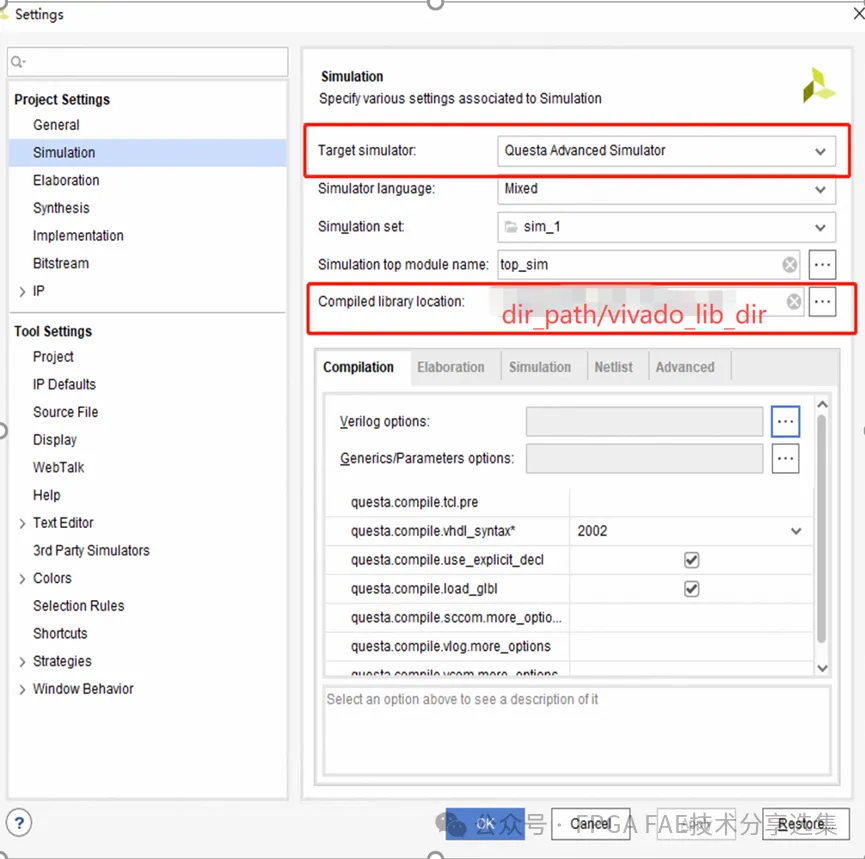

1.打开 Vivado,点击顶部菜单栏Tools → Settings,打开设置窗口。

2.在左侧菜单栏找到 Simulation,切换到第三方仿真器配置界面。

3.在 Install Paths 栏目下,找到对应的 QuestaSim/ModelSim 选项,填写软件安装根路径,比如C:/questasim64_2020.1。

4.在 Default Compiled Library Paths 栏目下,填写步骤 1 中预编译的库文件夹路径,比如dir_path /vivado_lib_dir。

5. 点击 Apply → OK,保存配置并退出。

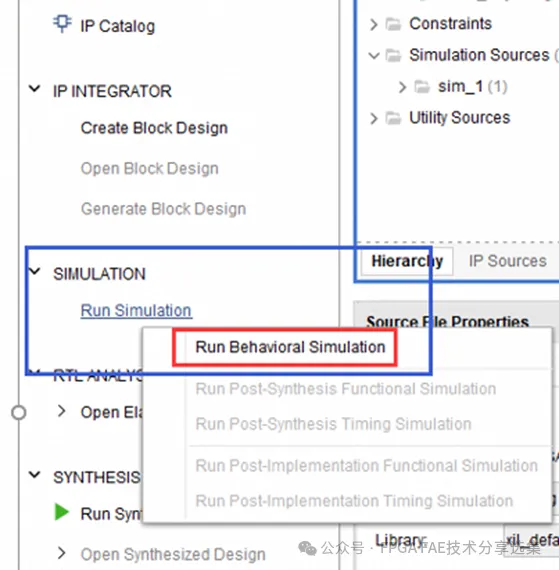

步骤 4:启动仿真验证配置

到这里,基础配置就全部完成了,我们可以直接在 Vivado 中启动仿真,验证配置是否生效。

1.打开你的 FPGA 工程,确保已经编写好 Testbench 仿真文件,并添加到工程的 Simulation Sources 中。

2.点击左侧 Flow Navigator 中的 Run Simulation,根据需求选择仿真类型:

Run Behavioral Simulation:行为级仿真(最常用)

Run Post-Synthesis Functional Simulation:综合后功能仿真

Run Post-Implementation Timing Simulation:实现后时序仿真

3.点击对应选项后,软件会自动调用 QuestaSim/ModelSim 仿真器,启动仿真界面,正常加载工程、IP 核和 Testbench,即代表配置全部成功。

三、避坑指南:Windows系统 Vivado 调用仿真器卡死解决方案

很多 Windows 用户会遇到一个经典问题:Vivado 点击启动仿真后,软件直接卡死,无法弹出仿真器界面,而 Linux 系统却能正常使用。这里给大家提供一个稳定可用的解决办法,通过自定义 do 脚本实现仿真启动。

核心原理:

Vivado 自动生成的仿真脚本,在 Windows 系统下存在调用兼容性问题,我们将自动生成的编译、 elaboration 脚本合并重构,编写自定义的 run.do 脚本,直接在仿真器中执行,规避软件联动的卡死问题。

具体操作步骤

1.先在 Vivado 中点击一次 Run Simulation,等待工程生成仿真文件,无需等待软件响应,直接关闭卡死的Vivado。

2.打开工程目录,找到仿真生成的文件夹:工程目录/工程名.sim/sim_1/behav/questa,在这个文件夹中,能看到 Vivado 自动生成的top_sim_compile.do和top_sim_elaborate.do两个核心脚本。(工程仿真所需要的coe、mif及glbl.v文件会自动拷贝到当前文件夹)

3.新建一个文本文档,重命名为run.do,作为我们的自定义仿真脚本,按以下规则编辑内容:

脚本首行添加vlib questasim_lib,创建仿真工作库;

复制top_sim_compile.do中所有的文件编译命令(vlog/vcom 相关指令),粘贴到 run.do 中;

复制top_sim_elaborate.do中的核心内容,做两处关键修改:

(1)删除-o top_sim_opt参数,将开头的c:\\questasim64_2020.1\\win64\\vopt -64 +acc=npr替换为vsim -voptargs="+acc",适配 QuestaSim 环境;

(2)删除脚本末尾的quit -force命令,避免仿真完成后自动关闭仿真器,无法查看波形。

4.保存修改好的run.do文件,将其放在questa文件夹根目录下。

5.双击打开QuestaSim/ModelSim 软件,将路径切换到questa文件夹,在 Transcript 控制台输入tcl命令:do run.do;

6.回车执行后,脚本会自动完成工程编译、仿真启动,全程无卡死,后续波形查看、仿真调试操作,和 QuestaSim 原生操作完全一致,后续更新IP增加仿真激励只需维护run.do脚本,无需再打开vivado即可仿真。

写在最后:

FPGA 仿真环境的搭建,看似是基础操作,实则藏着很多版本兼容、路径配置、系统适配的细节坑点。很多时候开发进度被耽误,不是因为代码写不出来,而是好用的环境搭不起来。

如果您在仿真环境搭建方面有问题,欢迎联系: