波束成形概述:从4G到5G的挑战

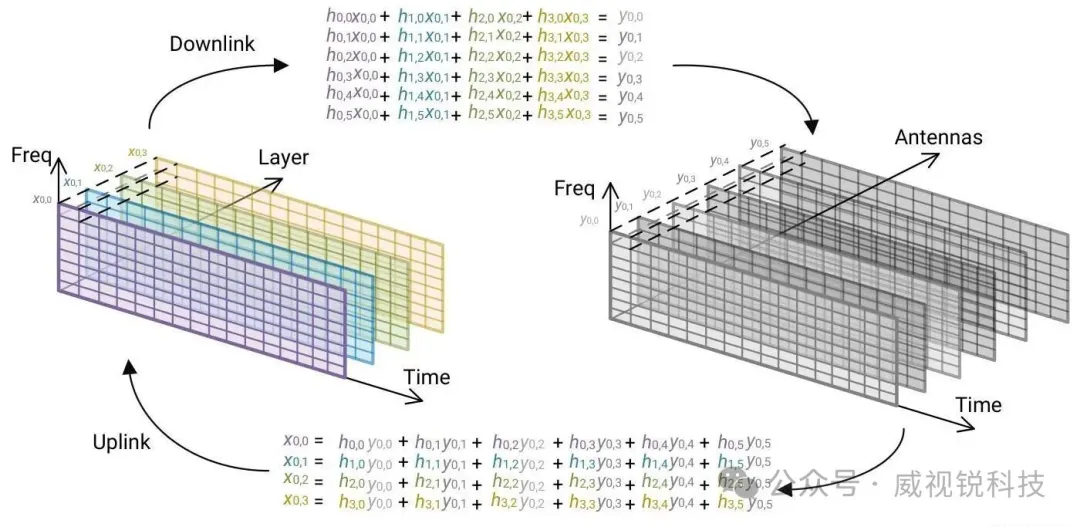

MIMO与波束成形核心机制

核心作用:对多天线信号加权处理,实现信号定向传输,大幅提升频谱效率与信号质量。

关键位置:位于基站基带单元(BBU)与射频单元(RRU)之间,连接数字与射频信号。

5G NR 带来的计算复杂度挑战

320倍 相比4G LTE,波束成形复杂度激增。

原因:天线数(8→64) | 数据流(2→16) | 带宽(20M→100M)

AIE架构解析:AI引擎的核心优势

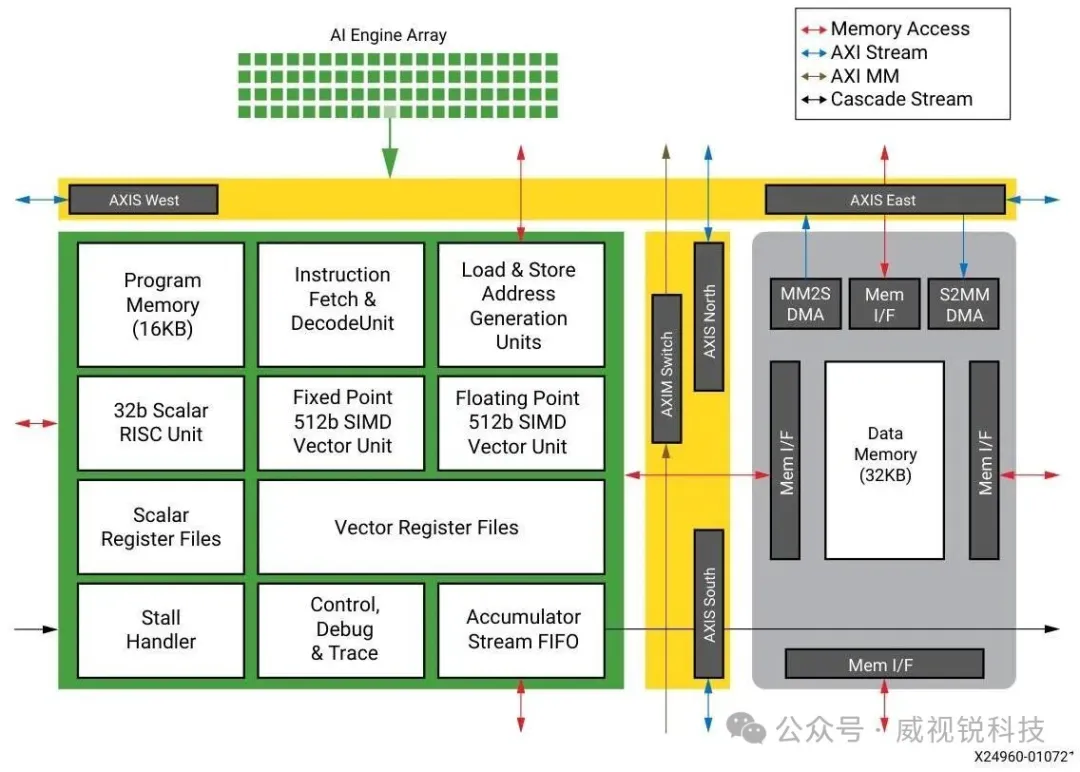

AIE Tile 核心架构示意图

AIE 架构组成

AI Engine核心:集成标量与矢量处理器,单周期支持32个16-bit MAC运算。

本地数据存储器:32KB高速存储,减少片外依赖,显著降低数据延迟。

DMA引擎:双DMA引擎实现计算与数据传输并行,提升吞吐效率。

核心技术优势

极致计算密度:单核心提供8G CMAC/s算力,性能相当于32个传统DSP。

灵活可编程性:支持C语言开发,大幅缩短开发周期,易于维护升级。

硬件可扩展性:阵列结构设计,可根据场景灵活扩展算力规模。

AIE架构通过“计算+存储+传输”的深度融合,重新定义了边缘侧与云端的AI计算能效比标准。

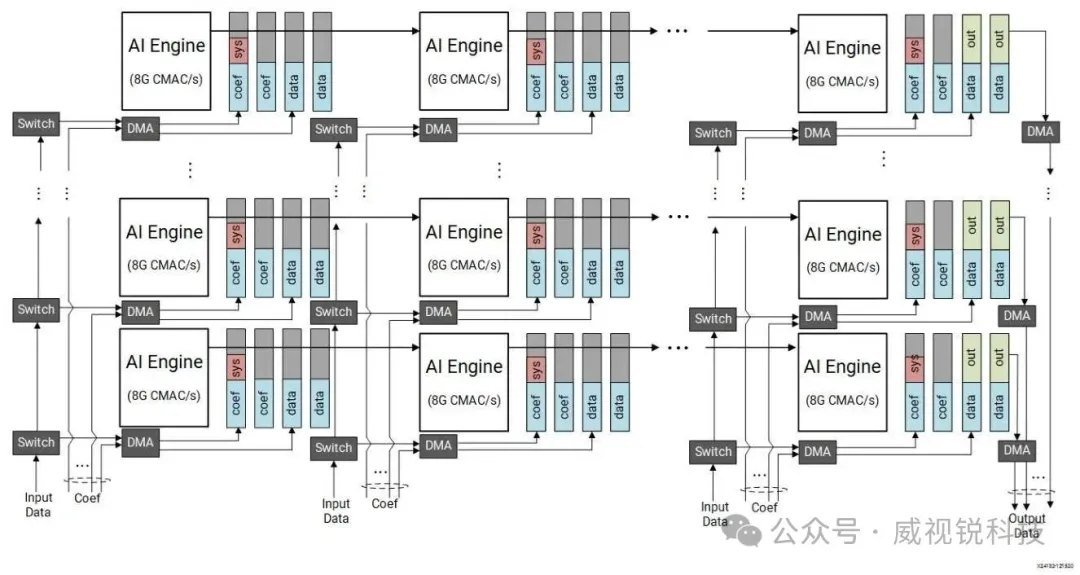

实现方案:矩阵乘法的高效映射

大规模矩阵运算的分解

核心思想:将大规模波束成形矩阵(NxM * MxL)分解为多个(u-by-v) × (v-by-L)的子矩阵运算。

并行处理:每个子矩阵由独立AI Engine处理,实现高度并行化计算。

高效的数据流与流水线

级联总线:AI Engine间通过级联总线连接,实现部分结果的高效累加与传输。

数据流水线:DMA负责数据搬运与计算过程并行,最大化硬件资源利用率。

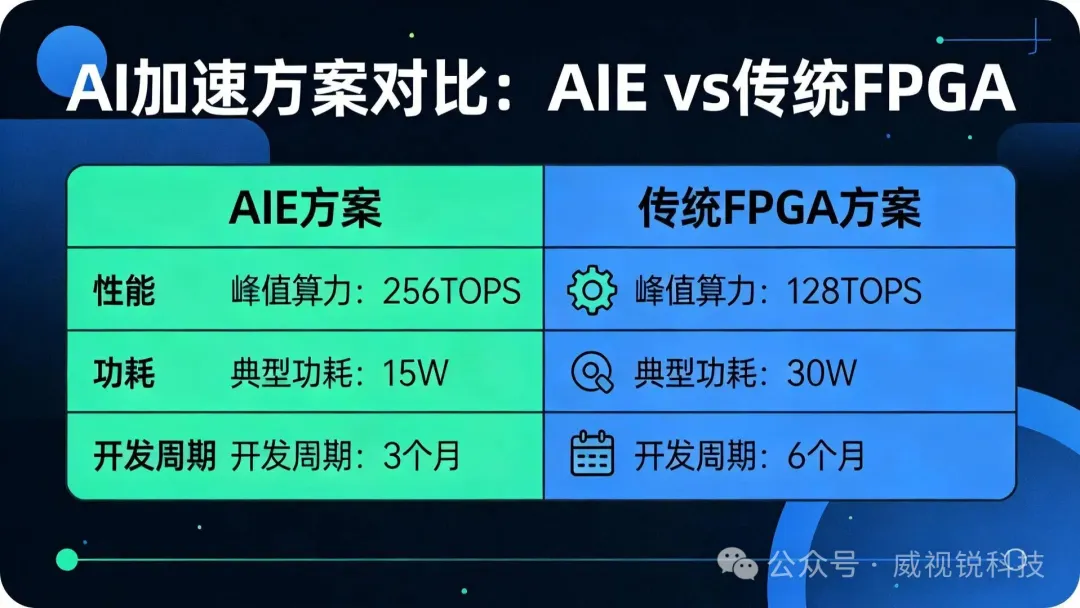

性能优势:超越传统方案的能效比

图表直观展示了AIE方案在算力密度、功耗控制及开发周期上相较于传统FPGA方案的全面代际优势。

计算效率跃升

单个AIE核心性能等效于32个DSP58,MAC运算效率突破80%,算力密度大幅领先。

开发周期缩短

基于标准C语言编程,无需手动布局布线,开发周期从数月缩短至数天,彻底解决时序收敛难题。

极致能效表现

在提供同等算力的前提下,AIE方案功耗显著低于传统FPGA,实现更高的性能/瓦特比,降低运营成本。

实现架构

系统配置

支持100MHz带宽,配置64根天线,可处理32层数据流,满足高阶MIMO需求。

AIE架构配置

采用(u=8, v=8, L=12)子矩阵划分策略,仅需32个AI Engine即可高效驱动。

性能表现

实现204.8 GCMAC/s算力,MAC利用率高达80%,完美满足5G实时处理低时延要求。

案例研究:LTE系统的灵活实现 窄带系统的优化策略

参数调整:在LTE 20MHz等窄带系统中,通过增大子矩阵尺寸(如u=v=16)来显著减少所需的AI Engine数量,提升效率。

共享设计:优化后的参数配置支持上下行波束成形共享同一套AI Engine内核,极大降低硬件资源消耗。

灵活性的体现

AIE的软件可编程性赋予了系统极高的弹性。系统可根据不同的带宽需求和配置场景,动态灵活地调整参数,从而实现资源的最优利用,适应多变的通信环境。

核心价值:通过算法优化与硬件共享,实现从资源消耗到资源高效利用的跨越。

未来展望:面向6G的应用场景

更大规模的MIMO

支持数百甚至上千根天线,通过波束赋形与空间复用技术,实现极致的频谱效率与数据吞吐能力。

通感一体化 (ISAC)

基站融合通信与雷达感知能力,实现高精度环境感知与定位,赋能自动驾驶、无人机等新兴智能应用。

AI原生优化

利用AI处理能力实现智能波束管理、信道预测与干扰抑制,构建自感知、自优化的下一代智能通信网络。

总结

AIE以其卓越的计算密度、能效比和灵活性,成为实现5G及未来6G波束成形的理想平台,为无线通信的发展提供了强大的算力支持。

文章来源:威视锐科技